- •Analysis and Application of Analog Electronic Circuits to Biomedical Instrumentation

- •Dedication

- •Preface

- •Reader Background

- •Rationale

- •Description of the Chapters

- •Features

- •The Author

- •Table of Contents

- •1.1 Introduction

- •1.2 Sources of Endogenous Bioelectric Signals

- •1.3 Nerve Action Potentials

- •1.4 Muscle Action Potentials

- •1.4.1 Introduction

- •1.4.2 The Origin of EMGs

- •1.5 The Electrocardiogram

- •1.5.1 Introduction

- •1.6 Other Biopotentials

- •1.6.1 Introduction

- •1.6.2 EEGs

- •1.6.3 Other Body Surface Potentials

- •1.7 Discussion

- •1.8 Electrical Properties of Bioelectrodes

- •1.9 Exogenous Bioelectric Signals

- •1.10 Chapter Summary

- •2.1 Introduction

- •2.2.1 Introduction

- •2.2.4 Schottky Diodes

- •2.3.1 Introduction

- •2.4.1 Introduction

- •2.5.1 Introduction

- •2.5.5 Broadbanding Strategies

- •2.6 Photons, Photodiodes, Photoconductors, LEDs, and Laser Diodes

- •2.6.1 Introduction

- •2.6.2 PIN Photodiodes

- •2.6.3 Avalanche Photodiodes

- •2.6.4 Signal Conditioning Circuits for Photodiodes

- •2.6.5 Photoconductors

- •2.6.6 LEDs

- •2.6.7 Laser Diodes

- •2.7 Chapter Summary

- •Home Problems

- •3.1 Introduction

- •3.2 DA Circuit Architecture

- •3.4 CM and DM Gain of Simple DA Stages at High Frequencies

- •3.4.1 Introduction

- •3.5 Input Resistance of Simple Transistor DAs

- •3.7 How Op Amps Can Be Used To Make DAs for Medical Applications

- •3.7.1 Introduction

- •3.8 Chapter Summary

- •Home Problems

- •4.1 Introduction

- •4.3 Some Effects of Negative Voltage Feedback

- •4.3.1 Reduction of Output Resistance

- •4.3.2 Reduction of Total Harmonic Distortion

- •4.3.4 Decrease in Gain Sensitivity

- •4.4 Effects of Negative Current Feedback

- •4.5 Positive Voltage Feedback

- •4.5.1 Introduction

- •4.6 Chapter Summary

- •Home Problems

- •5.1 Introduction

- •5.2.1 Introduction

- •5.2.2 Bode Plots

- •5.5.1 Introduction

- •5.5.3 The Wien Bridge Oscillator

- •5.6 Chapter Summary

- •Home Problems

- •6.1 Ideal Op Amps

- •6.1.1 Introduction

- •6.1.2 Properties of Ideal OP Amps

- •6.1.3 Some Examples of OP Amp Circuits Analyzed Using IOAs

- •6.2 Practical Op Amps

- •6.2.1 Introduction

- •6.2.2 Functional Categories of Real Op Amps

- •6.3.1 The GBWP of an Inverting Summer

- •6.4.3 Limitations of CFOAs

- •6.5 Voltage Comparators

- •6.5.1 Introduction

- •6.5.2. Applications of Voltage Comparators

- •6.5.3 Discussion

- •6.6 Some Applications of Op Amps in Biomedicine

- •6.6.1 Introduction

- •6.6.2 Analog Integrators and Differentiators

- •6.7 Chapter Summary

- •Home Problems

- •7.1 Introduction

- •7.2 Types of Analog Active Filters

- •7.2.1 Introduction

- •7.2.3 Biquad Active Filters

- •7.2.4 Generalized Impedance Converter AFs

- •7.3 Electronically Tunable AFs

- •7.3.1 Introduction

- •7.3.3 Use of Digitally Controlled Potentiometers To Tune a Sallen and Key LPF

- •7.5 Chapter Summary

- •7.5.1 Active Filters

- •7.5.2 Choice of AF Components

- •Home Problems

- •8.1 Introduction

- •8.2 Instrumentation Amps

- •8.3 Medical Isolation Amps

- •8.3.1 Introduction

- •8.3.3 A Prototype Magnetic IsoA

- •8.4.1 Introduction

- •8.6 Chapter Summary

- •9.1 Introduction

- •9.2 Descriptors of Random Noise in Biomedical Measurement Systems

- •9.2.1 Introduction

- •9.2.2 The Probability Density Function

- •9.2.3 The Power Density Spectrum

- •9.2.4 Sources of Random Noise in Signal Conditioning Systems

- •9.2.4.1 Noise from Resistors

- •9.2.4.3 Noise in JFETs

- •9.2.4.4 Noise in BJTs

- •9.3 Propagation of Noise through LTI Filters

- •9.4.2 Spot Noise Factor and Figure

- •9.5.1 Introduction

- •9.6.1 Introduction

- •9.7 Effect of Feedback on Noise

- •9.7.1 Introduction

- •9.8.1 Introduction

- •9.8.2 Calculation of the Minimum Resolvable AC Input Voltage to a Noisy Op Amp

- •9.8.5.1 Introduction

- •9.8.5.2 Bridge Sensitivity Calculations

- •9.8.7.1 Introduction

- •9.8.7.2 Analysis of SNR Improvement by Averaging

- •9.8.7.3 Discussion

- •9.10.1 Introduction

- •9.11 Chapter Summary

- •Home Problems

- •10.1 Introduction

- •10.2 Aliasing and the Sampling Theorem

- •10.2.1 Introduction

- •10.2.2 The Sampling Theorem

- •10.3 Digital-to-Analog Converters (DACs)

- •10.3.1 Introduction

- •10.3.2 DAC Designs

- •10.3.3 Static and Dynamic Characteristics of DACs

- •10.4 Hold Circuits

- •10.5 Analog-to-Digital Converters (ADCs)

- •10.5.1 Introduction

- •10.5.2 The Tracking (Servo) ADC

- •10.5.3 The Successive Approximation ADC

- •10.5.4 Integrating Converters

- •10.5.5 Flash Converters

- •10.6 Quantization Noise

- •10.7 Chapter Summary

- •Home Problems

- •11.1 Introduction

- •11.2 Modulation of a Sinusoidal Carrier Viewed in the Frequency Domain

- •11.3 Implementation of AM

- •11.3.1 Introduction

- •11.3.2 Some Amplitude Modulation Circuits

- •11.4 Generation of Phase and Frequency Modulation

- •11.4.1 Introduction

- •11.4.3 Integral Pulse Frequency Modulation as a Means of Frequency Modulation

- •11.5 Demodulation of Modulated Sinusoidal Carriers

- •11.5.1 Introduction

- •11.5.2 Detection of AM

- •11.5.3 Detection of FM Signals

- •11.5.4 Demodulation of DSBSCM Signals

- •11.6 Modulation and Demodulation of Digital Carriers

- •11.6.1 Introduction

- •11.6.2 Delta Modulation

- •11.7 Chapter Summary

- •Home Problems

- •12.1 Introduction

- •12.2.1 Introduction

- •12.2.2 The Analog Multiplier/LPF PSR

- •12.2.3 The Switched Op Amp PSR

- •12.2.4 The Chopper PSR

- •12.2.5 The Balanced Diode Bridge PSR

- •12.3 Phase Detectors

- •12.3.1 Introduction

- •12.3.2 The Analog Multiplier Phase Detector

- •12.3.3 Digital Phase Detectors

- •12.4 Voltage and Current-Controlled Oscillators

- •12.4.1 Introduction

- •12.4.2 An Analog VCO

- •12.4.3 Switched Integrating Capacitor VCOs

- •12.4.6 Summary

- •12.5 Phase-Locked Loops

- •12.5.1 Introduction

- •12.5.2 PLL Components

- •12.5.3 PLL Applications in Biomedicine

- •12.5.4 Discussion

- •12.6 True RMS Converters

- •12.6.1 Introduction

- •12.6.2 True RMS Circuits

- •12.7 IC Thermometers

- •12.7.1 Introduction

- •12.7.2 IC Temperature Transducers

- •12.8 Instrumentation Systems

- •12.8.1 Introduction

- •12.8.5 Respiratory Acoustic Impedance Measurement System

- •12.9 Chapter Summary

- •References

Examples of Special Analog Circuits and Systems |

495 |

Examine the system design with practical numbers: let φm ∫ 10º; Ki = 1 and KP = 8.0E−6 sec/V; and 720/c = 2.40E−6. These numbers give a reasonable range sensitivity:

KR |

= |

720 |

= 3.0E |

−2 V m |

(12.48) |

||

c KP |

φmss |

||||||

|

|

|

|

|

|||

From Equation 12.47, the velocity sensitivity is also useful:

KS |

= 2.40E−6 |

|

1 |

= 3.0E |

−2 V m s |

(12.49) |

|

KP |

φmss Ki |

||||||

|

|

|

|

|

The VPC steady-state output frequency at a 1-m range is 4.17 MHz; when L = 100 m, it is 41.7 kHz.

12.4.6Summary

There are a variety of architectures for voltage-controlled oscillators, including “linear” VCOs using variable gain elements, switched integrating capacitor VCOs, and emitter-coupled, astable multivibrators. Versions of the latter architecture have been made to oscillate in the gigahertz. Another VHF–UHF VCO architecture (not shown here) makes use of the varactor diode (VD). The VD is a reverse-biased pn junction diode in which the diode depletion capacitance is controlled by the reverse-bias voltage. This voltage-variable capacitance can be used to tune oscillators such as the familiar Hartley design and to generate NBFM by adding the modulating signal to the reverse diode bias voltage. VCOs are used in all phase-lock loops and in FM communications applications, as well as in many instrumentation systems.

The voltage-to-period converter (VPC) is a VCO in which the output oscillation’s period is linearly proportional to the input voltage. The VPC is a useful circuit component in a closed-loop, constant-phase laser velocimeter and ranging system. The same closed-loop, constant-phase architecture can also be used with sound or ultrasound to measure object range and velocity simultaneously.

12.5 Phase-Locked Loops

12.5.1Introduction

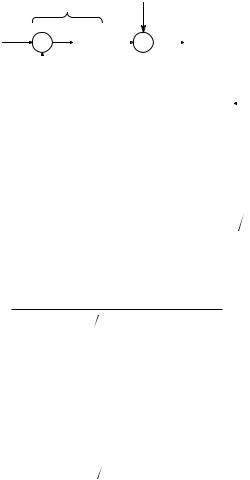

A phase-locked loop (PLL) (also called a phase-lock loop) is a closed-loop feedback system in which the phase of the PLL’s periodic output is made to follow the phase of a periodic input signal. The closed-loop PLL system’s

© 2004 by CRC Press LLC

496 |

|

Analysis and Application of Analog Electronic Circuits |

||||||

f1 |

|

Vφ |

Loop |

Vc |

|

N f1 |

||

PD |

|

|

|

VCO |

|

|

||

θ1 |

|

filter |

|

|

|

|

||

|

|

|

|

|

|

|

||

Vφ (θ1 − θo)

|

|

Freq. divider |

@ lock: |

|

|

fo |

= f1 |

÷ N |

θo |

|

|

|

|

|

A

Linearized PD

|

|

|

Loop filter |

VCO |

|

|

|

|

|

θ1 |

θe |

Vφ |

Vc |

θo, fo |

|

Kp |

|

F(s) |

Kv |

|

|

s |

||

|

|

|

|

|

|

− |

|

|

|

|

θo |

|

|

|

|

fo = f1 at lock |

|

B |

|

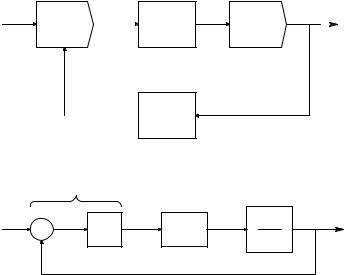

FIGURE 12.24

(A) Basic architecture of a phase-locked loop (PLL). (B) Systems block diagram of a PLL.

natural frequencies are, in general, several orders of magnitude lower than the frequency of the input signal. Phase-lock loops have many applications in communications, control systems, and instrumentation systems. They can be used to modulate and demodulate narrow-band FM (NBFM) signals; demodulate double-sideband/suppressed carrier (DSBSC) signals; demodulate AM signals; generate a frequency-independent phase shift; measure frequencies, including heart rate; synthesize signals used in digital communications systems; detect touch-tone frequencies and status signals used in telephony; control motor speed, etc.

The basic architecture of a PLL is shown in Figure 12.24(A). It includes a phase (difference) detector (PD), loop filter, VCO (VFC), and, sometimes, a frequency divider between the VCO and the PD. (Phase detectors were described in Section 12.3.) A phase detector returns an average voltage proportional to the phase difference between the input signal and the VCO output.

Analysis of PLL dynamics is done assuming lock, i.e., that the input and VCO frequencies are equal. When a PLL first acquires its input signal, f1 π fo and the loop must attain lock through a nonlinear process known as acquisition. The time required for acquisition is important in such PLL applications as telephone touch-tone decoding and the demodulation of FSK signals. Empirical formulas for acquisition times can be found in Northrop (1990) and Gardner (1979).

© 2004 by CRC Press LLC

Examples of Special Analog Circuits and Systems |

497 |

12.5.2PLL Components

As mentioned earlier, phase detectors such as those used in PLLs have already been considered in Section 12.3. Most IC PLLs use PDs in which the analog input signal is effectively multiplied by a ±1 square wave derived from the VCO. This type of PD is a quadrature detector; the zero phase error condition requires that θ1 − θo = π/2. Analog multiplier and exclusive OR PDs are also quadrature detectors. Only the RSFF PD and the MC 4044 PD are in-phase detectors.

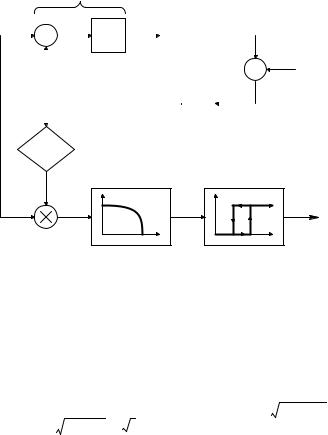

All PDs produce an analog output whose average value, Vφ, is proportional to sin(θe) or to θe. When θe < 15º, sin(θe) can be replaced with θe in radians. Thus, for small-signal errors at lock, the PLL can be modeled by the block diagram in Figure 12.24(B). The VCO is modeled in the frequency domain by Kv s because ωo = Vc Kv r/s and its output phase is, in general, the integral of its output frequency, i.e., θo = ωo dt. The PLL’s dynamics in response to changes in θ1 are determined in part by its closed-loop poles, which can be found from its linear loop gain using root-locus techniques. The PLL’s loop gain is generally:

AL (s) = |

Kp |

F(s)Kv |

(12.50) |

|

s |

||

|

|

|

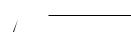

If F(s) = Kf (s + a)/s, then the loop gain function has a zero at s = −a, and two poles at the origin. Its root-locus is the well-known circle, shown in Figure 12.25. Effective design of this PLL wants the closed-loop poles at s = −a ± ja. This gives a damping factor of ξ = 0.707 and an undamped natural frequency of ωn = a2. The scalar gain product, Kp Kf Kv, is adjusted to obtain these closed-loop parameters. It can be shown that Kp Kf Kv = 2a will put the closed-loop poles at s = −a ± ja (Northrop, 1990).

The PLL’s loop filter is generally low-pass and can be of the form F(s) = Kf (s/b + 1), Kf (s + a)/s, Kf (s/a + 1)/(s/b + 1), etc. The loop filter is generally chosen to give the PLL the desired dynamic response in tracking changes in θ1. The PLL’s VCO can have a digital (TTL) or sinusoidal output. The VCO used on IC PLLs often uses the voltage-controlled, emitter-coupled astable multivibrator architecture (see above).

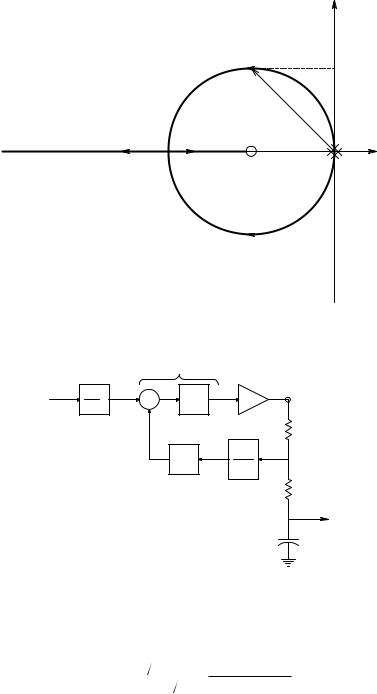

12.5.3PLL Applications in Biomedicine

One application of a PLL is its use to measure heart rate. Figure 12.26 illustrates the block diagram of a 4046 CMOS PLL used as a cardiotachometer (Northrop, 1990). The loop filter’s transfer function is found from the voltagedivider relation:

Vc |

= |

|

R2 + 1 sC |

= |

sCR2 + 1 |

(12.51) |

||

|

|

|

|

sC(R |

+ R )+ 1 |

|||

V |

R |

+ R |

+ 1 sC |

|||||

φ |

1 |

2 |

|

1 |

2 |

|

||

© 2004 by CRC Press LLC

498 |

Analysis and Application of Analog Electronic Circuits |

jω

s-plane

ja

ωn = a√2

−2a |

σ |

−a

FIGURE 12.25

Root-locus diagram of a PLL having a loop filter of the form, F(s) = Kf (s + a)/s.

|

|

|

PD |

|

|

|

f1 |

2π |

θi |

Kp |

×1 |

Vφ |

Loop |

|

|

|

||||

(beat/s) s |

(rad) + |

|

filter |

|||

− |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

VCO |

|

R1 |

|

|

|

|

|

|

|

|

|

|

θo |

Kv |

|

|

|

|

|

÷ N |

|

Vc |

|

|

|

|

s |

|

||

|

|

|

ωo |

|

|

|

|

|

|

|

Nωo |

|

|

|

|

|

|

|

|

R2 |

Vo

C

FIGURE 12.26

Block diagram of a PLL used as a heart rate monitor. Vo is proportional to the average heart rate.

Similarly, the output transfer function is:

Vo |

|

1 sC |

1 |

|

|

|

= |

|

= |

sC(R1 + R2 )+ 1 |

(12.52) |

Vφ |

R1 + R2 + 1 sC |

||||

and the PLL’s loop gain is:

© 2004 by CRC Press LLC

Examples of Special Analog Circuits and Systems |

|

|

|

|

499 |

||||||||||

|

|

|

PD |

|

|

|

Vp |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

Loop filter |

|

|

|||

θ1 |

|

|

|

|

|

Vφ |

+ |

|

|

|

|

Vc |

|||

+ |

|

|

|

Kp |

+ |

|

Kf (s + a) |

||||||||

|

|

|

|

|

|

|

|

|

|

|

s |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

− |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCO |

|

|

|

|

|

|

θo |

|

|

|

|

|

|

|

Kv |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

s |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FIGURE 12.27

Block diagram of a PLL used to generate a frequency-independent phase shift. (θi − θo) Vp.

|

K |

p |

K |

v ( |

sCR + 1 |

|

|

K |

p |

K |

CR |

( |

s + 1 |

CR |

|

|||

A (s) = − |

|

|

2 |

) |

|

= − |

|

|

v |

2 |

|

2 ) |

(12.53) |

|||||

N s[sC(R1 + R2 )+ |

1] |

N C(R1 + R2 )s[s + 1 C(R1 + R2 )] |

||||||||||||||||

L |

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

The PLL’s transfer function is thus:

V |

(2π s)Kp |

|||

o |

= |

[1− AL (s)][s + 1 C(R1 + R2 )]C(R1 + R2 ) |

|

|

f1 |

||||

|

|

(12.54) |

||

= |

2πN Kv |

|

||

s2 NC(R1 + R2 ) KpKv + s[N + KpKvCR2 ] KpKv + 1 |

||||

|

|

|||

The denominator of the preceding equation is of the standard quadratic form: s2 ωn2 + s 2ξ ωn + 1. Thus:

ωn |

= |

KpKv |

|

ξ = |

N + KpKvR2C |

||

|

|

r s and |

|

(12.55) |

|||

NC(R1 |

+ R2 ) |

|

|||||

|

|

|

|

2 NC(R1 + R2 )KpKv |

|||

Examine system ωn, ξ, and dc gain given the typical circuit parameters: Kp = 8.33; Kv = 3.14; N = 4; C = 1.E−5; R1 = 62k; and R2 = 150k. These values yield: ωn = 1.76 r/s; ξ = 1.45 (overdamped); and dc gain Vo/f1 = 8.00 volts/beat/sec = 0.133 V/beat/min. Note that ωn and the damping ξ are measures of the PLL’s response dynamics to changes in the heart rate, f1 beats/sec.

In the second example of PLL applications, Figure 12.27 illustrates the block diagram of a PLL used to generate a frequency-independent phase shift between the input signal and the VCO output. This application is important in maximizing the output of a phase-sensitive rectifier or lock-in amplifier. The PLL’s loop gain is:

A |

(s) = − |

KpKf Kv (s + a) |

(12.56) |

|

s2 |

||||

L |

|

|

© 2004 by CRC Press LLC

500 |

|

|

|

Analysis and Application of Analog Electronic Circuits |

|||||||||

|

|

|

|

PD |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

F(s) |

|

|

||

|

x1 θ1, ω1 |

|

Kp |

Vφ |

|

|

1/τ |

|

Vc |

||||

|

|

|

|

|

|

|

|

|

|

||||

|

(sin) |

|

|

|

s + 1/τ |

|

|

||||||

|

|

|

|

|

|

|

|||||||

|

|

|

− |

|

|

|

|

|

|

|

|

|

b/Kv |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

VCO |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

θo, ωo |

|

|

|

Kv |

|

|

|

|

|

x2 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

(cos) |

|

|

|

s |

ωo = Kv Vc + b |

|||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Phase |

|

|

|

|

|

b = 2π(440) r/s |

|||

|

|

−90o |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

shifter |

|

|

|

|

|

|

|

||

x3 |

LPF |

|

|

Comp. |

|

|

|

|

|

|

1 |

x5 |

1 |

x6 = 0,1 |

|

x4 |

|||

|

|

f |

|

x5 |

|

0 |

|

0 |

|

AM |

|

|

||

|

|

|

|

FIGURE 12.28

Block diagram of a (tuned or frequency-selective) audio tone decoder PLL.

Taking the reference phase input, θ1 = 0, the transfer function between θo and Vp can be written:

θ |

o |

= |

|

Kf Kv (s + a) |

|

|

|

(12.57) |

||||

|

|

|

+ s K |

K |

K |

|

+ a K |

K |

K |

|

||

V s2 |

v |

v |

||||||||||

|

p |

|

|

p |

f |

|

p |

f |

|

|||

The undamped natural frequency of this PLL is ωn = aKpKf Kv r/s; its damping factor is ξ = KpKf Kv (2 a). These parameters relate to the system’s response to changes in the phase-shifting voltage, Vp, and have nothing to do with the input carrier frequency, ω1. The steady-state phase shift at lock

is simply θoss = Vp /Kp.

A third example of PLL applications examines a tone decoder, that is, a PLL system that outputs a logic HI when a sinusoidal signal is present at its input that has a frequency, f1, within some ±Δfc. Note that f1/ fc defines a capture “Q” for the tone decoder. Figure 12.28 illustrates the block diagram of a tone decoder PLL. Note that this system uses two phase detectors of

the quadrature (multiplicative) type. In the absence of a sinusoidal input signal, x1, Vc 0 and the VCO output frequency is by design ωo = b = 2π(440) r/s. Also, x6 = LO. The PLL acquires lock if the input sinusoid, x1 = A sin(ω1 t),

lies within the capture range of ±Δωc around ω1. Once the loop acquires lock, x2 = B cos(ω1 t), x3 = B sin(ω1 t), and x4 = x3 x1 = (AB/2)[cos(0) − cos(2ω1 t)].

After the LPF, x5 = AB/2 and x6 = 1 (HI). It can be shown (Grebene, 1971) that lock occurs when the input frequency ω1 lies in the capture range, given by:

ωc = 2π fc ∫ KT |

|

F(j ωc ) |

|

, |

(12.58) |

|

|

© 2004 by CRC Press LLC

Examples of Special Analog Circuits and Systems |

501 |

|

|

jω |

|

Incr. KpKv |

|

s-plane |

|

|

|

s* |

j /2τ |

|

_ |

|

|

|

|

|

ωn =√2/2τ |

|

|

|

σ |

−1/τ |

−1/2τ |

|

|

|

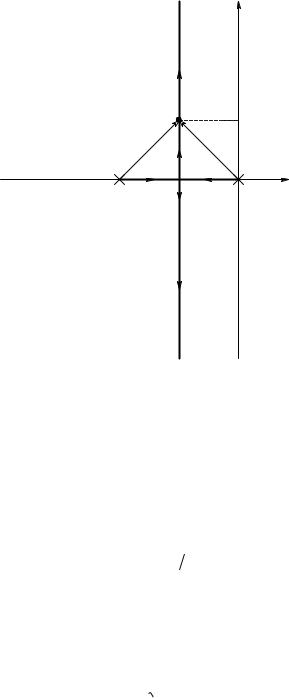

FIGURE 12.29

Root locus diagram for the PLL tone decoder.

where F(jΔωc) is the loop filter’s gain magnitude at ω = Δωc r/s, F(s) = (1/τ)/(s + 1/τ), and KT ∫ Kp Kv F(0). The lock range of input frequency over which the PLL will maintain lock is given by ΔωL = KT > Δωc. Thus, the tone decoder PLL behaves like a nonlinear tuned filter.

In order to design the system to respond to A440 to within ±1%, the PLL must acquire f1 = 440 ± 4.4 Hz. Thus, fc = 8.8 Hz. It is also necessary that

the loop damping factor be ξ = 0.707. The PLL’s loop gain is simply:

AL |

(s) = − |

KpKv |

τ |

(12.59) |

||

s(s |

+ 1 |

τ) |

||||

|

|

|

||||

From AL(s), using the root-locus technique, one can find the value of the gain product KpKv to put the PLL’s closed loop poles at s* = −1/2τ ± j 2τ. (See Figure 12.29.) The RL magnitude criterion indicates:

KpKv  τ = [ 2

τ = [ 2 (2τ)]2

(2τ)]2

¬

© 2004 by CRC Press LLC