- •Analysis and Application of Analog Electronic Circuits to Biomedical Instrumentation

- •Dedication

- •Preface

- •Reader Background

- •Rationale

- •Description of the Chapters

- •Features

- •The Author

- •Table of Contents

- •1.1 Introduction

- •1.2 Sources of Endogenous Bioelectric Signals

- •1.3 Nerve Action Potentials

- •1.4 Muscle Action Potentials

- •1.4.1 Introduction

- •1.4.2 The Origin of EMGs

- •1.5 The Electrocardiogram

- •1.5.1 Introduction

- •1.6 Other Biopotentials

- •1.6.1 Introduction

- •1.6.2 EEGs

- •1.6.3 Other Body Surface Potentials

- •1.7 Discussion

- •1.8 Electrical Properties of Bioelectrodes

- •1.9 Exogenous Bioelectric Signals

- •1.10 Chapter Summary

- •2.1 Introduction

- •2.2.1 Introduction

- •2.2.4 Schottky Diodes

- •2.3.1 Introduction

- •2.4.1 Introduction

- •2.5.1 Introduction

- •2.5.5 Broadbanding Strategies

- •2.6 Photons, Photodiodes, Photoconductors, LEDs, and Laser Diodes

- •2.6.1 Introduction

- •2.6.2 PIN Photodiodes

- •2.6.3 Avalanche Photodiodes

- •2.6.4 Signal Conditioning Circuits for Photodiodes

- •2.6.5 Photoconductors

- •2.6.6 LEDs

- •2.6.7 Laser Diodes

- •2.7 Chapter Summary

- •Home Problems

- •3.1 Introduction

- •3.2 DA Circuit Architecture

- •3.4 CM and DM Gain of Simple DA Stages at High Frequencies

- •3.4.1 Introduction

- •3.5 Input Resistance of Simple Transistor DAs

- •3.7 How Op Amps Can Be Used To Make DAs for Medical Applications

- •3.7.1 Introduction

- •3.8 Chapter Summary

- •Home Problems

- •4.1 Introduction

- •4.3 Some Effects of Negative Voltage Feedback

- •4.3.1 Reduction of Output Resistance

- •4.3.2 Reduction of Total Harmonic Distortion

- •4.3.4 Decrease in Gain Sensitivity

- •4.4 Effects of Negative Current Feedback

- •4.5 Positive Voltage Feedback

- •4.5.1 Introduction

- •4.6 Chapter Summary

- •Home Problems

- •5.1 Introduction

- •5.2.1 Introduction

- •5.2.2 Bode Plots

- •5.5.1 Introduction

- •5.5.3 The Wien Bridge Oscillator

- •5.6 Chapter Summary

- •Home Problems

- •6.1 Ideal Op Amps

- •6.1.1 Introduction

- •6.1.2 Properties of Ideal OP Amps

- •6.1.3 Some Examples of OP Amp Circuits Analyzed Using IOAs

- •6.2 Practical Op Amps

- •6.2.1 Introduction

- •6.2.2 Functional Categories of Real Op Amps

- •6.3.1 The GBWP of an Inverting Summer

- •6.4.3 Limitations of CFOAs

- •6.5 Voltage Comparators

- •6.5.1 Introduction

- •6.5.2. Applications of Voltage Comparators

- •6.5.3 Discussion

- •6.6 Some Applications of Op Amps in Biomedicine

- •6.6.1 Introduction

- •6.6.2 Analog Integrators and Differentiators

- •6.7 Chapter Summary

- •Home Problems

- •7.1 Introduction

- •7.2 Types of Analog Active Filters

- •7.2.1 Introduction

- •7.2.3 Biquad Active Filters

- •7.2.4 Generalized Impedance Converter AFs

- •7.3 Electronically Tunable AFs

- •7.3.1 Introduction

- •7.3.3 Use of Digitally Controlled Potentiometers To Tune a Sallen and Key LPF

- •7.5 Chapter Summary

- •7.5.1 Active Filters

- •7.5.2 Choice of AF Components

- •Home Problems

- •8.1 Introduction

- •8.2 Instrumentation Amps

- •8.3 Medical Isolation Amps

- •8.3.1 Introduction

- •8.3.3 A Prototype Magnetic IsoA

- •8.4.1 Introduction

- •8.6 Chapter Summary

- •9.1 Introduction

- •9.2 Descriptors of Random Noise in Biomedical Measurement Systems

- •9.2.1 Introduction

- •9.2.2 The Probability Density Function

- •9.2.3 The Power Density Spectrum

- •9.2.4 Sources of Random Noise in Signal Conditioning Systems

- •9.2.4.1 Noise from Resistors

- •9.2.4.3 Noise in JFETs

- •9.2.4.4 Noise in BJTs

- •9.3 Propagation of Noise through LTI Filters

- •9.4.2 Spot Noise Factor and Figure

- •9.5.1 Introduction

- •9.6.1 Introduction

- •9.7 Effect of Feedback on Noise

- •9.7.1 Introduction

- •9.8.1 Introduction

- •9.8.2 Calculation of the Minimum Resolvable AC Input Voltage to a Noisy Op Amp

- •9.8.5.1 Introduction

- •9.8.5.2 Bridge Sensitivity Calculations

- •9.8.7.1 Introduction

- •9.8.7.2 Analysis of SNR Improvement by Averaging

- •9.8.7.3 Discussion

- •9.10.1 Introduction

- •9.11 Chapter Summary

- •Home Problems

- •10.1 Introduction

- •10.2 Aliasing and the Sampling Theorem

- •10.2.1 Introduction

- •10.2.2 The Sampling Theorem

- •10.3 Digital-to-Analog Converters (DACs)

- •10.3.1 Introduction

- •10.3.2 DAC Designs

- •10.3.3 Static and Dynamic Characteristics of DACs

- •10.4 Hold Circuits

- •10.5 Analog-to-Digital Converters (ADCs)

- •10.5.1 Introduction

- •10.5.2 The Tracking (Servo) ADC

- •10.5.3 The Successive Approximation ADC

- •10.5.4 Integrating Converters

- •10.5.5 Flash Converters

- •10.6 Quantization Noise

- •10.7 Chapter Summary

- •Home Problems

- •11.1 Introduction

- •11.2 Modulation of a Sinusoidal Carrier Viewed in the Frequency Domain

- •11.3 Implementation of AM

- •11.3.1 Introduction

- •11.3.2 Some Amplitude Modulation Circuits

- •11.4 Generation of Phase and Frequency Modulation

- •11.4.1 Introduction

- •11.4.3 Integral Pulse Frequency Modulation as a Means of Frequency Modulation

- •11.5 Demodulation of Modulated Sinusoidal Carriers

- •11.5.1 Introduction

- •11.5.2 Detection of AM

- •11.5.3 Detection of FM Signals

- •11.5.4 Demodulation of DSBSCM Signals

- •11.6 Modulation and Demodulation of Digital Carriers

- •11.6.1 Introduction

- •11.6.2 Delta Modulation

- •11.7 Chapter Summary

- •Home Problems

- •12.1 Introduction

- •12.2.1 Introduction

- •12.2.2 The Analog Multiplier/LPF PSR

- •12.2.3 The Switched Op Amp PSR

- •12.2.4 The Chopper PSR

- •12.2.5 The Balanced Diode Bridge PSR

- •12.3 Phase Detectors

- •12.3.1 Introduction

- •12.3.2 The Analog Multiplier Phase Detector

- •12.3.3 Digital Phase Detectors

- •12.4 Voltage and Current-Controlled Oscillators

- •12.4.1 Introduction

- •12.4.2 An Analog VCO

- •12.4.3 Switched Integrating Capacitor VCOs

- •12.4.6 Summary

- •12.5 Phase-Locked Loops

- •12.5.1 Introduction

- •12.5.2 PLL Components

- •12.5.3 PLL Applications in Biomedicine

- •12.5.4 Discussion

- •12.6 True RMS Converters

- •12.6.1 Introduction

- •12.6.2 True RMS Circuits

- •12.7 IC Thermometers

- •12.7.1 Introduction

- •12.7.2 IC Temperature Transducers

- •12.8 Instrumentation Systems

- •12.8.1 Introduction

- •12.8.5 Respiratory Acoustic Impedance Measurement System

- •12.9 Chapter Summary

- •References

Noise and the Design of Low-Noise Amplifiers for Biomedical Applications |

353 |

|||||

and the output SNR is: |

|

|

|

|

|

|

|

|

|

|

|

|

|

SNRo = |

v 2 |

B |

|

|

(9.60) |

|

|

s |

|

|

|

||

4kTR + e 2 |

n2 + i 2 n2 R 2 |

|

||||

|

s na |

na |

s |

|

||

The SNRo clearly has a maximum with respect to the turns ratio, n. (It can be shown that F is minimum when n = no, so SNRo is maximum (Northrop, 1997). If the denominator of Equation 9.60 is differentiated with respect to n2 and set equal to zero, an optimum turns ratio, no, exists that will maximize SNRo. no is given by:

no = ena (inaRs ) |

(9.61) |

If the noiseless (ideal) transformer is given the turns ratio of no, then it is easy to show that the maximum output SNR is given by:

SNRO max |

= |

v 2 |

B |

(9.62) |

|

s |

|

||||

4kTRs + 2ena ina Rs |

|||||

|

|

|

|||

The general effect of transformer SNR maximization on the system’s noise figure contours is to shift the locus of minimum NFspot to a lower range of Rs; no obvious shift occurs along the fc axis. Also, the minimum NFspot is higher with a real transformer because a practical transformer is noisy, as discussed earlier. As a rule of thumb, using a transformer to improve output

SNR and reduce NFspot is justified if (ena2 + ina2 Rs2) > 20 ena ina Rs in the range of frequencies of interest (Northrop, 1990).

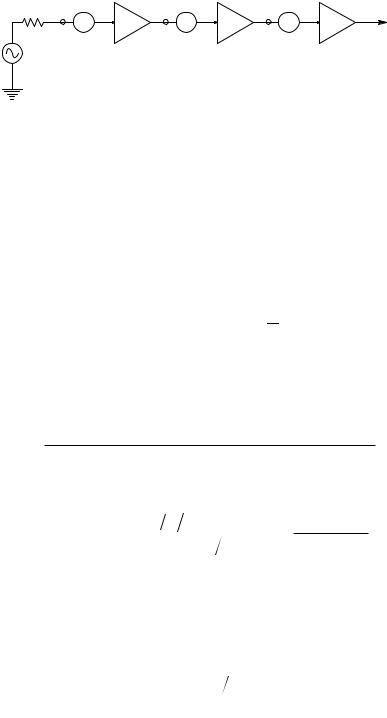

9.5Cascaded Noisy Amplifiers

9.5.1Introduction

To achieve the required high gain required for certain biomedical signal conditioning applications, it is often necessary to place several IC gain stages in series. A natural question to ask is whether all the component IC gain stages need to be low noise in the low-noise amplifier design. The good news is that as long as the headstage (input, or first stage) is low noise and has a gain magnitude of ≥10, the remaining gain stages do not need to be low noise in design. The headstage’s noise sets the noise performance of the complete signal conditioning amplifier.

© 2004 by CRC Press LLC

354 |

|

Analysis and Application of Analog Electronic Circuits |

|||

RS @ T |

ena1 |

ena2 |

ena3 |

|

|

V1 |

V2 |

V3 |

Vo |

||

|

|||||

|

|

KV1 |

KV2 |

KV3 |

|

+

vs

FIGURE 9.13

Three cascaded noisy amplifiers.

9.5.2The SNR of Cascaded Noisy Amplifiers

Figure 9.13 illustrates three cascaded amplifier stages. The amplifier’s overall

gain is KV = KV1 KV2 KV3. The first stage has a white, short-circuit voltage, root power spectrum of ena1 RMSV/ Hz and an input current noise root power spectrum of ina1 RMS V/ Hz. The other two stages have voltage noises

of ena2 and ena3, respectively, and zero current noises. (It can be assumed that the current noises are zero because the output resistance of the previous

stages is assumed to be very low, so that ina2 Ro1 ena2, and ina3 Ro2 ena3.) Assume a sinusoidal input signal, vs(t) = Vs sin(2πft); thus, the MS input

voltage is Vs2/2. The MS output voltage is simply vos2 = (Vs2/2)(KV1KV2KV3)2. The total MS noise output voltage is the sum of the MS noise components

from the noise sources: v |

2 |

= [e |

2 + i |

2iR 2](K |

V1 |

K |

V2 |

K |

V3 |

)2 + e |

2 |

(K |

V2 |

K |

V3 |

)2 + |

|||||||

|

|

|

|

|

|

on |

|

na1 |

na1 |

s |

|

|

|

|

na2 |

|

|

|

|||||

e |

2 |

(K |

)2. The output MS signal-to-noise ratio can now be examined for the |

||||||||||||||||||||

|

na3 |

V3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

three-stage amplifier: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

SNRo = |

|

|

|

(Vs2 2)(KV1KV 2KV 3 )2 |

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

{[ena21 + ina21 Rs2 ](KV1KV 2KV 3 )2 + ena22 (KV 2KV 3 )2 + ena23 (KV 3 )2}B |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

¬ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SNRo = |

|

|

(Vs2 2) B |

|

|

|

|

|

|

|

(Vs2 2) |

B |

|

|

|

|

|||||

|

|

|

|

[ena21 + ina21 Rs2 ] |

(9.63) |

||||||||||||||||||

|

|

[ena21 + ina21 Rs2 ]+ ena22 KV21 + ena23 |

(KV1KV 2 )2 |

||||||||||||||||||||

Thus, the SNRo of the three-stage cascaded amplifier is set by the headstage alone, as long as the headstage gain KV1 > 10.

What if the headstage is of necessity a source or emitter follower with near-unity gain? If the preceding equation is examined, it can be seen that it reduces to a lower value for KV1 1, e.g.,

SNRo |

(Vs |

2 2) B |

(9.64) |

[ena21 + ina21 Rs2 ]+ ena22 + ena23 (KV 2 )2 |

|||

© 2004 by CRC Press LLC

Noise and the Design of Low-Noise Amplifiers for Biomedical Applications |

355 |

Rs @ T |

ena |

|

Vi |

|

+ |

Vs |

ina |

|

Vo |

|

G |

Vs’ |

ina’ |

|

− |

|

Vi’ |

Rs’ @ T |

ena’ |

FIGURE 9.14

Equivalent input circuit for a noisy differential amplifier. In this model, both input transistors make noise.

Now the second stage’s voltage noise, ena2, becomes important and KV2 that should be >10; the first and the second stages must use low-noise amplifiers.

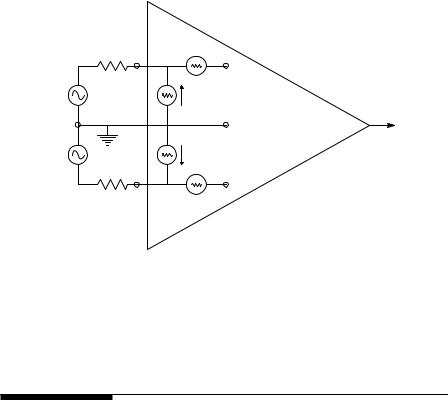

9.6Noise in Differential Amplifiers

9.6.1Introduction

As Chapter 3 discussed, the headstage of a differential amplifier contains two active elements (BJTs, JFETs, or MOSFETs) and thus two, independent, uncorrelated sources of ena and ina. The equivalent input circuit of a DA is shown in Figure 9.14. To simplify analysis, the two amplifier input resistances that appear in parallel with the inas have been set to infinity (i.e.,

omitted) because Rs Rin. All the noise sources are assumed to be white, |

||||||||

e |

na |

= e ′ |

RMSV/ Hz, and i |

= i ′ RMSA/ Hz, although certainly e |

na |

(t) π |

||

|

na |

|

|

na |

na |

|

||

e ′ (t) and i |

na |

(t) π i ′ (t), except very rarely. Recall that, for a DA, |

|

|

||||

|

na |

|

|

na |

|

|

|

|

|

|

|

|

|

|

vo = ADvid + ACvic |

(9.65) |

|

where AD is the scalar difference-mode gain; AC is the scalar common-mode gain; vid is the difference-mode input signal; and vic is the common-mode input signal. By definition:

vid ∫ (vi − vi′)/2 |

(9.66A) |

© 2004 by CRC Press LLC

356 |

Analysis and Application of Analog Electronic Circuits |

|

|

vic ∫ (vi + vi′)/2 |

(9.66B) |

Also recall that the common-mode rejection ratio for the simple DA could be expressed as:

CMRR ∫ AD/AC |

(9.67) |

Under normal operating conditions, AD AC and CMRR 1.

9.6.2Calculation of the SNRO of the DA

Referring to Figure 9.14, the DA noise model circuit has six independent, uncorrelated noise sources. Thus the total noise PDS at the vi node can be written:

S |

= e |

na |

2 + i |

na |

2R 2 |

+ 4kTR |

s |

MSV/Hz |

(9.68) |

ni |

|

|

s |

|

|

|

Similarly, the total noise PDS at the vi′ node is:

S ′ = e ′ 2 |

+ i ′2 |

R 2 |

+ 4kTR |

s |

MSV/Hz |

(9.69) |

ni na |

na |

s |

|

|

|

To find the MS SNRo of the noisy DA, assume that the input signal is pure

DM. Thus vic = 0, vid = vs, and vos2 = AD2 vs2 MSV. To find the MS noise output, set vs = vs′ = 0 and consider that the six noise sources add in quadrature (in

an MS sense). First, note that in the time domain:

vi(t) = ena(t) + ina(t)Rs + enrs(t) V |

(9.70) |

and

vi′(t) = ena′(t) + ina′(t)Rs′+ enrs′(t) V

Now expand and square Equation 9.65 for the amplifier output:

v 2 |

(t) = A 2 |

|

vi2 |

− 2vivi′ + vi′2 |

˘ |

+ 2A A |

|

vi |

− vi′ |

˘ |

vi |

+ vi′ |

˘ |

+ A 2 |

|

vi2 |

+ 2vivi′ |

|

|

|

|

|

|

|

|

||||||||||

on |

D |

|

4 |

˙ |

D C |

|

˙ |

|

˙ |

C |

|

4 |

|||||

|

|

|

˚ |

|

|

2 ˚ |

2 ˚ |

|

|

||||||||

(9.71)

2 ˘

+ vi′ ˙˚ (9.72)

When the expressions for vi(t) and vi′(t) from Equation 9.70 and Equation 9.71 are substituted into Equation 9.72 and the expectation or mean is taken, cross terms between vi and vi′ vanish because of statistical independence and no correlation. Also, the means of self-cross terms such as ena′(ina′Rs′) also

vanish for the same reasons. Recall that because the DA is symmetrical, ena = ena′ RMSV/ Hz, ina = ina′ RMSA/ Hz and Rs = Rs′. After some algebra that

will not be reproduced here, the MS output noise is given by:

© 2004 by CRC Press LLC