- •Вступ 6 зм 1. Електричні властивості напівпровідників 9

- •Зм 2. Напівпровідникові прилади 26

- •Зм 3. Електронні пристрої 79

- •Зм 4. Електронні елементи мікропроцесорної техніки 164

- •Зм 1. Електричні властивості напівпровідників

- •1.1. Основи зонної теорії твердого тіла.

- •1.2. Електропровідність напівпровідників.

- •1.2.1. Власна електропровідність напівпровідників

- •1.2.2. Домішкова електропровідність напівпровідників

- •1 .2.3. Ефекти, що пов’язані з електропровідністю напівпровідників

- •1.3. Властивості електронно-діркового переходу.

- •1.3.1. Формування електронно-діркового переходу.

- •1.3.2. Властивості n-p переходу при підключенні зовнішньої напруги

- •1.3.3. Тунельний ефект

- •1.4. Питання для самоперевірки.

- •Зм 2. Напівпровідникові прилади

- •2.1. Напівпровідникові діоди1

- •2.1.1. Випрямляючі діоди

- •2.1.2. Стабілітрони і схеми стабілізації напруги.

- •2.1.3. Варикапи

- •2.1.4. Тунельні діоди

- •2.1.5. Інші види діодів

- •2.2. Біполярні транзистори і їх використання в електронних пристроях

- •2.2.1. Устрій та принцип роботи біполярного транзистора.

- •2.2.2. Режими роботи біполярного транзистора.

- •2.2.3. Схеми включення транзисторів.

- •2.2.4. Вольт-амперні характеристики біполярних транзисторів та режими роботи (на прикладі n-p-n транзисторів).

- •2.2.5. Транзистор як активний чотирьохполюсник.

- •2.3. Уніполярні транзистори.

- •2.4. Тиристори

- •2.5. Питання для самоперевірки.

- •Зм 3. Електронні пристрої

- •3.1. Випрямлячі змінного струму.

- •3.2. Підсилювачі електричних сигналів.

- •3.2.1. Загальна інформація.

- •3.2.2. Характеристики підсилювачів

- •3.2.3. Зворотний зв’язок в підсилювачах.

- •3.2.4. Схеми підсилювальних каскадів на біполярних транзисторах.

- •3.2.5. Особливості роботи схеми попередніх каскадів підсилювача.

- •3.2.6. Режими роботи підсилюючих елементів.

- •3.2.7. Особливості роботи схеми кінцевого каскаду підсилювача.

- •3.2.8. Складені транзистори.

- •3.2.9. Спеціальні види підсилювачів.

- •3.3. Транзисторні генератори електричних сигналів.

- •3.3.1. Генератори синусоїдальних коливань.

- •3.3.2. Генератори імпульсів складної форми.

- •3.3.2.1. Параметри імпульсів прямокутної форми.

- •3.3.2.2. Мультивібратори.

- •3.3.2.3. Очікуючий мультивібратор або одновібратор.

- •3.3.2.4. Блокінг-генератори.

- •3.3.2.5. Генератори пилкоподібної напруги (гпн).

- •3.3.3. Генератори сигналів на операційних підсилювачах1.

- •3.4. Питання для самоперевірки.

- •Зм 4. Електронні елементи мікропроцесорної техніки

- •4.1. Уявлення про мікропроцесорну техніку, мікропроцесорні засоби і мікропроцесорні системи.

- •4.2. Структура мікропроцесорної системи.

- •4.2.1. Загальне уявлення про мікропроцесорну систему.

- •4.2.2. Мікропроцесорні засоби в системах керування

- •4.3. Елементи математичного апарату цифрової техніки.

- •4.3.1. Системи числення.

- •4.3.2. Фізичне уявлення інформації в мп-системі.

- •4.3.3. Форми представлення чисел.

- •4.3.4. Кодування чисел в мп-системах

- •4.3.5. Поняття булевої змінної та булевої функції

- •4.3.6. Операції та закони булевої алгебри.

- •4.3.7. Функціонально повні системи булевих функцій.

- •4.3.8. Мінімізація булевих функцій.

- •4.4. Цифрові схеми та цифрові автомати.

- •4.4.1. Елементи ртл.

- •4.4.2. Елементи дтл.

- •4.4.3. Елементи ттл.

- •4.4.4. Елементи езл.

- •4.4.5. Інтегральні схеми на моп–транзисторах.

- •4.5. Комбінаційні цифрові пристрої.

- •4.5.1 Дешифратор.

- •4.5.2. Перетворювачі кодів і шифратори.

- •4.5.3. Мультиплексори і демультиплексори.

- •4.5.4. Напівсуматор і суматор.

- •4.6. Послідовнісні пристрої.

- •4.6.1. Тригери.

- •4.6.1.1. Синхронний однотактний rs–тригер.

- •4.6.1.2. Синхронний двотактний rs–тригер.

- •4.6.2. Регістри.

- •4.6.2.1. Прийом і передача інформації в регістрах.

- •4.6.2.2. Схемна реалізація зсуваючого регістру

- •4.6.2.3. Реалізація порозрядних операцій в регістрах.

- •4.6.3. Лічильники.

- •4.6.3.1. Загальне уявлення і класифікація.

- •4.6.3.2. Лічильник з безпосередніми зв’язками з послідовним переносом.

- •4.6.3.3. Лічильник з паралельним переносом.

- •4.6.3.4. Реверсивний лічильник з послідовним переносом.

- •4.6.4. Накопичуючі суматори.

- •4.6.4.1. Однорозрядний накопичуючий суматор.

- •4.6.4.2. Багаторозрядні суматори

- •4.6.5. Електронні елементи пам’яті.

- •4.6.6. Перетворювачі сигналів.

- •4.7. Питання для самоперевірки.

- •Додаток

- •Префікси для кратних одиниць

- •Список рекомендованої літератури

4.6.4.2. Багаторозрядні суматори

В залежності від того, як передаються

коди доданків, можуть бути два способи

додавання, а відповідно два типу

суматорів: послідовні і паралельні.

залежності від того, як передаються

коди доданків, можуть бути два способи

додавання, а відповідно два типу

суматорів: послідовні і паралельні.

Послідовні суматори – це однорозрядні суматори, в яких числа-доданки надходять послідовним кодом і перетворюються на послідовний код сум цих доданків.

Паралельні суматори – це суматори, в яких використовується паралельний код. Такий суматор складається з окремих однорозрядних суматорів в кожному розряді.

На рис. 4.73 наведена схема паралельного n-розрядного суматора з крізним переносом. Коло крізного переносу є частиною схем суматорів і уявляє собою коло послідовно включених схем І–АБО (І–АБО1 на рис. 4.71, 4.72).

В цьому суматорі n–розрядні числа x1 x2…xn і y1 y2…yn подаються одночасно на його входи. Перенос рі–1 кожного окремого попереднього однорозрядного суматора подається на вхід переносу наступного однорозрядного суматора.

Швидкодія такого суматора визначається часом сумування в одному розряді tс і часом розповсюдження переносу tр.п. послідовно по всьому n–розрядному суматорі, тобто Т = tс + (n–1) tр.п.. Для підвищення швидкодії суматори виконують з використанням схем з прискореним розповсюдженням переносів (паралельним або груповим).

Суматори в більшості випадків входять до складу структури ВІС мікропроцесорів (складають основу арифметико-логічного блоку мікропроцесора) та інших пристроїв. Але можуть використовуватись як окремі самостійні вузли.

4.6.5. Електронні елементи пам’яті.

Зазначимо, що тут розглядатимуться тільки питання реалізації інформаційного процесу утримання інформації електронними схемами. Організація ж пам’яті МПС і комп’ютерів зокрема розглядається в посібниках з дисципліни «Архітектура комп’ютерів».

Оперативна пам’ять будується на базі відносно недорогої динамічної пам’яті − DRAM і статичної пам’яті невеликого об’єму – SRAM, яка є буфером між процесором і пам’яттю DRAM.

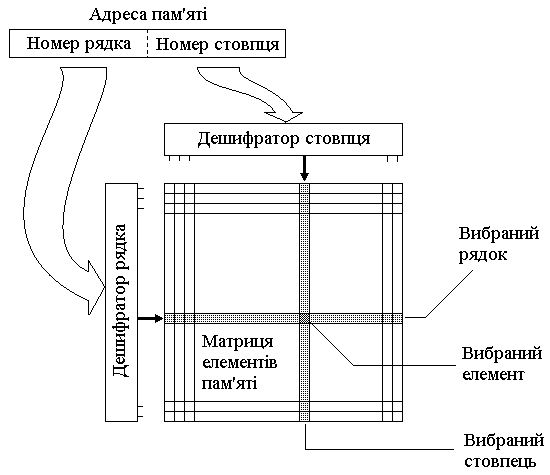

При довільному адресному доступі для запису або читання місце розташування інформації в запам’ятовуючому пристрої (ЗП) визначається її адресою. Логічно адреса може мати різну структуру. Наприклад, в оперативних ЗП адреса уявляє собою двійковий код, одна частина розрядів якого вказує рядок матриці елементів пам’яті, а інша – стовпчик цієї матриці. На перетині визначених рядка і стовпчика знаходиться шукана інформація (див. рис. 4.74).

Рис. 4.74.

DRAM (Dynamic Random Access Memory) − тип енергозалежної напівпровідникової пам’яті з довільним доступом (RAM), а також запам’ятовуючий пристрій, який найбільш широко використовується в якості оперативної пам’яті сучасних комп’ютерів.

Пам’ять DRAM складається з вічок − елементів пам’яті, створених в напівпровідниковому матеріалі, у кожному з яких можна зберігати 1 біт даних. Сукупність елементів такої пам’яті утворюють умовний «прямокутник» − матрицю, що складається з певної кількості рядків і стовпців. Один такий «прямокутник» називають сторінкою, а сукупність сторінок − банком.

DRAM відноситься до запам’ятовуючих пристроїв (ЗП) із адресним доступом. Тобто при записі або читанні місце розташування інформації в ЗП визначається її адресою. Як зазначалось, логічно структура адреси уявляє собою двійковий код, одна частина розрядів якого вказує рядок матриці елементів пам’яті, а інша – стовпчик цієї матриці. На перетині визначених рядка і стовпчика знаходиться елемент пам’яті. Щоб отримати доступ до будь-якого запам’ятовуючого елемента матриці необхідно вибрати відповідний рядок і стовпець. Вибір відбувається за сигналами дешифраторів рядків і стовпців, до яких надходять відповідні частини адреси.

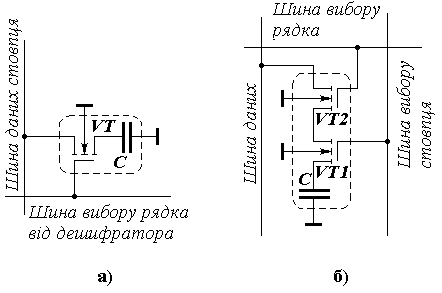

Рис. 4.75.

На рис. 4.75 представлені варіанти елементів пам’яті DRAM об’ємом в 1 біт: а) на конденсаторі С і одному транзисторі VT із вибором рядка; б) на конденсаторі і двох транзисторах VT1 і VT2 із вибором рядка і стовпця. Фізично елемент пам’яті DRAM об’ємом в 1 біт (рис. 4.75-а) складається з конденсатора С і транзистора VT (на рис. − польовий транзистор із індукованим каналом n-типу, хоча можливий і інший тип, див. ч. 2, п. 2.3). Насправді, окремого конденсатора немає, його роль виконує бар’єрна ємність (див. ч. 2, п. 2.1.3) між затвором і витоком транзистора. Але для простоти викладу ємність виділена як би в окремий елемент. Саме наявністю або відсутністю зарядів на конденсаторі і кодуються біти. Транзистор в елементі працює як ключ, що керує передачею заряду. Під час запису в конденсатор біта інформації ключ відкривається (сигнал відкриття транзистора надходить по горизонтальній шині (рис.4.75)), і сигнал із вертикальної шини при записі «1» надходить через відкритий транзистор заряджаючи конденсатор до певної величини, а під час читання заряд із конденсатора (він є, якщо конденсатор зберігає «1») через відкритий ключ надходить на вертикальну шину і, далі як підсилений сигнал, на шину даних МПС. При записі або читанні «0», хоча в обраному елементі ключ відкривається, але ніяких дій із конденсатором не відбувається – при записі він не заряджається, при читанні із нього не надходить на вертикальну шину заряд.

Як видно, при читанні «1» в елементі пам’яті заряд конденсатора, а відповідно і інформація втрачаються. Крім того, вона втрачається із часом, оскільки відбувається поступовий розряд конденсатора через n-p перехід − «стікання» заряду. Тому інформацію доводиться оновлювати і після читання, і через певні проміжки часу, щоб уникнути втрат даних. Цей процес називається регенерацією пам’яті.

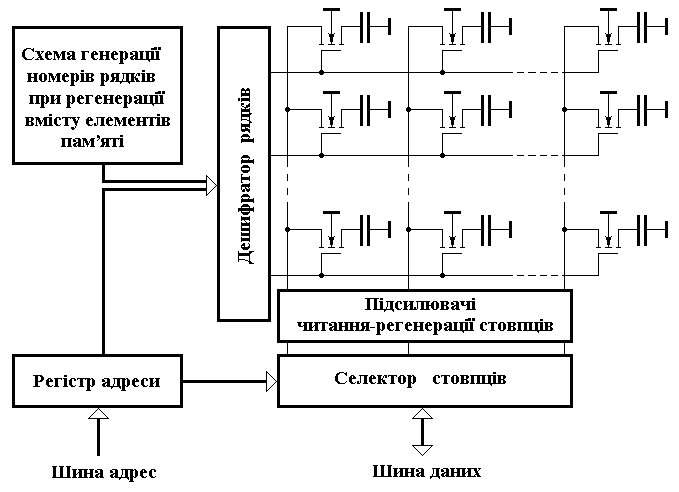

Рис. 4.76.

Періодична регенерація реалізується спеціальним контролером, встановленим на системній платі або ж на кристалі центрального процесора і ініціюється інтервальним таймером кожні 15 мкс. Протягом часу, що називається кроком регенерації, в DRAM перезаписується цілий рядок елементів, і через 8 − 64 мс оновлюються всі рядки пам’яті. Крім того, регенерація вмісту всіх елементів рядка відбувається і при звертанні до будь-якого елементу рядка.

Структурна схема сторінки DRAM-пам’яті показана на рис. 4.76. При звертанні до DRAM-пам’яті – при записі, при читанні, при регенерації, послідовно відбуваються два процеси – читання, запис. Це забезпечує при записі попереднє «скидання в нуль» всіх елементів вибраного рядка матриці і запам’ятовуванням інформації рядка в підсилювачах читання-регенерації стовпців із наступним її відновленням, або відновленням і модифікацією для вибраного елемента, при записі.

В ажливим

елементом пам’яті цього типу є чутливий

підсилювач (англ. sense amp), підключений до

кожного стовпця матриці (рис. 4.77). Він,

реагуючи на слабкий потік електронів

із конденсаторів, сприймає рівень

напруги на відповідній шині як «0», або

як «1». Сприйнята інформація тимчасово

утримується на конденсаторі С1

і, завдяки зворотному зв’язку через

транзистор VT1,

відповідний потенціал відновлюється

на шині стовпця, що в свою чергу забезпечує

відновлення заряду конденсатора елемента

пам’яті. При записі нової інформації

в процесі відновлення відбувається її

модифікація новим значенням біта, яке

надходить до кола зворотного зв’язку

через транзистор VT2.

ажливим

елементом пам’яті цього типу є чутливий

підсилювач (англ. sense amp), підключений до

кожного стовпця матриці (рис. 4.77). Він,

реагуючи на слабкий потік електронів

із конденсаторів, сприймає рівень

напруги на відповідній шині як «0», або

як «1». Сприйнята інформація тимчасово

утримується на конденсаторі С1

і, завдяки зворотному зв’язку через

транзистор VT1,

відповідний потенціал відновлюється

на шині стовпця, що в свою чергу забезпечує

відновлення заряду конденсатора елемента

пам’яті. При записі нової інформації

в процесі відновлення відбувається її

модифікація новим значенням біта, яке

надходить до кола зворотного зв’язку

через транзистор VT2.

Таким чином, при читанні із DRAM-пам’яті: дешифратор рядка за частиною коду адреси звертання обирає потрібний рядок матриці; заряди з конденсаторів всіх елементів цього рядка через шини стовпчиків надходять до підсилювачів стовпчиків, при цьому інформація в рядку втрачається; через зворотний зв’язок в підсилювачах відновлюється електричні потенціали шин всіх стовпчиків і, відповідно, відновлюються заряди всіх конденсаторів обраного рядка – інформація в рядку регенерується; селектор обирає стовпчик, який визначається другою частиною адреси звертання, і напруга саме цього стовпця, крім того, що вона повертається у шину стовпця, надходить і на шину даних як зчитаний біт інформації. Селектор в цьому випадку грає роль мультиплексора (див. ч. 2, п. 4.5.5).

При записі в DRAM-пам’ять: дешифратор рядка за частиною коду адреси звертання обирає потрібний рядок матриці; заряди з конденсаторів всіх елементів цього рядка через шини стовпчиків надходять до підсилювачів стовпчиків, при цьому інформація в рядку втрачається; напруга що надійшла через селектор від шини даних як біт записуваної інформації змінює потенціал в колі зворотного зв’язку і шини вибраного відповідно другої частини адреси звертання стовпця, селектор в цьому випадку працює як демультиплексор (див. ч. 2, п. 4.5.5); через зворотний зв’язок в підсилювачах відновлюється електричні потенціали шин всіх стовпчиків за виключенням шини, в якій потенціал відповідає новій інформації, і, відповідно, відновлюються заряди всіх конденсаторів обраного рядка – інформація в рядку регенерується, а для вибраного елемента модифікується.

При «плановій» регенерації DRAM-пам’яті: контролер пам’яті МПС, встановлений на системній платі або ж на кристалі центрального процесора і, який налаштований на відповідну промисловим стандартам частоту регенерації, періодично звертається по-черзі до всіх рядків даних у мікросхемах пам’яті, генеруючи адреси рядків; заряди з конденсаторів всіх елементів поточного рядка через шини стовпчиків надходять до підсилювачів стовпчиків, при цьому інформація в рядку втрачається; через зворотний зв’язок в підсилювачах відновлюється електричні потенціали шин всіх стовпчиків і, відповідно, відновлюються заряди всіх конденсаторів обраного рядка – інформація в рядку регенерується. Інформація на/від шини даних не надходить. Підсилювачі відносно шини даних знаходяться у високоімпедансному стані1.

Таке динамічне підтримання заряду конденсатора є основним принципом роботи пам’яті типу DRAM.

Процес регенерації пам’яті в класичному варіанті суттєво «гальмує» роботу системи, оскільки в цей час обмін даними з пам’яттю неможливий: кожен цикл регенерації по тривалості займає кілька циклів центрального процесора. У старих комп’ютерах цикли регенерації могли займати до 10% (або більше) процесорного часу, але в сучасних системах, що працюють на частотах, рівних сотням мегагерц, витрати на регенерацію складають 1% (або менше) процесорного часу. Деякі системи дозволяють змінити параметри регенерації, але збільшення часу між циклами регенерації може призвести до того, що в деяких елементах пам’яті заряд «стече», а це викликає втрату інформації і збої пам’яті. У більшості випадків надійніше дотримуватися рекомендованої або заданої за замовчуванням частоти регенерації.

Однак, у пристроях DRAM для зберігання одного біта використовується тільки один транзистор і конденсатор, тому вони більш місткі, ніж мікросхеми інших типів пам’яті. В даний час є мікросхеми динамічної оперативної пам’яті ємністю в кілька гігабайт. У мікросхемі пам’яті всі транзистори і конденсатори розміщуються послідовно, зазвичай у вузлах квадратної решітки, у вигляді дуже простих, що періодично повторюються структур. Тому динамічна оперативна пам’ять використовується в персональних комп’ютерах; оскільки вона недорога, мікросхеми можуть бути щільно упаковані, а це означає, що запам’ятовуючий пристрій великої ємності може займати невеликий простір. На жаль, пам’ять цього типу не відрізняється високою швидкодією, зазвичай вона набагато «повільніше» процесора. Тому існує багато різних типів організації DRAM, що дозволяють поліпшити цю характеристику.

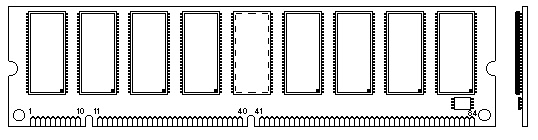

Модулі динамічної напівпровідникової пам’яті пройшли еволюцію від набору мікросхем, що встановлюються на системній платі і помітних по своєму регулярному розташуванню (кілька суміжних рядів однакових мікросхем) до окремих невеликих плат − модулів з розташованими на них мікросхемами DRAM, що вставляються в стандартний роз’єм (слот) системної плати (рис. 4.78).

Рис. 4.78.

Ядро мікросхеми статичної оперативної пам’яті (SRAM − Static Random Access Memory) являє собою сукупність тригерів − логічних пристроїв, що мають два стійких стани, один з яких умовно відповідає логічному нулю, а інший − логічній одиниці (див. ч. 2, п. 4.6.1). Іншими словами, кожен тригер зберігає один біт інформації, − стільки ж, скільки і елемент динамічної пам’яті.

Тригер, як елемент пам’яті, має дві переваги в порівнянні з конденсаторним елементом динамічної пам’яті: а) стани тригера стійкі і за наявності живлення можуть зберігатися нескінченно довго, в той час як конденсатор вимагає періодичної регенерації; б) тригер, маючи малий час перемикання, працює на частотах аж до кількох ГГц, тоді як конденсатори не встигають перезаряджатись вже на 75−100 МГц. Тому статична пам’ять дозволяє досягти найбільшої швидкодії, забезпечуючи час доступу до одиниць і навіть десятих часток наносекунд, що й обумовлює її використання, головним чином, у вищих щаблях пам’яті ЕОМ − кеш-пам’яті всіх рівнів.

До недоліків тригерів слід віднести їх високу вартість та низьку щільність зберігання інформації. Якщо для створення елемента динамічної пам’яті достатньо всього одного транзистора і одного конденсатора, то елемент статичної пам’яті складається як мінімум з чотирьох, а в середньому шести − восьми транзисторів, тому мегабайт статичної пам’яті виявляється щонайменше у кілька разів дорожче.

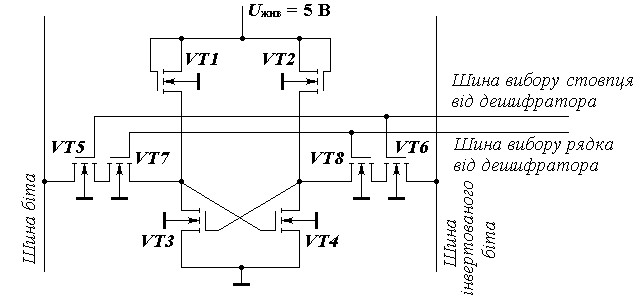

Один із варіантів тригерного елемента пам’яті SRAM показаний на рис. 4.79. В основі тригера лежить кільце з двох логічних елементів «НЕ» (інверторів) із взаємно зворотними додатними зв’язками, наявність яких призводить до того, що в стійкому стані один транзистор відкритий, а інший закритий. Роль інверторів виконують пари транзисторів VT1, VT3 і VT2, VT4, причому транзистори VT1 і VT2 − це навантаження (на рис. 4.48 – це опори Rн1 і Rн2 відповідно). Сигнал із виходу транзистора VT3 через перехресний зворотний зв’язок подається на затвор транзистора VT4 і навпаки. Отже безпосередньо тригер побудований на транзисторах VT1 − VT4.

Подібно елементам динамічної пам’яті, тригери об’єднуються в єдину матрицю, що складається з рядків (row) і стовпців (column).

На відміну від елемента динамічної пам’яті, для управління якої достатньо лише одного (або двох, як на рис. 4.75-б) ключового транзистора, елемент статичної пам’яті управляється як мінімум двома, оскільки тригер, на відміну від конденсатора, має окремі входи для запису-читання прямого і інвертованого значення біта. Таким чином, на елемент статичної пам’яті витрачається вісім транзисторів − чотири йдуть, власне, на сам тригер і ще по два − на керуючі входи-виходи елемента. Варіант такого 8-транзисторного елемента пам’яті SRAM представлений на рис. 4.79.

Рис. 4.79.

При звертанні до такого елемента пам’яті SRAM активізується визначена частиною адреси звертання шина вибору стовпця, відкриваючи транзистори VT5, VT6 всіх елементів стовпця і, визначена іншою частиною адреси, шина вибору рядка, відкриваючи транзистори VT7, VT8 всіх елементів рядка (рис. 4.79). Оскільки пари транзисторів VT5, VT7 і VT6, VT8 включені послідовно, то доступ до входів-виходів отримує елемент, що знаходиться на перетині обраного рядка і обраного стовпця.

При записі значення біта парафазним кодом1 надходить по шинам біта через відкриті ключові транзистори VT5, VT7 і VT6, VT8 обраного елемента до затворів транзисторів VT3, VT4 тригера, що призводить до встановлення в тригері нового стану. В цьому стані тригер буде знаходитись і після зняття сигналів з бітових шин та з шин вибору рядка і стовпця, зберігаючи нову інформацію.

При читанні рівні напруг, які відповідають занесеній в тригер інформації, знов таки через відкриті ключові транзистори VT5, VT7 і VT6, VT8 обраного елемента надходять до бітових шин, утворюючи парафазний код біта, і далі до схем читання-запису – підсилювачів і т.д. Тригер при цьому свій стан не змінює, оскільки енергія при читанні постачається джерелом живлення (Uжив), отже регенерація інформації в тригері не потрібна.

Постійні запам’ятовуючі пристрої (ПЗП або Read Only Memory − ROM) в МП-системах використовуються для зберігання програм та іншої незмінюваної інформації. Важлива перевага ПЗП в порівнянні з ОЗП – зберігання інформації при виключеному живленні. Вартість біта зберігаємої в ПЗП інформації може бути майже на порядок нижча ніж в ОЗП.

Постійні ЗП можуть бути реалізовані на основі різних фізичних принципів та елементів і відрізняються способом занесення інформації, кратністю занесення, способом стирання.

Застосовуються такі види ПЗП:

ПЗП, в яких інформація закладається на заводі-виробнику, так звані масочні ПЗП (МПЗП);

ПЗП, в яких інформація закладається користувачем;

ПЗП, що перепрограмовуються.

Перші два види ПЗП допускають тільки однократне занесення інформації (програмування), третій – дозволяє багатократно змінювати інформацію, що в ньому зберігається.

Масочні ПЗП програмуються на заводі-виробнику. За поданою замовником інформацією створюються фотошаблони, за допомогою яких інформацію вносять в кристал ПЗП в процесі його виробництва. Цей спосіб самий дешевий і призначений для крупносерійного виробництва ПЗП.

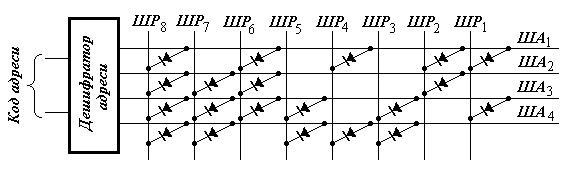

Масочні ПЗП будуються на основі діодів, біполярних та МДП–транзисторів. В діодних ПЗП діоди включені на тих перетинах матриці, які відповідають запису «1», і відсутні в місцях, де повинний бути записаний «0». Фрагмент ПЗП, що складається з діодної матриці та дешифратора адреси показано на рис. 4.80.

Рис. 4.80.

Горизонтальні шини матриці – адресні; вертикальні – розрядні, з яких знімаються восьмирозрядні двійкові числа, що записані в ПЗП. Якщо, наприклад, з виходу дешифратора збуджується адресна шина ША2, то високий потенціал проходить з неї через діоди на розрядні шини ШР2, ШР6, ШР7, ШР8, встановлюючи на виході двійкове число 11100010. Аналогічно, при збудженні інших адресних шин на виходах встановлюються інші двійкові числа. Відзначимо, що діодна матриця (рис. 4.80) є сукупністю елементів АБО. Кожний з них складається з діодів, підключених до однієї розрядної шини, а входами цих елементів є адресні шини.

Масочні ПЗП характеризуються більшою надійністю, але при їх виготовлені виникає ряд незручностей для замовника та виробника. Велика номенклатура ПЗП і мала їх тиражність, призводить до того, що на виробника накладаються підвищені витрати на фотошаблони, що збільшує вартість ПЗП. Відсутня можливість оперативно змінювати інформацію в ПЗП без виготовлення нової ІС, що особливо незручно на етапі відпрацювання програм системи.

П ЗП,

що програмуються користувачем,

є більш універсальними і, відповідно

більш дорожчими приладами. Структура

ПЗП з однократним програмуванням

показана на рис. 4.81. Вони уявляють собою

матриці біполярних приладів, в яких

зв’язки між розрядними і адресними

шинами порушуються при занесені на

спеціальних програмуючих пристроях

(програматорах) відповідних кодових

комбінацій. Ці пристрої виробляють

напруги, необхідні і достатні для

перепалювання плавких перемичок в

потрібних елементах ПЗП. Можливість

програмування користувачем зробила

ПЗП цього типу надзвичайно зручними

при розробці МП-систем.

ЗП,

що програмуються користувачем,

є більш універсальними і, відповідно

більш дорожчими приладами. Структура

ПЗП з однократним програмуванням

показана на рис. 4.81. Вони уявляють собою

матриці біполярних приладів, в яких

зв’язки між розрядними і адресними

шинами порушуються при занесені на

спеціальних програмуючих пристроях

(програматорах) відповідних кодових

комбінацій. Ці пристрої виробляють

напруги, необхідні і достатні для

перепалювання плавких перемичок в

потрібних елементах ПЗП. Можливість

програмування користувачем зробила

ПЗП цього типу надзвичайно зручними

при розробці МП-систем.

Найбільше розповсюдження отримали ПЗП з з плавкими перемичками, ультрафіолетовим стиранням (УФ-стиранням), з електричним стиранням і записом інформації.

Запам’ятовуючим елементом в ПЗП з УФ-стиранням є МОП–транзистор, розташований на перетині відповідних адресної і розрядної шини. Вміст запам’ятовуючого елемента зберігається у вигляді заряду на другому (плаваючому) затворі МОП–транзистора. Затвор називається плаваючим, якщо він розміщений між керуючим затвором транзистора і його каналом і оточений високоомним діелектриком.

ПЗП, що перепрограмовуються – це ПЗП з вмістом, що змінюється. На затворах матриці МОП–транзисторів тривалий час можуть зберігатись заряди, що утворюють заданий код. Всі ПЗП, що перепрограмовуються уявляють собою МОП-прилади. При необхідності в перепрограмуванні мікросхеми ПЗП попередньо записану інформацію стирають ультрафіолетовим світлом через прозоре кварцове вікно на поверхні корпусу мікросхеми. Попадаючи на плаваючий затвор і вибиваючи з нього фотоелектрони, УФ-випромінювання розряджає плаваючий затвор МОП–транзистора. Час збереження інформації в мікросхемах ПЗП даного типу визначається якістю призатворного діелектрика і для сучасних мікросхем складає більш десяти років.