- •Вступ 6 зм 1. Електричні властивості напівпровідників 9

- •Зм 2. Напівпровідникові прилади 26

- •Зм 3. Електронні пристрої 79

- •Зм 4. Електронні елементи мікропроцесорної техніки 164

- •Зм 1. Електричні властивості напівпровідників

- •1.1. Основи зонної теорії твердого тіла.

- •1.2. Електропровідність напівпровідників.

- •1.2.1. Власна електропровідність напівпровідників

- •1.2.2. Домішкова електропровідність напівпровідників

- •1 .2.3. Ефекти, що пов’язані з електропровідністю напівпровідників

- •1.3. Властивості електронно-діркового переходу.

- •1.3.1. Формування електронно-діркового переходу.

- •1.3.2. Властивості n-p переходу при підключенні зовнішньої напруги

- •1.3.3. Тунельний ефект

- •1.4. Питання для самоперевірки.

- •Зм 2. Напівпровідникові прилади

- •2.1. Напівпровідникові діоди1

- •2.1.1. Випрямляючі діоди

- •2.1.2. Стабілітрони і схеми стабілізації напруги.

- •2.1.3. Варикапи

- •2.1.4. Тунельні діоди

- •2.1.5. Інші види діодів

- •2.2. Біполярні транзистори і їх використання в електронних пристроях

- •2.2.1. Устрій та принцип роботи біполярного транзистора.

- •2.2.2. Режими роботи біполярного транзистора.

- •2.2.3. Схеми включення транзисторів.

- •2.2.4. Вольт-амперні характеристики біполярних транзисторів та режими роботи (на прикладі n-p-n транзисторів).

- •2.2.5. Транзистор як активний чотирьохполюсник.

- •2.3. Уніполярні транзистори.

- •2.4. Тиристори

- •2.5. Питання для самоперевірки.

- •Зм 3. Електронні пристрої

- •3.1. Випрямлячі змінного струму.

- •3.2. Підсилювачі електричних сигналів.

- •3.2.1. Загальна інформація.

- •3.2.2. Характеристики підсилювачів

- •3.2.3. Зворотний зв’язок в підсилювачах.

- •3.2.4. Схеми підсилювальних каскадів на біполярних транзисторах.

- •3.2.5. Особливості роботи схеми попередніх каскадів підсилювача.

- •3.2.6. Режими роботи підсилюючих елементів.

- •3.2.7. Особливості роботи схеми кінцевого каскаду підсилювача.

- •3.2.8. Складені транзистори.

- •3.2.9. Спеціальні види підсилювачів.

- •3.3. Транзисторні генератори електричних сигналів.

- •3.3.1. Генератори синусоїдальних коливань.

- •3.3.2. Генератори імпульсів складної форми.

- •3.3.2.1. Параметри імпульсів прямокутної форми.

- •3.3.2.2. Мультивібратори.

- •3.3.2.3. Очікуючий мультивібратор або одновібратор.

- •3.3.2.4. Блокінг-генератори.

- •3.3.2.5. Генератори пилкоподібної напруги (гпн).

- •3.3.3. Генератори сигналів на операційних підсилювачах1.

- •3.4. Питання для самоперевірки.

- •Зм 4. Електронні елементи мікропроцесорної техніки

- •4.1. Уявлення про мікропроцесорну техніку, мікропроцесорні засоби і мікропроцесорні системи.

- •4.2. Структура мікропроцесорної системи.

- •4.2.1. Загальне уявлення про мікропроцесорну систему.

- •4.2.2. Мікропроцесорні засоби в системах керування

- •4.3. Елементи математичного апарату цифрової техніки.

- •4.3.1. Системи числення.

- •4.3.2. Фізичне уявлення інформації в мп-системі.

- •4.3.3. Форми представлення чисел.

- •4.3.4. Кодування чисел в мп-системах

- •4.3.5. Поняття булевої змінної та булевої функції

- •4.3.6. Операції та закони булевої алгебри.

- •4.3.7. Функціонально повні системи булевих функцій.

- •4.3.8. Мінімізація булевих функцій.

- •4.4. Цифрові схеми та цифрові автомати.

- •4.4.1. Елементи ртл.

- •4.4.2. Елементи дтл.

- •4.4.3. Елементи ттл.

- •4.4.4. Елементи езл.

- •4.4.5. Інтегральні схеми на моп–транзисторах.

- •4.5. Комбінаційні цифрові пристрої.

- •4.5.1 Дешифратор.

- •4.5.2. Перетворювачі кодів і шифратори.

- •4.5.3. Мультиплексори і демультиплексори.

- •4.5.4. Напівсуматор і суматор.

- •4.6. Послідовнісні пристрої.

- •4.6.1. Тригери.

- •4.6.1.1. Синхронний однотактний rs–тригер.

- •4.6.1.2. Синхронний двотактний rs–тригер.

- •4.6.2. Регістри.

- •4.6.2.1. Прийом і передача інформації в регістрах.

- •4.6.2.2. Схемна реалізація зсуваючого регістру

- •4.6.2.3. Реалізація порозрядних операцій в регістрах.

- •4.6.3. Лічильники.

- •4.6.3.1. Загальне уявлення і класифікація.

- •4.6.3.2. Лічильник з безпосередніми зв’язками з послідовним переносом.

- •4.6.3.3. Лічильник з паралельним переносом.

- •4.6.3.4. Реверсивний лічильник з послідовним переносом.

- •4.6.4. Накопичуючі суматори.

- •4.6.4.1. Однорозрядний накопичуючий суматор.

- •4.6.4.2. Багаторозрядні суматори

- •4.6.5. Електронні елементи пам’яті.

- •4.6.6. Перетворювачі сигналів.

- •4.7. Питання для самоперевірки.

- •Додаток

- •Префікси для кратних одиниць

- •Список рекомендованої літератури

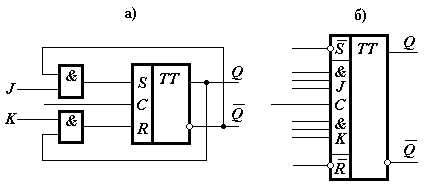

4.6.1.1. Синхронний однотактний rs–тригер.

Н а

рис. 4.51 наведена

схема (а) і умовне позначення (б)

синхронного однотактного RS-тригера,

виконаного на елементах І–НЕ.

Елементи 1 і 2 утворюють схему вхідної

логіки RS-тригера,

побудованого на елементах 3 і 4. Такі

RS-тригери

мають інформаційні входи R

і S

і вхід синхронізації С.

Крім того, тригер може

мати асинхронні входи

а

рис. 4.51 наведена

схема (а) і умовне позначення (б)

синхронного однотактного RS-тригера,

виконаного на елементах І–НЕ.

Елементи 1 і 2 утворюють схему вхідної

логіки RS-тригера,

побудованого на елементах 3 і 4. Такі

RS-тригери

мають інформаційні входи R

і S

і вхід синхронізації С.

Крім того, тригер може

мати асинхронні входи

![]() і

і

![]() .

В цьому випадку його функціонування

здійснюється або під дією сигналів, що

надходять на несинхронізовані входи

при відсутності синхронізуючого сигналу

(С

= 0), або під дією сигналів, що надходять

на синхронізовані входи. В останньому

випадку на несинхронних входах повинні

бути сигнали, які не впливають на стан

схеми, в даному випадку –

=

=1.

.

В цьому випадку його функціонування

здійснюється або під дією сигналів, що

надходять на несинхронізовані входи

при відсутності синхронізуючого сигналу

(С

= 0), або під дією сигналів, що надходять

на синхронізовані входи. В останньому

випадку на несинхронних входах повинні

бути сигнали, які не впливають на стан

схеми, в даному випадку –

=

=1.

Вхідна інформація, що представлена в парафазному коді, заноситься в синхронний однотактний RS-тригер через елементи вхідної логіки 1 і 2 в момент t надходження імпульсу синхронізації. При С = 0 тригер буде знаходитись в режимі зберігання. При відсутності імпульсу синхронізації тригер може бути встановлений в стан 0 через одночасну подачу на несинхронізовані входи сигналів = 0, = 1.

Таблиця 4.11.

Таблиця переходів RS-тригера, побудованого на елементах І–НЕ, для синхронних входів R і S.

t |

t +1 |

Коментар |

||

C |

R |

S |

Q |

|

0 |

* |

* |

Q(t) |

Зберігання 0 або 1 |

1 |

0 |

0 |

Q(t) |

Зберігання 0 або 1 |

1 |

0 |

1 |

1 |

Встановлення 1 |

1 |

1 |

0 |

0 |

Встановлення 0 |

1 |

1 |

1 |

– |

Заборонена комбінація |

* – будь-яке значення |

||||

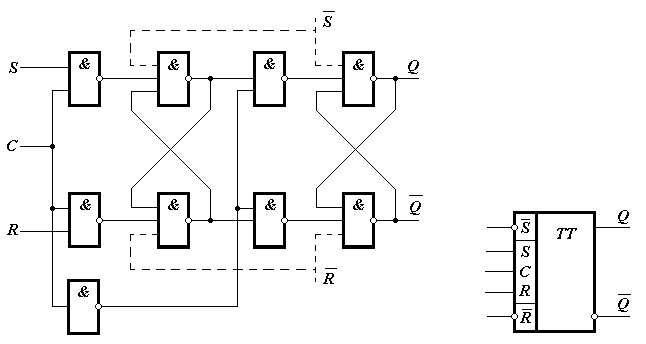

4.6.1.2. Синхронний двотактний rs–тригер.

При

передачі інформації між тригерами, яка

здійснюється за спільним синхросигналом,

важливо, щоб інформація в наступний в

ланцюгу тригерів елемент була передана

до надходження іншої інформації з

попереднього елемента. Короткочасну

затримку інформації при передачі

забезпечує двотактний принцип обміну

інформацією. Схема тригера, побудованого

за цим принципом, наведена на рис. 4.52-а

(умовне графічне позначення – на рис.

4.52-б). Вона складається з двох однотактних

RS-тригерів

та інвертора в колі синхронізації. При

надходженні на вхід RS-тригера

синхроімпульсу С = 1

вхідна інформація заноситься тільки в

перший однотактний RS-тригер,

а другий тригер при цьому буде зберігати

інформацію, що відноситься до попереднього

періоду представлення. По закінченню

дії імпульсу синхронізації (коли С

= 0, а

![]() =

1) перший RS-тригер

перейде в режим зберігання, а другий

перепише з нього нове значення стану.

На відміну від однотактних тригерів,

які змінюють значення вихідного сигналу

під час

дії синхроімпульсу,

двотактний тригер змінить свій стан

тільки після закінчення

дії

імпульсу синхронізації.

Тому з двотактних тригерів можна будувати

схеми, що мають зв’язки між виходами

одних тригерів і синхронними входами

інших.

=

1) перший RS-тригер

перейде в режим зберігання, а другий

перепише з нього нове значення стану.

На відміну від однотактних тригерів,

які змінюють значення вихідного сигналу

під час

дії синхроімпульсу,

двотактний тригер змінить свій стан

тільки після закінчення

дії

імпульсу синхронізації.

Тому з двотактних тригерів можна будувати

схеми, що мають зв’язки між виходами

одних тригерів і синхронними входами

інших.

а) б)

Рис. 4.52.

Для

встановлення тригера в стан 0 або 1 без

використання синхроімпульсів в схему

введені додаткові входи

![]() і

і

![]() несинхронізованого встановлення.

Зв’язки з цими входами показані на рис.

4.52-а пунктиром.

несинхронізованого встановлення.

Зв’язки з цими входами показані на рис.

4.52-а пунктиром.

Схеми RS-тригерів складають основу для побудови інших тригерних схем типу T-, D- і JK-тригерів.

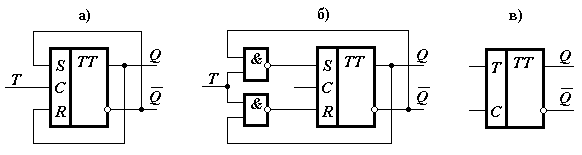

4.6.1.3. Т-тригер.

Це тригер з лічильним входом (однорозрядний лічильник). Він може бути побудований з використанням двотактного синхронного RS-тригера. Т-тригер реалізує функцію виду

![]()

тобто одиничний вхідний сигнал Т повинен міняти стан тригера на протилежний, а нульовий – залишати стан тригера без змін.

а) б) в)

Рис. 4.53.

Схема двотактного несинхронного Т-тригера, утвореного з RS-тригера, наведена на рис. 4.53-а. В цій схемі надходження сигналу Т = 1 на вхід С призводить до запису в двотактний RS-тригер стану, протилежного попередньому. Сигнал на виході тригера зміниться тільки після завершення дії сигналу Т = 1, що виключає виникнення генерації в схемі із зворотнім зв’язком.

На рис. 4.53-б представлена схема синхронного двотактного Т-тригера, а на рис. 4.53-в – його умовне позначення. Одиничний вхідний сигнал Т уявляється високою напругою при С = 1. Запис інформації в тригер здійснюється при С = 1, причому зміна стану, як звичайно в двотактних тригерах, відбувається після закінчення дії імпульсу синхронізації С = 1. При Т = 1 стан тригера змінюється на протилежний, а при Т = 0 – не змінюється.

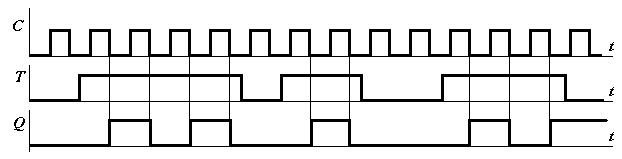

Часова діаграма роботи Т-тригера має вид, представлений на рис. 4.54.

Рис. 4.54.

Як видно з часової діаграми Т-тригер можна використовувати як асинхронний тригер з лічильним входом, якщо на інформаційний вхід Т подати константу 1, а логічну змінну подавати на вхід С.

Синхронні і асинхронні тригери з лічильним входом застосовуються в цифрових пристроях і мікропроцесорних системах для побудови схем лічильників.

4.6.1.4. D-тригер.

О дним

з

інтегральних тригерів,

що має широке використання,

є

D-тригер

з одним

входом. D-тригер

запам’ятовує стан входу і видає його

на вихід. D-тригери

мають, як мінімум, два входи: інформаційний

вхід D

і вхід синхронізації С.

Найпростіший варіант побудови

двотактного D-тригера

показаний на рис. 4.55-а (його умовне

позначення – на рис. 4.55-б). У деякий

момент дискретного часу t

під дією синхросигналу

С інформація, що

надходить

на вхід D,

приймається в RS-тригер,

але на виході Q

з’являється

із затримкою на час дії синхросигналу,

оскільки RS-тригер

двотактний, тобто Q(t + 1) = D(t).

Отже D-тригер

може використовуватись як синхронний

елемент затримки на один такт (на час

дії одного синхросигналу). Часова

діаграма, що ілюструє роботу D-тригера,

наведена на рис. 4.56.

дним

з

інтегральних тригерів,

що має широке використання,

є

D-тригер

з одним

входом. D-тригер

запам’ятовує стан входу і видає його

на вихід. D-тригери

мають, як мінімум, два входи: інформаційний

вхід D

і вхід синхронізації С.

Найпростіший варіант побудови

двотактного D-тригера

показаний на рис. 4.55-а (його умовне

позначення – на рис. 4.55-б). У деякий

момент дискретного часу t

під дією синхросигналу

С інформація, що

надходить

на вхід D,

приймається в RS-тригер,

але на виході Q

з’являється

із затримкою на час дії синхросигналу,

оскільки RS-тригер

двотактний, тобто Q(t + 1) = D(t).

Отже D-тригер

може використовуватись як синхронний

елемент затримки на один такт (на час

дії одного синхросигналу). Часова

діаграма, що ілюструє роботу D-тригера,

наведена на рис. 4.56.

Рис. 4.56.

Особливістю схеми D-тригера є те, що на вхід безпосередньо RS-тригера інформація подається в парафазному коді, хоча на вхід D подається тільки пряме значення. Парафазний код утворюється штучно, за допомогою інвертора, що знаходиться в колі входу R, причому пряме значення подається на вхід S, а інвертоване – на вхід R, що забезпечую сприймання D-тригером як «нульового» сигналу, так і «одиничного».

D-тригер відповідає RS-тригеру, що працює тільки в режимі встановлення і зберігання, тобто або з комбінаціями сигналів R = 1 і S = 0, або з комбінаціями сигналів R = 0 і S = 1. Для керування зберіганням інформації використовується вхід С (режим занесення: С = 1; режим зберігання: С = 0). Режими «Встановлення в 1» і «Скидання в 0» відсутні.

4.6.1.5. JK-тригер.

Оскільки конструктору обчислювальної техніки можуть знадобитися тригери всіх трьох типів в тих чи інших кількостях, вигідніше виготовляти один тип універсального тригера, який можна використовувати як RS-, Т- або D-тригер. Розповсюдженим типом такого тригера в системах інтегральних логічних елементів є універсальний двотактний JK-тригер (рис. 4.57-а, -б).

а) б)

Рис. 4.57.

Входи J (від англ. Jump − стрибок) і K (від англ. Kill − вбити) відповідають входам S і R RS-тригера, тобто сигнал 1 на вході J встановлює тригер в стан 1, а сигнал 1 на вході K встановлює його в стан 0 незалежно від попереднього стану. Але на відміну від RS-тригера в JK-тригері сигнали 1 можуть одночасно прийти на входи J і K. При цьому стан тригера завжди буде змінюватись на протилежний, тобто при J = K = 1 схема поводить себе як Т-тригер з лічильним входом.

Якщо

на входах R і

S RS-тригера

поставити схеми 2І,

що керуються виходами тригера Q

і

і

вхідними сигналами K

і J

в рівняння RS-тригера

(див. початок ч. 2, п. 4.6.1) замість S(t)

доведеться підставити

![]() ,

а замість

,

а замість

![]() −

−

![]() .

Після відповідних спрощень (див. ч. 2, п.

4.3.6) отримується рівняння нового тригера:

.

Після відповідних спрощень (див. ч. 2, п.

4.3.6) отримується рівняння нового тригера:

![]() ,

при

=

=1

(тобто сигнали на несинхронізованих

входах не впливають на стан тригера).

,

при

=

=1

(тобто сигнали на несинхронізованих

входах не впливають на стан тригера).

Сигнали J і K можуть бути результатом кон’юнкції кількох сигналів J = J1 J2 J3 і K = K1 K2 K3. Крім того тригер має входи несинхронізованого встановлення і , за допомогою яких при С = 0 тригер можна встановити в стан 1 через подачу сигналів = 1, = 0 або в стан 0 через подачу сигналів = 0, = 1.

Функціонування JK–тригера може бути описано таблицею переходів. Наводиться таблиця переходів (табл. 4.12) при = =1 під дією синхронізованих входів (С = 1).

JK-тригер зручний тим, що при різних варіантах підключення його входів можна отримати схеми, що функціонують як D-, T- і RS-тригери.

Таблиця 4.12.

Таблиця переходів JK-тригера.

t |

t + 1 |

Коментар |

|

J |

K |

Q |

|

0 |

0 |

Q(t) |

Зберігання 0 або 1 |

0 |

1 |

0 |

Встановлення 1 |

1 |

0 |

1 |

Встановлення 0 |

1 |

1 |

|

Інверсія стану |

Дійсно,

якщо об’єднати входи J

і К

і позначити їх Т,

то JK-тригер

перетворюється в Т-тригер

(рис. 4.58-а – синхронний Т-тригер;

рис. 4.58-б − асинхронний Т-тригер).

Його рівняння:

![]()

а) б) в) г)

Рис. 4.58.

Інша

трансформація (рис. 4.58-в), яка забезпечує

те, що при подачі на вхід J

сигналу D,

а на вхід К

– сигналу

![]() перетворює JK-тригер

в D-тригер.

Його рівняння:

перетворює JK-тригер

в D-тригер.

Його рівняння:

![]() .

.

Пряма подача на вхід J сигналу S, а на вхід К сигналу R змушує працювати JK-тригер як RS-тригер (рис. 4.58-г).