- •Вступ 6 зм 1. Електричні властивості напівпровідників 9

- •Зм 2. Напівпровідникові прилади 26

- •Зм 3. Електронні пристрої 79

- •Зм 4. Електронні елементи мікропроцесорної техніки 164

- •Зм 1. Електричні властивості напівпровідників

- •1.1. Основи зонної теорії твердого тіла.

- •1.2. Електропровідність напівпровідників.

- •1.2.1. Власна електропровідність напівпровідників

- •1.2.2. Домішкова електропровідність напівпровідників

- •1 .2.3. Ефекти, що пов’язані з електропровідністю напівпровідників

- •1.3. Властивості електронно-діркового переходу.

- •1.3.1. Формування електронно-діркового переходу.

- •1.3.2. Властивості n-p переходу при підключенні зовнішньої напруги

- •1.3.3. Тунельний ефект

- •1.4. Питання для самоперевірки.

- •Зм 2. Напівпровідникові прилади

- •2.1. Напівпровідникові діоди1

- •2.1.1. Випрямляючі діоди

- •2.1.2. Стабілітрони і схеми стабілізації напруги.

- •2.1.3. Варикапи

- •2.1.4. Тунельні діоди

- •2.1.5. Інші види діодів

- •2.2. Біполярні транзистори і їх використання в електронних пристроях

- •2.2.1. Устрій та принцип роботи біполярного транзистора.

- •2.2.2. Режими роботи біполярного транзистора.

- •2.2.3. Схеми включення транзисторів.

- •2.2.4. Вольт-амперні характеристики біполярних транзисторів та режими роботи (на прикладі n-p-n транзисторів).

- •2.2.5. Транзистор як активний чотирьохполюсник.

- •2.3. Уніполярні транзистори.

- •2.4. Тиристори

- •2.5. Питання для самоперевірки.

- •Зм 3. Електронні пристрої

- •3.1. Випрямлячі змінного струму.

- •3.2. Підсилювачі електричних сигналів.

- •3.2.1. Загальна інформація.

- •3.2.2. Характеристики підсилювачів

- •3.2.3. Зворотний зв’язок в підсилювачах.

- •3.2.4. Схеми підсилювальних каскадів на біполярних транзисторах.

- •3.2.5. Особливості роботи схеми попередніх каскадів підсилювача.

- •3.2.6. Режими роботи підсилюючих елементів.

- •3.2.7. Особливості роботи схеми кінцевого каскаду підсилювача.

- •3.2.8. Складені транзистори.

- •3.2.9. Спеціальні види підсилювачів.

- •3.3. Транзисторні генератори електричних сигналів.

- •3.3.1. Генератори синусоїдальних коливань.

- •3.3.2. Генератори імпульсів складної форми.

- •3.3.2.1. Параметри імпульсів прямокутної форми.

- •3.3.2.2. Мультивібратори.

- •3.3.2.3. Очікуючий мультивібратор або одновібратор.

- •3.3.2.4. Блокінг-генератори.

- •3.3.2.5. Генератори пилкоподібної напруги (гпн).

- •3.3.3. Генератори сигналів на операційних підсилювачах1.

- •3.4. Питання для самоперевірки.

- •Зм 4. Електронні елементи мікропроцесорної техніки

- •4.1. Уявлення про мікропроцесорну техніку, мікропроцесорні засоби і мікропроцесорні системи.

- •4.2. Структура мікропроцесорної системи.

- •4.2.1. Загальне уявлення про мікропроцесорну систему.

- •4.2.2. Мікропроцесорні засоби в системах керування

- •4.3. Елементи математичного апарату цифрової техніки.

- •4.3.1. Системи числення.

- •4.3.2. Фізичне уявлення інформації в мп-системі.

- •4.3.3. Форми представлення чисел.

- •4.3.4. Кодування чисел в мп-системах

- •4.3.5. Поняття булевої змінної та булевої функції

- •4.3.6. Операції та закони булевої алгебри.

- •4.3.7. Функціонально повні системи булевих функцій.

- •4.3.8. Мінімізація булевих функцій.

- •4.4. Цифрові схеми та цифрові автомати.

- •4.4.1. Елементи ртл.

- •4.4.2. Елементи дтл.

- •4.4.3. Елементи ттл.

- •4.4.4. Елементи езл.

- •4.4.5. Інтегральні схеми на моп–транзисторах.

- •4.5. Комбінаційні цифрові пристрої.

- •4.5.1 Дешифратор.

- •4.5.2. Перетворювачі кодів і шифратори.

- •4.5.3. Мультиплексори і демультиплексори.

- •4.5.4. Напівсуматор і суматор.

- •4.6. Послідовнісні пристрої.

- •4.6.1. Тригери.

- •4.6.1.1. Синхронний однотактний rs–тригер.

- •4.6.1.2. Синхронний двотактний rs–тригер.

- •4.6.2. Регістри.

- •4.6.2.1. Прийом і передача інформації в регістрах.

- •4.6.2.2. Схемна реалізація зсуваючого регістру

- •4.6.2.3. Реалізація порозрядних операцій в регістрах.

- •4.6.3. Лічильники.

- •4.6.3.1. Загальне уявлення і класифікація.

- •4.6.3.2. Лічильник з безпосередніми зв’язками з послідовним переносом.

- •4.6.3.3. Лічильник з паралельним переносом.

- •4.6.3.4. Реверсивний лічильник з послідовним переносом.

- •4.6.4. Накопичуючі суматори.

- •4.6.4.1. Однорозрядний накопичуючий суматор.

- •4.6.4.2. Багаторозрядні суматори

- •4.6.5. Електронні елементи пам’яті.

- •4.6.6. Перетворювачі сигналів.

- •4.7. Питання для самоперевірки.

- •Додаток

- •Префікси для кратних одиниць

- •Список рекомендованої літератури

4.4.2. Елементи дтл.

Діодно-транзисторна логіка (ДТЛ) − це технологія побудови цифрових схем на основі біполярних транзисторів, діодів і резисторів. Свою назву технологія отримала завдяки реалізації логічних функцій (наприклад, І) за допомогою діодних кіл, а посилення сигналу − за допомогою транзистора.

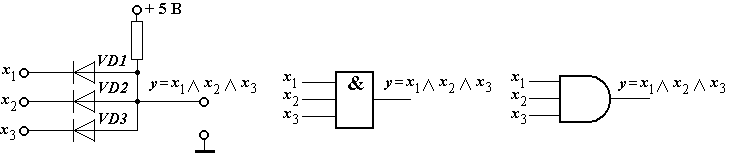

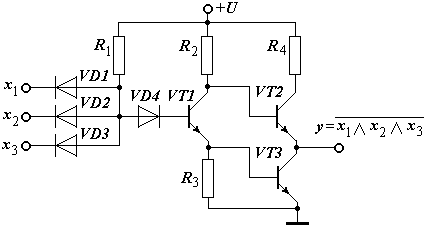

Приклад комбінаційної схеми (а), що реалізує функцію 3І (кон’юнкцію) тобто y = f(x 1, x 2 , x 3 ) = x 1 x 2 x 3 , і її умовні позначення в системах DIN (б) та ANSI (в) наведені на рис. 4.19.

а) б) в)

Рис. 4.19.

О перація

кон’юнкції в цій схемі здійснюється

за допомогою діодів. Якщо на входи

x 1 x 3

схеми подати високу напругу, що відповідає

логічній 1, то діоди VD1÷VD3

будуть закриті, струм

через них проходити не буде і на виході

схеми буде висока напруга (близька до

напруги живлення), яка відповідає

логічній 1. Якщо хоча б на одному з входів

цієї схеми буде низька напруга, яка

відповідає логічному 0, то струм від

джерела живлення +U

пройде через резистор, утворюючи на

ньому падіння напруги, і

через відкритий діод;

напруга на виході цієї схеми буде

відповідати логічному 0. Тобто схема

реалізує функцію 3І.

перація

кон’юнкції в цій схемі здійснюється

за допомогою діодів. Якщо на входи

x 1 x 3

схеми подати високу напругу, що відповідає

логічній 1, то діоди VD1÷VD3

будуть закриті, струм

через них проходити не буде і на виході

схеми буде висока напруга (близька до

напруги живлення), яка відповідає

логічній 1. Якщо хоча б на одному з входів

цієї схеми буде низька напруга, яка

відповідає логічному 0, то струм від

джерела живлення +U

пройде через резистор, утворюючи на

ньому падіння напруги, і

через відкритий діод;

напруга на виході цієї схеми буде

відповідати логічному 0. Тобто схема

реалізує функцію 3І.

Аналогічна схема виконує функцію 3АБО (рис.4.20).

Кількість входів елемента І залежить від кількості діодів. Якщо використовувати два діоди, то вийде елемент 2І, якщо три діода − то 3І, якщо чотири діода, то 4І, і так далі. У мікросхемах випускається максимальний елемент 8І.

Н аведена

схема має такий недолік, як зміщення

логічних рівнів на виході мікросхеми.

Напруга нуля і напруга одиниці на виході

схеми вище вхідних рівнів на 0,7 В. Це

викликано падінням напруги на вхідних

діодах. Компенсувати це зміщення рівнів

можна діодом, включеному на виході

схеми, як це показано на рис. 4.21.

аведена

схема має такий недолік, як зміщення

логічних рівнів на виході мікросхеми.

Напруга нуля і напруга одиниці на виході

схеми вище вхідних рівнів на 0,7 В. Це

викликано падінням напруги на вхідних

діодах. Компенсувати це зміщення рівнів

можна діодом, включеному на виході

схеми, як це показано на рис. 4.21.

У цій схемі логічні рівні на вході і виході схеми однакові. Більш того, схема на рис. 4.21 буде нечутлива не тільки до вхідних напруг, більшим за напругу живлення схеми, а й до від'ємних вхідних напруг. Діоди витримують напругу до сотень вольт. Тому така схема досі використовується для захисту цифрових пристроїв від перевантажень по напрузі, що виникають, наприклад, в колах за межами пристрою. Природно, що для захисту одного входу досить одного діода на вході елемента. У результаті виходить тільки схема захисту без функції І.

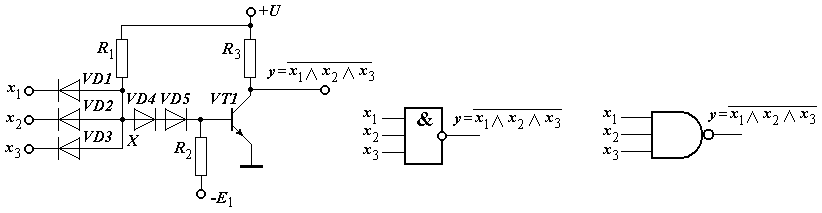

При

з’єднанні вхідної діодної схеми 3І

з вихідним транзисторним інвертором

утворюється одна з найпростіших логічних

мікросхем, що реалізує функцію 3І−НЕ,

тобто y = f(x) = ![]() .

Схема логічного елемента 3І–НЕ

(а) та її умовні позначення в системах

DIN (б) та ANSI (в) показані на рис. 4.22. Діоди

VD4, VD5

і коло зміщення R2,

−Е1

введені для забезпечення працездатності

і збільшення завадостійкості схеми при

рівні логічного нуля на вході.

.

Схема логічного елемента 3І–НЕ

(а) та її умовні позначення в системах

DIN (б) та ANSI (в) показані на рис. 4.22. Діоди

VD4, VD5

і коло зміщення R2,

−Е1

введені для забезпечення працездатності

і збільшення завадостійкості схеми при

рівні логічного нуля на вході.

а) б) в)

Рис. 4.22.

Вважаємо що вхід такого логічного елементу підключений до виходу такого ж логічного елемента. Паспортні дані на такі ДТЛ мікросхеми: U<0>вих.max = 0,5 В; пряме падіння на вхідному діоді Uпр.д.max = 0,9 B. Отже при логічному нулі на виході попереднього логічного елемента і, відповідно, на вході даного логічного елементу напруга після вхідного діода в точці Х з’єднання анодів вхідних діодів може бути наступним:

U<0>X = U<0>вых.max + Uпр.д.max = 0,5 + 0,9 = 1,4 B.

Якщо б не було діодів VD4 і VD5, то напруга логічного нуля U<0>X в точці Х, безпосередньо потрапляючи на базу вихідного транзистора, могла б бути занадто високою, щоб цей транзистор закрити, тобто може бути так, що вихідний транзистор не буде закриватися ні при логічній одиниці ні при логічному нулі на його вході.

За наявності діодів VD4, VD5 та кола зміщення R2, −Е1, струм, що протікає від точки Х через діоди VD4 і VD5 і резистор R2 до джерела зміщення −Е1, створює на цих діодах падіння напруги, яке дорівнює подвійному Uпр.д.max, тобто Uпр. = 1,8 В. Напруга на базі транзистора Uб при логічному нулі вході при цьому буде нижче напруги в точці Х на величину падіння напруги на відкритих діодах VD4 і VD5 (виходячи з напрямку струму в діодах), тобто Uб = UX – 2×Uпр.д.max = 1,4 – 1,8 = – 0,4 В.

Оскільки для початку відкривання транзистора n-n-p необхідна додатна напруга хоча б 0,1 В, можна вважати, що у даної мікросхеми статична завадостійкість складе U<0>завад. = 0,1 − (− 0,4) = 0,5 В.

Головні недоліки таких схем:

a) низька навантажувальна здатність Крозг. = 51;

б) низька швидкодія: t0, 1затр. = 110 нс, t1, 0затр. = 20 нс. Велика різниця між затримками по фронтах при переході від «0» до «1» і від «1» до «0» пояснюється тим, що заряд ємності навантаження логічного елемента при закриванні вихідного транзистора (фронт 0,1) відбувається через колекторний резистор R3 = 4 Ком, а розряд, − через відкритий транзистор,що має істотно менше внутрішній опір Rвідкр., ніж R3.

Удосконалення мікросхем ДТЛ шляхом ускладнення вихідного інвертора, як показано на рис. 4.23, дозволило збільшити навантажувальну здатність (Kрозг. = 16) і швидкодію (t0, 1затр. = t1, 0затр. = 40 нс).

Рис. 4.23.

У цій схемі вихідні транзистори VT2 та VT3 зібрані за двотактною схемою (push-pull, − «тягни-штовхай»). Вони відкриваються по черзі. Транзистор VT1 називають фазороздільним. Низькоомний резистор R4 обмежує імпульс струму, що протікає через транзистори VT2 та VT3 при перемиканні, коли один з цих транзисторів відкривається, а другий, − закривається.

Для аналізу роботи такого вихідного каскаду можна використати наступний прийом, − допустити, що в одному випадку (при логічній одиниці на всіх входах х1, х2, х3) фазоінвертуючий транзистор відкритий і являє собою коротке замикання між колектором і емітером, а в іншому стані цей транзистор закритий і являє собою розрив.

У першому випадку очевидно, що якщо не враховувати вплив верхнього вихідного транзистора, то нижній вихідний транзистор VT3 буде відкрито. При цьому напруга на його колекторі буде вище рівня нуля (хоча б на частку вольта), отже і потенціал емітера верхнього вихідного транзистора буде вище рівня нуля, вище рівня емітера нижнього вихідного транзистора.

Тому можна вважати, що для верхнього вихідного транзистора напруги на його базі буде недостатньо для його відкриття, хоча цієї напруги і вистачає для відкривання нижнього вихідного транзистора. Отже, верхній вихідний транзистор буде закрито, і не буде впливати на роботу нижнього вихідного транзистора, що підтверджує правильність зробленого вище припущення.

Таким чином, при логічних одиницях на всіх входах ДТЛ логічний елемент має на своєму виході напруга логічного нуля.

У другому випадку, очевидно, що верхній

вихідний транзистор буде відкритий, а

нижній вихідний транзистор, − закритий.

другому випадку, очевидно, що верхній

вихідний транзистор буде відкритий, а

нижній вихідний транзистор, − закритий.

Отже, при хоча б одному логічному нулі на входах схеми логічний елемент має на своєму виході напруга логічної одиниці.

На основі базового елементу будується і інвертор. У цьому випадку на вході використовується тільки один діод VD1. Схема ДТЛ інвертора наведена на рис. 4.24.

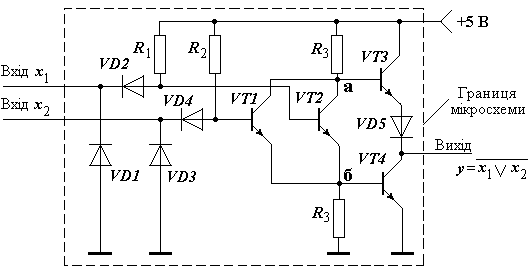

До складу сучасних серій мікросхем крім елементів І входять логічні елементи АБО. Схема логічного елемента 2АБО-НЕ наведена на рис. 4.25. Транзистори VT1, VT2, що реалізують функцію АБО, з’єднуються паралельно в точках а і б, а вихідний каскад на транзисторах VT3, VT4 − один.

Рис. 4. 25.

Наведений на рис. 4.25 логічний елемент використовується в таких серіях мікросхем як 555, 533, 1531, 1533. У цих серіях мікросхем для підвищення швидкодії застосовуються транзистори і діоди Шотткі. Схеми АБО-НЕ у цих серіях мікросхем має позначення «ЛЕ». Так наприклад, схема К555ЛЕ1 містить в одному корпусі чотири елемента 2АБО-НЕ.