- •Вступ 6 зм 1. Електричні властивості напівпровідників 9

- •Зм 2. Напівпровідникові прилади 26

- •Зм 3. Електронні пристрої 79

- •Зм 4. Електронні елементи мікропроцесорної техніки 164

- •Зм 1. Електричні властивості напівпровідників

- •1.1. Основи зонної теорії твердого тіла.

- •1.2. Електропровідність напівпровідників.

- •1.2.1. Власна електропровідність напівпровідників

- •1.2.2. Домішкова електропровідність напівпровідників

- •1 .2.3. Ефекти, що пов’язані з електропровідністю напівпровідників

- •1.3. Властивості електронно-діркового переходу.

- •1.3.1. Формування електронно-діркового переходу.

- •1.3.2. Властивості n-p переходу при підключенні зовнішньої напруги

- •1.3.3. Тунельний ефект

- •1.4. Питання для самоперевірки.

- •Зм 2. Напівпровідникові прилади

- •2.1. Напівпровідникові діоди1

- •2.1.1. Випрямляючі діоди

- •2.1.2. Стабілітрони і схеми стабілізації напруги.

- •2.1.3. Варикапи

- •2.1.4. Тунельні діоди

- •2.1.5. Інші види діодів

- •2.2. Біполярні транзистори і їх використання в електронних пристроях

- •2.2.1. Устрій та принцип роботи біполярного транзистора.

- •2.2.2. Режими роботи біполярного транзистора.

- •2.2.3. Схеми включення транзисторів.

- •2.2.4. Вольт-амперні характеристики біполярних транзисторів та режими роботи (на прикладі n-p-n транзисторів).

- •2.2.5. Транзистор як активний чотирьохполюсник.

- •2.3. Уніполярні транзистори.

- •2.4. Тиристори

- •2.5. Питання для самоперевірки.

- •Зм 3. Електронні пристрої

- •3.1. Випрямлячі змінного струму.

- •3.2. Підсилювачі електричних сигналів.

- •3.2.1. Загальна інформація.

- •3.2.2. Характеристики підсилювачів

- •3.2.3. Зворотний зв’язок в підсилювачах.

- •3.2.4. Схеми підсилювальних каскадів на біполярних транзисторах.

- •3.2.5. Особливості роботи схеми попередніх каскадів підсилювача.

- •3.2.6. Режими роботи підсилюючих елементів.

- •3.2.7. Особливості роботи схеми кінцевого каскаду підсилювача.

- •3.2.8. Складені транзистори.

- •3.2.9. Спеціальні види підсилювачів.

- •3.3. Транзисторні генератори електричних сигналів.

- •3.3.1. Генератори синусоїдальних коливань.

- •3.3.2. Генератори імпульсів складної форми.

- •3.3.2.1. Параметри імпульсів прямокутної форми.

- •3.3.2.2. Мультивібратори.

- •3.3.2.3. Очікуючий мультивібратор або одновібратор.

- •3.3.2.4. Блокінг-генератори.

- •3.3.2.5. Генератори пилкоподібної напруги (гпн).

- •3.3.3. Генератори сигналів на операційних підсилювачах1.

- •3.4. Питання для самоперевірки.

- •Зм 4. Електронні елементи мікропроцесорної техніки

- •4.1. Уявлення про мікропроцесорну техніку, мікропроцесорні засоби і мікропроцесорні системи.

- •4.2. Структура мікропроцесорної системи.

- •4.2.1. Загальне уявлення про мікропроцесорну систему.

- •4.2.2. Мікропроцесорні засоби в системах керування

- •4.3. Елементи математичного апарату цифрової техніки.

- •4.3.1. Системи числення.

- •4.3.2. Фізичне уявлення інформації в мп-системі.

- •4.3.3. Форми представлення чисел.

- •4.3.4. Кодування чисел в мп-системах

- •4.3.5. Поняття булевої змінної та булевої функції

- •4.3.6. Операції та закони булевої алгебри.

- •4.3.7. Функціонально повні системи булевих функцій.

- •4.3.8. Мінімізація булевих функцій.

- •4.4. Цифрові схеми та цифрові автомати.

- •4.4.1. Елементи ртл.

- •4.4.2. Елементи дтл.

- •4.4.3. Елементи ттл.

- •4.4.4. Елементи езл.

- •4.4.5. Інтегральні схеми на моп–транзисторах.

- •4.5. Комбінаційні цифрові пристрої.

- •4.5.1 Дешифратор.

- •4.5.2. Перетворювачі кодів і шифратори.

- •4.5.3. Мультиплексори і демультиплексори.

- •4.5.4. Напівсуматор і суматор.

- •4.6. Послідовнісні пристрої.

- •4.6.1. Тригери.

- •4.6.1.1. Синхронний однотактний rs–тригер.

- •4.6.1.2. Синхронний двотактний rs–тригер.

- •4.6.2. Регістри.

- •4.6.2.1. Прийом і передача інформації в регістрах.

- •4.6.2.2. Схемна реалізація зсуваючого регістру

- •4.6.2.3. Реалізація порозрядних операцій в регістрах.

- •4.6.3. Лічильники.

- •4.6.3.1. Загальне уявлення і класифікація.

- •4.6.3.2. Лічильник з безпосередніми зв’язками з послідовним переносом.

- •4.6.3.3. Лічильник з паралельним переносом.

- •4.6.3.4. Реверсивний лічильник з послідовним переносом.

- •4.6.4. Накопичуючі суматори.

- •4.6.4.1. Однорозрядний накопичуючий суматор.

- •4.6.4.2. Багаторозрядні суматори

- •4.6.5. Електронні елементи пам’яті.

- •4.6.6. Перетворювачі сигналів.

- •4.7. Питання для самоперевірки.

- •Додаток

- •Префікси для кратних одиниць

- •Список рекомендованої літератури

4.4.5. Інтегральні схеми на моп–транзисторах.

Інтегральні схеми на МОН–транзисторах (метал–оксид–напівпровідник) мають нижчу швидкодію, ніж елементи ТТЛ- або ЕЗЛ–типу. Однак ці елементи відрізняються меншою потужністю споживання, більшою навантажувальною здатністю і завадостійкістю, потребують меншу площу на поверхні ІС, дешевше елементів ТТЛ- і ЕЗЛ–типу. Тому вони широко застосовуються, особливо в цифрових пристроях невисокої швидкодії або в пристроях, для яких важлива висока ступінь інтеграції.

В основі роботи МОН–транзисторів лежить ефект керування полем (польові транзистори – див. ч. 2, п. 2.3). За принципом дії вони є аналогами електронних ламп, оскільки керуються напругою, а не струмом. МОН–транзистори бувають n- і p–типу.

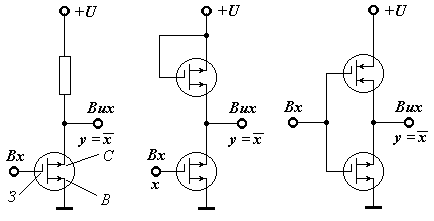

На рис. 4.30 наведені схеми інвертора на МОН–тразисторі n–типу: а) – з навантажувальним резистором, б) – з навантажувальним транзистором n–типу, в) – з навантажувальним транзистором p–типу. Виток В транзистора виконує тут роль, схожу з роллю емітера в транзисторах. До затвору З (входу схеми) прикладається керуюча напруга, стік С є виходом схеми. При зміні напруги на затворі З змінюється опір між витоком В і стоком С (від сотень Ом до сотень мОм), що призводить до зміни струму, який протікає через транзистор, і вихідної напруги схеми. При надходженні на затвор З сигналу високої напруги, опір між витоком В і стоком С падає і на виході встановлюється низька напруга. При надходженні на вхід сигналу низького рівня опір транзистора стає дуже великим і на виході встановлюється висока напруга. Як навантажувальний опір в схемах на МОН–транзисторах технологічно зручно використовувати МОН–транзистор, на затвор З якого подається напруга, що ставить його в режим відкритого транзистора (рис. 4.30-б).

а) б) в)

Рис. 4.30.

Поряд з навантажувальним резистором в схемах на МОН–транзисторах використовуються МОН–транзистори p–типу, живлення яких і керування проводиться від’ємними напругами. Інвертор з транзисторами n- і p–типів наведений на рис. 4.30-в. Тут при надходженні на вхід високої напруги відкривається нижній транзистор, а верхній закривається, і, навпаки, при надходженні на вхід низької напруги відкривається верхній транзистор, а нижній закривається.

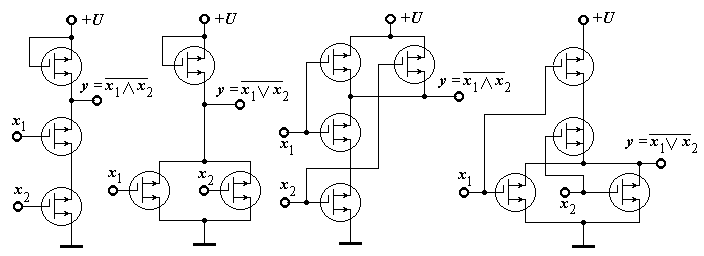

а) б) в) г)

Рис. 4.31.

Схеми з доповнюючими транзисторами (комплементарні схеми) відрізняються малою потужністю споживання і більш високою швидкодією, оскільки в колах заряду і розряду паразитних ємностей виявляються включеними малі опори відкритих транзисторів.

Схеми, що реалізують функції І або АБО, будуються відповідно послідовним і паралельним включенням МОН–транзисторів. При цьому звичайно на виході схеми отримуються функції І – НЕ або АБО – НЕ. На рис. 4.31 показані: а) – елемент І–НЕ з навантажувальним транзистором; б) – елемент АБО–НЕ з навантажувальним транзистором; в) – елемент І–НЕ з доповнюючими транзисторами; г) – елемент АБО–НЕ з доповнюючими транзисторами.