- •Вступ 6 зм 1. Електричні властивості напівпровідників 9

- •Зм 2. Напівпровідникові прилади 26

- •Зм 3. Електронні пристрої 79

- •Зм 4. Електронні елементи мікропроцесорної техніки 164

- •Зм 1. Електричні властивості напівпровідників

- •1.1. Основи зонної теорії твердого тіла.

- •1.2. Електропровідність напівпровідників.

- •1.2.1. Власна електропровідність напівпровідників

- •1.2.2. Домішкова електропровідність напівпровідників

- •1 .2.3. Ефекти, що пов’язані з електропровідністю напівпровідників

- •1.3. Властивості електронно-діркового переходу.

- •1.3.1. Формування електронно-діркового переходу.

- •1.3.2. Властивості n-p переходу при підключенні зовнішньої напруги

- •1.3.3. Тунельний ефект

- •1.4. Питання для самоперевірки.

- •Зм 2. Напівпровідникові прилади

- •2.1. Напівпровідникові діоди1

- •2.1.1. Випрямляючі діоди

- •2.1.2. Стабілітрони і схеми стабілізації напруги.

- •2.1.3. Варикапи

- •2.1.4. Тунельні діоди

- •2.1.5. Інші види діодів

- •2.2. Біполярні транзистори і їх використання в електронних пристроях

- •2.2.1. Устрій та принцип роботи біполярного транзистора.

- •2.2.2. Режими роботи біполярного транзистора.

- •2.2.3. Схеми включення транзисторів.

- •2.2.4. Вольт-амперні характеристики біполярних транзисторів та режими роботи (на прикладі n-p-n транзисторів).

- •2.2.5. Транзистор як активний чотирьохполюсник.

- •2.3. Уніполярні транзистори.

- •2.4. Тиристори

- •2.5. Питання для самоперевірки.

- •Зм 3. Електронні пристрої

- •3.1. Випрямлячі змінного струму.

- •3.2. Підсилювачі електричних сигналів.

- •3.2.1. Загальна інформація.

- •3.2.2. Характеристики підсилювачів

- •3.2.3. Зворотний зв’язок в підсилювачах.

- •3.2.4. Схеми підсилювальних каскадів на біполярних транзисторах.

- •3.2.5. Особливості роботи схеми попередніх каскадів підсилювача.

- •3.2.6. Режими роботи підсилюючих елементів.

- •3.2.7. Особливості роботи схеми кінцевого каскаду підсилювача.

- •3.2.8. Складені транзистори.

- •3.2.9. Спеціальні види підсилювачів.

- •3.3. Транзисторні генератори електричних сигналів.

- •3.3.1. Генератори синусоїдальних коливань.

- •3.3.2. Генератори імпульсів складної форми.

- •3.3.2.1. Параметри імпульсів прямокутної форми.

- •3.3.2.2. Мультивібратори.

- •3.3.2.3. Очікуючий мультивібратор або одновібратор.

- •3.3.2.4. Блокінг-генератори.

- •3.3.2.5. Генератори пилкоподібної напруги (гпн).

- •3.3.3. Генератори сигналів на операційних підсилювачах1.

- •3.4. Питання для самоперевірки.

- •Зм 4. Електронні елементи мікропроцесорної техніки

- •4.1. Уявлення про мікропроцесорну техніку, мікропроцесорні засоби і мікропроцесорні системи.

- •4.2. Структура мікропроцесорної системи.

- •4.2.1. Загальне уявлення про мікропроцесорну систему.

- •4.2.2. Мікропроцесорні засоби в системах керування

- •4.3. Елементи математичного апарату цифрової техніки.

- •4.3.1. Системи числення.

- •4.3.2. Фізичне уявлення інформації в мп-системі.

- •4.3.3. Форми представлення чисел.

- •4.3.4. Кодування чисел в мп-системах

- •4.3.5. Поняття булевої змінної та булевої функції

- •4.3.6. Операції та закони булевої алгебри.

- •4.3.7. Функціонально повні системи булевих функцій.

- •4.3.8. Мінімізація булевих функцій.

- •4.4. Цифрові схеми та цифрові автомати.

- •4.4.1. Елементи ртл.

- •4.4.2. Елементи дтл.

- •4.4.3. Елементи ттл.

- •4.4.4. Елементи езл.

- •4.4.5. Інтегральні схеми на моп–транзисторах.

- •4.5. Комбінаційні цифрові пристрої.

- •4.5.1 Дешифратор.

- •4.5.2. Перетворювачі кодів і шифратори.

- •4.5.3. Мультиплексори і демультиплексори.

- •4.5.4. Напівсуматор і суматор.

- •4.6. Послідовнісні пристрої.

- •4.6.1. Тригери.

- •4.6.1.1. Синхронний однотактний rs–тригер.

- •4.6.1.2. Синхронний двотактний rs–тригер.

- •4.6.2. Регістри.

- •4.6.2.1. Прийом і передача інформації в регістрах.

- •4.6.2.2. Схемна реалізація зсуваючого регістру

- •4.6.2.3. Реалізація порозрядних операцій в регістрах.

- •4.6.3. Лічильники.

- •4.6.3.1. Загальне уявлення і класифікація.

- •4.6.3.2. Лічильник з безпосередніми зв’язками з послідовним переносом.

- •4.6.3.3. Лічильник з паралельним переносом.

- •4.6.3.4. Реверсивний лічильник з послідовним переносом.

- •4.6.4. Накопичуючі суматори.

- •4.6.4.1. Однорозрядний накопичуючий суматор.

- •4.6.4.2. Багаторозрядні суматори

- •4.6.5. Електронні елементи пам’яті.

- •4.6.6. Перетворювачі сигналів.

- •4.7. Питання для самоперевірки.

- •Додаток

- •Префікси для кратних одиниць

- •Список рекомендованої літератури

4.3.7. Функціонально повні системи булевих функцій.

Система булевих функцій називається функціонально повною, якщо для будь-якого булевого виразу знайдеться булевий вираз, який дорівнює даному, і містить лише функції з зазначеної системи.

Іншими словами, система булевих функцій називається функціонально повною, якщо будь-яку булеву функцію можна виразити за допомогою функцій, які входять до складу цієї системи.

Відомо досить багато функціонально повних систем булевих функцій. Фундаментальна теорема Поста, яка вивчається в курсі дискретної математики, встановлює необхідні і достатні умови функціональної повноти. Найбільш відомою і вживаною функціонально повною системою є система, що складається з трьох функцій: кон’юнкції, диз’юнкції та заперечення. Особливе місце цього набору пов’язано з тим, що існує простий стандартний алгоритм вираження будь-якої булевої функції за допомогою цих трьох функцій; алгоритм полягає у побудові на основі таблиці істинності досконалої диз’юнктивної нормальної форми (ДДНФ).

Можна навести інші приклади функціонально повних систем, такі як:

кон’юнкція та заперечення;

диз’юнкція та заперечення;

тотожний 0, тотожна 1, кон’юнкція, додавання за модулем 2;

імплікація та тотожний 0.

Існують функціонально повні набори, кожний з яких містить єдину функцію. Такими функціями є штрих Шефера та стрілка Пірса.

Вираження довільного булевого виразу через кон’юнкцію, диз’юнкцію та заперечення. Система булевих функцій, яка містить кон’юнкцію, диз’юнкцію та заперечення, як зазначалось, є функціонально повною, і існує загальновживаний (хоч і не завжди оптимальний з точки зору часу виконання) алгоритм представлення будь-якого булевого виразу через ці функції. Алгоритм складається з двох частин:

Побудова таблиці істинності для заданого виразу.

Побудова за таблицею істинності так званої досконалої диз’юнктивної (або кон’юнктивної) нормальної форми.

Якщо функція вже задана таблицею істинності, перший етап автоматично відпадає, і залишається тільки другий.

Елементарною кон’юнкцією називається кон’юнкція булевих змінних, кожна з яких може стояти під знаком заперечення.

Булевий вираз записаний у диз’юнктивній нормальній формі (ДНФ), якщо він являє собою диз’юнкцію елементарних кон’юнкцій.

Диз’юнктивна нормальна форма від n змінних називається досконалою (ДДНФ), якщо кожна елементарна кон’юнкція включає всі змінні, можливо із запереченням.

Зазначимо, що крім диз’юнктивних нормальних форм, широко застосовуються нормальні форми іншого типу – кон’юнктивні.

Кон’юнктивною нормальною формою (КНФ) називається логічний добуток елементарних диз’юнкцій, в кожну з яких аргумент або його заперечення входять один раз. КНФ може бути отримана з таблиці істинності: для кожного набору аргументів на якому функція рівна «0» складають елементарну суму, причому змінні, значення яких рівне «1», записуються із запереченням. Отримані суми, які носять назву констітуент нуля, або макстермів, об’єднують операцією логічного множення. КНФ також називається досконалою (ДКНФ), якщо кожна елементарна сума містить всі змінні з інверсією або без.

Метод побудови ДДНФ за таблицею істинності полягає в наступному. Оскільки ДДНФ, що будується, є булевим виразом, який відповідає заданій таблиці істинності, він повинен приймати значення 1 при тих і тільки тих наборах значень аргументів, при яких у таблиці істинності стоїть 1.

Нехай заданий деякий набір значень: змінні x1, …, xn приймають значення відповідно s1, …, sn. Елементарна кон’юнкція, яка залежить від змінних x1, …, xn, при даних значеннях аргументів може дорівнювати 1 в одному і тільки одному випадку: якщо аргументи, що дорівнюють 0, входять до неї під знаком заперечення, а ті, що дорівнюють 1 – без знака заперечення. Іншими словами, єдина елементарна кон’юнкція, яка при x1 = s1, … , xn = sn дорівнює 1, має вид y1…yn, де yi =xi при si = 1 і yi = xi при si = 0. Далі, оскільки таблиця істинності дорівнює 1 при декількох наборах значень аргументів, вона повинна являти собою диз’юнкцію усіх відповідних елементарних кон’юнкцій.

Прикладом застосування алгоритму побудови ДДНФ може бути описана в ч. 2, п. 4.3.5 процедура формулювання вислову у вигляді формули для функції більшості. Отриманий остаточний вираз

і уявляє собою ДДНФ, оскільки кожен логічний доданок є кон’юнкцією всіх аргументів.

Ще один приклад. Побудуємо ДДНФ для наведеної таблиці істинності.

x |

y |

z |

F(x, y, z) |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

![]() .

.

Оскільки побудова ДДНФ дуже важливий етап у синтезі електронних схем реалізації конкретних вузлів МП-систем, наведемо ще кілька прикладів.

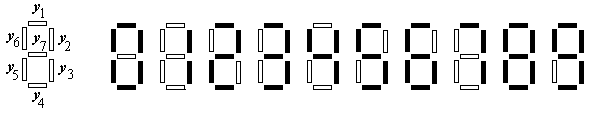

Розглянемо побудову ДДНФ для створення методом синтезу логічного пристрою перетворювача кодів, призначеного для керування семисегментним індикатором, який повинен висвітлювати одну із десяткових цифр (0, 1, 2, …, 9) в залежності від поданого на вхід коду цифри. Індикатор складається із семи сегментів, кожний з яких керується окремою логічною схемою. Схема керування кожним сегментом реалізує логічну функцію уі(х1, х2, х3, х4), де х1, х2, х3, х4 – розряди вхідного слова, яке є кодом символу, що відтворюється індикатором. Сукупність логічних схем керування сегментами і уявляє собою шифратор або перетворювач кодів.

Відповідність функцій уі і сегментів та перелік стилізованих зображень символів, які повинен створювати індикатор, показані на рис. 4.8.

Рис. 4.8.

Складемо таблицю істинності для комбінацій вхідних – х4 х1 і комбінацій вихідних – у1 у7 сигналів. При подачі коду десяткової цифри 0 (двійковий код – 0000) повинні світитись сегменти, що керуються функціями у1, у2, у3, у4, у5, у6, тобто значення цих функцій – 1 («істина»); при подачі коду десяткової цифри 1 (двійковий код – 0001) повинні світитись сегменти, що керуються функціями у2, у3; при подачі коду цифри 2 (двійковий код – 0010) повинні світитись сегменти, що керуються функціями у1, у2, у4, у5, у7 і т.д.

Таблиця 4.3.

Таблиця відповідності символу, його коду та значень логічних функцій уі.

Символ (цифра) |

Двійковий код (вхідні сигнали) |

Значення сигналів, що керують сегментами (вихідні сигнали) |

|||||||||

х4 |

х3 |

х2 |

х1 |

у1 |

у2 |

у3 |

у4 |

у5 |

у6 |

у7 |

|

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

2 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

3 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

4 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

5 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

6 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

7 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

8 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

9 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

Тепер треба дати відповідь на питання: коли повинен світитись сегмент, що керується функцією у1? Відповідь: коли буде поданий код 0000, або 0010, або 0011, або 0101, або 0110, або 0111, або 1000, або 1001 (в таблиці виділено курсивом). Цю відповідь треба записати у вигляді логічного виразу, тобто у вигляді ДДНФ:

![]()

Аналогічно будуються ДДНФ для інших функцій – у2, у3, …, у7:

![]()

![]()

![]()

![]()

![]()

![]()

Вхідні сигнали |

Вихідні сигнали |

|||

Ai |

Bi |

Pi–1 |

Si |

Pi |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Таблиця 4.4.

Таблиця істинності для однорозрядного суматора.

е один приклад побудови ДДНФ для однорозрядного суматора, з яких складається багаторозрядний суматор, і який реалізує арифметичну операцію додавання двох бітів в однойменних розрядах. На вхід такого пристрою подаються три сигнали – два доданка (Аі, Ві), і третій сигнал – значення переносу із суматора попереднього молодшого розряду (Рі–1). На виході повинні утворюватись два сигнали – значення суми в розряді (Si) і значення переносу в наступний старший розряд (Рі). Таблиця істинності для зазначених сигналів матиме вид, наведений в табл. 4.4.Так наприклад, у випадку, коли Аі = 1, Ві = 1, Рі–1 = 0, тобто значення і-тих розрядів доданків дорівнюють 1, і відсутній перенос одиниці із попереднього молодшого розряду, будемо мати 1 + 1 = 10, тобто значення суми саме в цьому розряді дорівнює 0 (Si = 0), і є перенос одиниці в сусідній старший розряд (Рі = 1). Ці обставини відображені у сьомому рядку таблиці. З аналогічних міркувань заповнюються інші рядки.

ДДНФ для вихідних сигналів Si і Рі матимуть вид:

![]()

![]()

В такий спосіб здійснюється реалізація арифметичних дій через виконання логічних перетворень.