- •Вступ 6 зм 1. Електричні властивості напівпровідників 9

- •Зм 2. Напівпровідникові прилади 26

- •Зм 3. Електронні пристрої 79

- •Зм 4. Електронні елементи мікропроцесорної техніки 164

- •Зм 1. Електричні властивості напівпровідників

- •1.1. Основи зонної теорії твердого тіла.

- •1.2. Електропровідність напівпровідників.

- •1.2.1. Власна електропровідність напівпровідників

- •1.2.2. Домішкова електропровідність напівпровідників

- •1 .2.3. Ефекти, що пов’язані з електропровідністю напівпровідників

- •1.3. Властивості електронно-діркового переходу.

- •1.3.1. Формування електронно-діркового переходу.

- •1.3.2. Властивості n-p переходу при підключенні зовнішньої напруги

- •1.3.3. Тунельний ефект

- •1.4. Питання для самоперевірки.

- •Зм 2. Напівпровідникові прилади

- •2.1. Напівпровідникові діоди1

- •2.1.1. Випрямляючі діоди

- •2.1.2. Стабілітрони і схеми стабілізації напруги.

- •2.1.3. Варикапи

- •2.1.4. Тунельні діоди

- •2.1.5. Інші види діодів

- •2.2. Біполярні транзистори і їх використання в електронних пристроях

- •2.2.1. Устрій та принцип роботи біполярного транзистора.

- •2.2.2. Режими роботи біполярного транзистора.

- •2.2.3. Схеми включення транзисторів.

- •2.2.4. Вольт-амперні характеристики біполярних транзисторів та режими роботи (на прикладі n-p-n транзисторів).

- •2.2.5. Транзистор як активний чотирьохполюсник.

- •2.3. Уніполярні транзистори.

- •2.4. Тиристори

- •2.5. Питання для самоперевірки.

- •Зм 3. Електронні пристрої

- •3.1. Випрямлячі змінного струму.

- •3.2. Підсилювачі електричних сигналів.

- •3.2.1. Загальна інформація.

- •3.2.2. Характеристики підсилювачів

- •3.2.3. Зворотний зв’язок в підсилювачах.

- •3.2.4. Схеми підсилювальних каскадів на біполярних транзисторах.

- •3.2.5. Особливості роботи схеми попередніх каскадів підсилювача.

- •3.2.6. Режими роботи підсилюючих елементів.

- •3.2.7. Особливості роботи схеми кінцевого каскаду підсилювача.

- •3.2.8. Складені транзистори.

- •3.2.9. Спеціальні види підсилювачів.

- •3.3. Транзисторні генератори електричних сигналів.

- •3.3.1. Генератори синусоїдальних коливань.

- •3.3.2. Генератори імпульсів складної форми.

- •3.3.2.1. Параметри імпульсів прямокутної форми.

- •3.3.2.2. Мультивібратори.

- •3.3.2.3. Очікуючий мультивібратор або одновібратор.

- •3.3.2.4. Блокінг-генератори.

- •3.3.2.5. Генератори пилкоподібної напруги (гпн).

- •3.3.3. Генератори сигналів на операційних підсилювачах1.

- •3.4. Питання для самоперевірки.

- •Зм 4. Електронні елементи мікропроцесорної техніки

- •4.1. Уявлення про мікропроцесорну техніку, мікропроцесорні засоби і мікропроцесорні системи.

- •4.2. Структура мікропроцесорної системи.

- •4.2.1. Загальне уявлення про мікропроцесорну систему.

- •4.2.2. Мікропроцесорні засоби в системах керування

- •4.3. Елементи математичного апарату цифрової техніки.

- •4.3.1. Системи числення.

- •4.3.2. Фізичне уявлення інформації в мп-системі.

- •4.3.3. Форми представлення чисел.

- •4.3.4. Кодування чисел в мп-системах

- •4.3.5. Поняття булевої змінної та булевої функції

- •4.3.6. Операції та закони булевої алгебри.

- •4.3.7. Функціонально повні системи булевих функцій.

- •4.3.8. Мінімізація булевих функцій.

- •4.4. Цифрові схеми та цифрові автомати.

- •4.4.1. Елементи ртл.

- •4.4.2. Елементи дтл.

- •4.4.3. Елементи ттл.

- •4.4.4. Елементи езл.

- •4.4.5. Інтегральні схеми на моп–транзисторах.

- •4.5. Комбінаційні цифрові пристрої.

- •4.5.1 Дешифратор.

- •4.5.2. Перетворювачі кодів і шифратори.

- •4.5.3. Мультиплексори і демультиплексори.

- •4.5.4. Напівсуматор і суматор.

- •4.6. Послідовнісні пристрої.

- •4.6.1. Тригери.

- •4.6.1.1. Синхронний однотактний rs–тригер.

- •4.6.1.2. Синхронний двотактний rs–тригер.

- •4.6.2. Регістри.

- •4.6.2.1. Прийом і передача інформації в регістрах.

- •4.6.2.2. Схемна реалізація зсуваючого регістру

- •4.6.2.3. Реалізація порозрядних операцій в регістрах.

- •4.6.3. Лічильники.

- •4.6.3.1. Загальне уявлення і класифікація.

- •4.6.3.2. Лічильник з безпосередніми зв’язками з послідовним переносом.

- •4.6.3.3. Лічильник з паралельним переносом.

- •4.6.3.4. Реверсивний лічильник з послідовним переносом.

- •4.6.4. Накопичуючі суматори.

- •4.6.4.1. Однорозрядний накопичуючий суматор.

- •4.6.4.2. Багаторозрядні суматори

- •4.6.5. Електронні елементи пам’яті.

- •4.6.6. Перетворювачі сигналів.

- •4.7. Питання для самоперевірки.

- •Додаток

- •Префікси для кратних одиниць

- •Список рекомендованої літератури

4.5.3. Мультиплексори і демультиплексори.

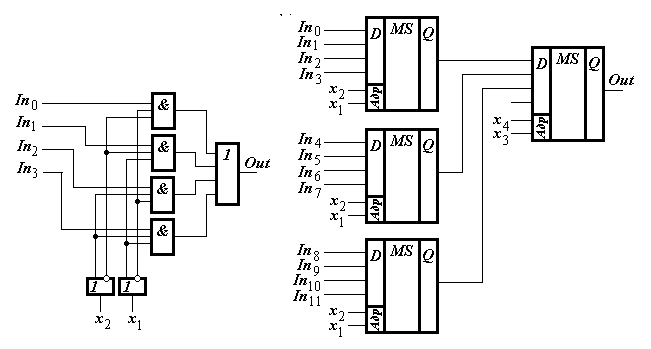

Мультиплексор – це комутатор інформаційних сигналів, що забезпечує передачу інформації, яка надходить по одній, вибраній з кількох, вхідній лінії зв’язку (Ini), на одну вихідну лінію (Out). Вхідна лінія вибирається мультиплексором відповідно надійшовшого адресного коду. При m–розрядному адресному коді можна реалізувати М = 2m комбінацій адресних сигналів, кожна з яких забезпечує вибір однієї із М вхідних ліній. Мультиплексор належить до комбінаційних логічних схем і складається з дешифратора адреси вхідної лінії, схем І та АБО. Схема мультиплексора для чотирьох вхідних ліній (In0, In1, In2, In3) та дворозрядним (х2 х1) адресним кодом подана на рис. 4.43-а.

Двійковий код адреси (х2 х1) відкриває одну із схем І(&), яка з’єднує вихідну лінію Out і відповідну вхідну лінію. При цьому інформація на виході не залежить від стану інших ліній.

Якщо треба побудувати мультиплексорний пристрій для великої кількості вхідних ліній, то можна об’єднати окремі мультиплексори в схему так званого мультиплексорного дерева, що складається з кількох рівнів комутації. Приклад такого мультиплексорного дерева показаний на рис. 4.43-б.

а) б)

Рис. 4.43.

Демультиплексор – це комутатор інформаційних сигналів, що забезпечує передачу інформації, яка надійшла по одній вхідній лінії (In), на одну із вихідний ліній відповідно встановленій адресі (Outi). Схема демультиплексору побудована аналогічно схемі мультиплексора (рис. 4.44-б). У разі необхідності мати більшу кількість вихідних ліній можна також побудувати демультиплексорне дерево. Приклад такого демультиплексорного дерева показаний на рис. 4.44-б.

а) б)

Рис. 4.44.

4.5.4. Напівсуматор і суматор.

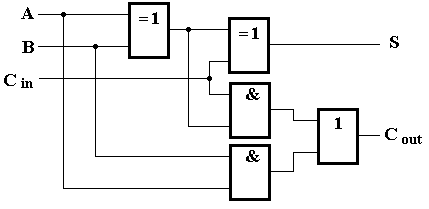

Н апівсумматор

− логічна схема має два входи та два

виходи (рис. 4.45). Напівсумматор

використовується для побудови двійкових

суматорів. Напівсумматор дозволяє

обчислювати суму A + B, де A і B - це розряди

двійкового числа, при цьому результатом

будуть два біти S, C, де S − це біт суми, а

C − біт переносу. Проте, для побудови

схеми двійкового суматора необхідно

мати елемент, який підсумовує три біта

A, B і Cin,

де Cin

− біт переносу з попереднього розряду,

таким елементом є повний

двійковий суматор, який

як правило складається з двох

напівсумматоров (рис. 4.46).

апівсумматор

− логічна схема має два входи та два

виходи (рис. 4.45). Напівсумматор

використовується для побудови двійкових

суматорів. Напівсумматор дозволяє

обчислювати суму A + B, де A і B - це розряди

двійкового числа, при цьому результатом

будуть два біти S, C, де S − це біт суми, а

C − біт переносу. Проте, для побудови

схеми двійкового суматора необхідно

мати елемент, який підсумовує три біта

A, B і Cin,

де Cin

− біт переносу з попереднього розряду,

таким елементом є повний

двійковий суматор, який

як правило складається з двох

напівсумматоров (рис. 4.46).

Рис. 4.46.

Отже, суматор − логічний операційний вузол, який виконує арифметичне додавання двійкових (трійкових або n-кових кодів двох (бінарний), трьох (трінарний) або m чисел (m-арний)). При арифметичному складання виконуються і інші додаткові операції: обрахунок знаків чисел, вирівнювання порядків доданків і тому подібне. Суматори є комбінаційними схемами, які виконують бінарну (двухоперандні), трінарну (трехоперандні) або n-арну (n-операндну) логічну функцію додавання. Входять до складу вузлів арифметико логічних пристроїв (АЛП).

4.6. Послідовнісні пристрої.

Як вже зазначалось, послідовнісними називають такі логічні пристрої, вихідні сигнали яких визначаються не тільки сигналами на входах в даний момент часу, а й передісторією їхньої роботи, тобто станом елементів пам’яті, в який вони були призведені вхідними сигналами в попередні часові моменти. Послідовнісні пристрої ще називають елементами з програмованою логікою.