- •Вступ 6 зм 1. Електричні властивості напівпровідників 9

- •Зм 2. Напівпровідникові прилади 26

- •Зм 3. Електронні пристрої 79

- •Зм 4. Електронні елементи мікропроцесорної техніки 164

- •Зм 1. Електричні властивості напівпровідників

- •1.1. Основи зонної теорії твердого тіла.

- •1.2. Електропровідність напівпровідників.

- •1.2.1. Власна електропровідність напівпровідників

- •1.2.2. Домішкова електропровідність напівпровідників

- •1 .2.3. Ефекти, що пов’язані з електропровідністю напівпровідників

- •1.3. Властивості електронно-діркового переходу.

- •1.3.1. Формування електронно-діркового переходу.

- •1.3.2. Властивості n-p переходу при підключенні зовнішньої напруги

- •1.3.3. Тунельний ефект

- •1.4. Питання для самоперевірки.

- •Зм 2. Напівпровідникові прилади

- •2.1. Напівпровідникові діоди1

- •2.1.1. Випрямляючі діоди

- •2.1.2. Стабілітрони і схеми стабілізації напруги.

- •2.1.3. Варикапи

- •2.1.4. Тунельні діоди

- •2.1.5. Інші види діодів

- •2.2. Біполярні транзистори і їх використання в електронних пристроях

- •2.2.1. Устрій та принцип роботи біполярного транзистора.

- •2.2.2. Режими роботи біполярного транзистора.

- •2.2.3. Схеми включення транзисторів.

- •2.2.4. Вольт-амперні характеристики біполярних транзисторів та режими роботи (на прикладі n-p-n транзисторів).

- •2.2.5. Транзистор як активний чотирьохполюсник.

- •2.3. Уніполярні транзистори.

- •2.4. Тиристори

- •2.5. Питання для самоперевірки.

- •Зм 3. Електронні пристрої

- •3.1. Випрямлячі змінного струму.

- •3.2. Підсилювачі електричних сигналів.

- •3.2.1. Загальна інформація.

- •3.2.2. Характеристики підсилювачів

- •3.2.3. Зворотний зв’язок в підсилювачах.

- •3.2.4. Схеми підсилювальних каскадів на біполярних транзисторах.

- •3.2.5. Особливості роботи схеми попередніх каскадів підсилювача.

- •3.2.6. Режими роботи підсилюючих елементів.

- •3.2.7. Особливості роботи схеми кінцевого каскаду підсилювача.

- •3.2.8. Складені транзистори.

- •3.2.9. Спеціальні види підсилювачів.

- •3.3. Транзисторні генератори електричних сигналів.

- •3.3.1. Генератори синусоїдальних коливань.

- •3.3.2. Генератори імпульсів складної форми.

- •3.3.2.1. Параметри імпульсів прямокутної форми.

- •3.3.2.2. Мультивібратори.

- •3.3.2.3. Очікуючий мультивібратор або одновібратор.

- •3.3.2.4. Блокінг-генератори.

- •3.3.2.5. Генератори пилкоподібної напруги (гпн).

- •3.3.3. Генератори сигналів на операційних підсилювачах1.

- •3.4. Питання для самоперевірки.

- •Зм 4. Електронні елементи мікропроцесорної техніки

- •4.1. Уявлення про мікропроцесорну техніку, мікропроцесорні засоби і мікропроцесорні системи.

- •4.2. Структура мікропроцесорної системи.

- •4.2.1. Загальне уявлення про мікропроцесорну систему.

- •4.2.2. Мікропроцесорні засоби в системах керування

- •4.3. Елементи математичного апарату цифрової техніки.

- •4.3.1. Системи числення.

- •4.3.2. Фізичне уявлення інформації в мп-системі.

- •4.3.3. Форми представлення чисел.

- •4.3.4. Кодування чисел в мп-системах

- •4.3.5. Поняття булевої змінної та булевої функції

- •4.3.6. Операції та закони булевої алгебри.

- •4.3.7. Функціонально повні системи булевих функцій.

- •4.3.8. Мінімізація булевих функцій.

- •4.4. Цифрові схеми та цифрові автомати.

- •4.4.1. Елементи ртл.

- •4.4.2. Елементи дтл.

- •4.4.3. Елементи ттл.

- •4.4.4. Елементи езл.

- •4.4.5. Інтегральні схеми на моп–транзисторах.

- •4.5. Комбінаційні цифрові пристрої.

- •4.5.1 Дешифратор.

- •4.5.2. Перетворювачі кодів і шифратори.

- •4.5.3. Мультиплексори і демультиплексори.

- •4.5.4. Напівсуматор і суматор.

- •4.6. Послідовнісні пристрої.

- •4.6.1. Тригери.

- •4.6.1.1. Синхронний однотактний rs–тригер.

- •4.6.1.2. Синхронний двотактний rs–тригер.

- •4.6.2. Регістри.

- •4.6.2.1. Прийом і передача інформації в регістрах.

- •4.6.2.2. Схемна реалізація зсуваючого регістру

- •4.6.2.3. Реалізація порозрядних операцій в регістрах.

- •4.6.3. Лічильники.

- •4.6.3.1. Загальне уявлення і класифікація.

- •4.6.3.2. Лічильник з безпосередніми зв’язками з послідовним переносом.

- •4.6.3.3. Лічильник з паралельним переносом.

- •4.6.3.4. Реверсивний лічильник з послідовним переносом.

- •4.6.4. Накопичуючі суматори.

- •4.6.4.1. Однорозрядний накопичуючий суматор.

- •4.6.4.2. Багаторозрядні суматори

- •4.6.5. Електронні елементи пам’яті.

- •4.6.6. Перетворювачі сигналів.

- •4.7. Питання для самоперевірки.

- •Додаток

- •Префікси для кратних одиниць

- •Список рекомендованої літератури

4.5.2. Перетворювачі кодів і шифратори.

Під перетворенням кодів розуміється перетворення n-розрядних двійкових чисел, що представляють інформацію в одному заданому коді, в m-розрядні двійкові числа, що представляють цю інформацію в іншому коді.

Найбільш поширені наступні два підходи до побудови перетворювачів кодів.

Перший підхід − синтез m незалежних одновихідних функцій за заданою таблицею істинності − таблиці відповідності кодів.

Припустимо, є таблиця істинності перетворювача 2-х розрядного двійкового коду у 3-х розрядний, тобто таблиця відповідності вхідного двохрозрядного коду і вихідного трьохрозрядного коду:

Таблиця 4.6.

Таблиця відповідності вхідного двохрозрядного коду і вихідного трьохрозрядного коду

a1 |

a0 |

b2 |

b1 |

b0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

Вважаючи b0, b1 і b2 залежними одновихідними функціями, запишемо для кожної з них булеві вирази:

![]()

![]()

![]() (за правилом Де Моргана).

(за правилом Де Моргана).

В икористовуючи

наведені булеві вирази з урахуванням

того, що інверсії деяких змінних і

логічний добуток

икористовуючи

наведені булеві вирази з урахуванням

того, що інверсії деяких змінних і

логічний добуток

![]() зустрічаються не в одній функції,

складаємо схему перетворювача з

застосуванням (де це можливо) одних і

тих самих логічних елементів (рис. 4.38).

зустрічаються не в одній функції,

складаємо схему перетворювача з

застосуванням (де це можливо) одних і

тих самих логічних елементів (рис. 4.38).

Такий же підхід використаний в розглянутих вище прикладах – синтезу схеми керування семисегментним індикатором (див. ч. 2, п. 4.3.7) і схеми однорозрядного комбінаційного суматора (див. ч. 2, п. 4.3.8).

Другий підхід − побудова перетворювача кодів за методом «дешифратор-шифратор». У цьому випадку по заданій таблиці істинності складається таблиця відповідності двійкових комбінацій десятковим цифрам. У розглянутому прикладі ця таблиця запишеться наступним чином:

Таблиця 4.7.

Таблиця відповідності двійкових комбінацій десятковим цифрам

A |

B |

0 |

4 |

1 |

1 |

2 |

3 |

3 |

0 |

Метод побудови перетворювача полягає в наступному. Спочатку будується схема перетворювача двійкового коду в унарний, тобто такий код, коли «1» може бути тільки на одному з N виходів перетворювача, номер якого співпадає з числом, представленим вхідним двійковим кодом (такий перетворювач називається дешифратор, що розглядався вище – ч. 2, п. 4.5.1). Число виходів дешифратора одно N = 2n, де n − число розрядів вхідного коду дешифратора (в даному випадку n = 2).

Потім будується схема перетворювача, що здійснює зворотну операцію, тобто перетворення унарного коду в двійковий. Число входів такого перетворювача, який називається шифратором, так само M = 2m, де m − число розрядів вихідного коду шифратора.

Схема перетворювача коду утворюється з’єднанням виходів дешифратора і входів шифратора відповідно до таблиці відповідності десяткових цифр (рис. 4.39). Тут DC − позначення дешифратора (DECODER), CD − позначення шифратора (ENCODER).

Рис. 4.39.

Шифратор (кодер)

(від фр. chiffre – цифра; англ. encoder)

− електронний логічний комбінаційний

пристрій, що виконує перетворення

унарного n-розрядного двійкового коду

в m-розрядний двійковий код, тобто при

подачі с игналу

на один із входів (обов’язково на один,

не більше) на виході з’являється

двійковий код номера активного входу.

Таким чином, шифратори − це комбінаційні

пристрої, що реалізують зворотну

дешифратору функцію.

игналу

на один із входів (обов’язково на один,

не більше) на виході з’являється

двійковий код номера активного входу.

Таким чином, шифратори − це комбінаційні

пристрої, що реалізують зворотну

дешифратору функцію.

Якщо кількість входів настільки велика, що в шифраторі використовуються всі можливі комбінації сигналів на виході, то такий шифратор називається повним, якщо не всі, то − неповним. Число входів і виходів у повному шифратори пов’язано співвідношенням: n = 2m, де n – кількість входів, m – число виходів. Умовне позначення шифратора наведене на рис. 4.40. Таблиця істинності шифратора має вид:

Таблиця 4.8.

Таблиця істинності шифратора

І7 |

І6 |

І5 |

І4 |

І3 |

І2 |

І1 |

І0 |

А2 |

А1 |

А0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

Отже, шифратор можна розглядати як окремий випадок перетворювача кодів, для якого код вхідного слова може містити одиницю тільки в одному розряді.

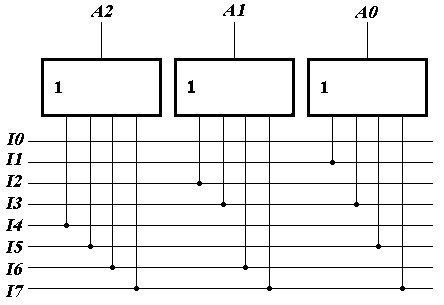

Рис. 4.41.

В

структурній схемі шифратора (рис. 4.41)

значення розрядів вихідного с лова

утворюються шляхом диз’юнкції розрядів

вхідного слова, які, відповідно таблиці

істинності, при власному одиничному

значенні надають одиничного значення

відповідному вихідному розряду.

лова

утворюються шляхом диз’юнкції розрядів

вхідного слова, які, відповідно таблиці

істинності, при власному одиничному

значенні надають одиничного значення

відповідному вихідному розряду.

Пріоритетний шифратор відрізняється від шифратора наявністю додаткової логічної схеми виділення активного рівня старшого входу для забезпечення умови працездатності шифратора (тільки один рівень на вході активний). Рівні сигналів на інших входах схемою ігноруються. Схема виділення будується на кон’юнкторах і інверторах таким чином, щоб будь-яке число старших нулів, утворюючи після інверторів логічні одиниці, не впливають на роботу кон’юнкторів в колі молодших входів. Будь-яка найстарша одиниця (після інвертора − логічний нуль) закриває кон’юнктори молодших входів. Таким чином, на вхід безпосередньо шифратора доходить одиниця тільки одного найстаршого розряду з надійшовшого на вхід схеми виділення вхідного ходу. Таблиця істинності для попередньо розглянутого шифратора, розглядаючи його вже як пріоритетний матиме вид:

Таблиця 4.9.

Таблиця істинності пріоритетного шифратора

І7 |

І6 |

І5 |

І4 |

І3 |

І2 |

І1 |

І0 |

А2 |

А1 |

А0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Х |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

Х |

Х |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

Х |

Х |

Х |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

Х |

Х |

Х |

Х |

1 |

0 |

0 |

0 |

0 |

1 |

Х |

Х |

Х |

Х |

Х |

1 |

0 |

1 |

0 |

1 |

Х |

Х |

Х |

Х |

Х |

Х |

1 |

1 |

0 |

1 |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

1 |

1 |

1 |

В наведеній таблиці «Х» означає будь-яке значення, тобто вихідний код визначається тільки найстаршим ненульовим розрядом.

Можлива структура логічної схеми виділення активного рівня старшого входу наведена на рис. 4.42.