- •40.Диференціальні підсильвальні каскади.

- •1. Класифікація твердих тіл за їх електрофізичними властивостями. Модельні уявлення щодо електропровідності твердих тіл. Елементи зонної теорії твердих тіл.

- •Модельні уявлення щодо електропровідності тв. Тіл

- •Елементи зонної теорії тв. Тіл

- •2. Класична теорія електропровідності. Рухомість носіїв заряду, питомий опір та провідність.

- •3. Статистика електронів та дірок в напівпровідниках. Густина квантових станів. Функція розподілу Фермі – Дірака для електронів та дірок.

- •4. Залежність положення рівня Фермі від концентрації домішок та температури в напівпровідниках.

- •5. Дифузійний та дрейфовий струми в напівпровідниках. Рівняння неперервності.

- •6. Напівпровідник у зовнішньому електричному полі. Дебаєвська довжина екранування.

- •7. Модельні уявлення, щодо контакту двох напівпровідників із різними типами провідності. Ефект випрямлення струму на p-n переході.

- •9. Товщина шару об΄ємного заряду p-n переходу. Бар΄єрна та дифузійна ємність p-n переходу. Варікапи, їх характеристики та параметри.

- •10. Контакт вироджених n- та p- напівпровідників. Тунельний діоди, їх характеристики та параметри.

- •11. Пробой p-n-перехода. Стабилитрон.

- •12. Внутрішній фотоефекти. Фотодіоди та фототранзистори, їх характеристики та парметри.

- •13. Контакт метал – напівпровідник. Товщина шару об΄ємного заряду в контакті метал – напівпровідник.

- •14. Ефект випрямлення струму в контакті метал – напівпровідник. Діоди Шотки, їх характеристики та параметри.

- •15. Біполярні транзистори, їх характеристики та параметри.

- •16. Распределение носителей заряда в базе биполярного транзистора. Эффект модуляции толщины базы биполярного транзистора.

- •17. Динамічний режим роботи біполярного транзистора.

- •18. Схемы питания и стабилизации режима работы транзистора

- •21. Виды имс. Методы фотолитографии. Конструктивно-технологічні особливості біполярных имс, мдн- імс та гібридних імс.

- •23. Параллельный Колебательный Контур. Резонанс Токов.

- •24.Связанные контуры. Резонанс в индуктивно связанных контурах.

- •26 Четырехполюсники.

- •27. Електричні кола з розподіленими параметрами.

- •28.Не линейные электрические цепи.

- •29. Методы преобразования цепей

- •30. Методы расчёта сложных цепей. Метод Сигнальных графов

- •31. Переходные процессы в rc-цепях.

- •32. Переходные процессы в rl-цепях

- •33.Переходные процессы в rlc цепях

- •34.Операторный метод анализа переходных процессов.

- •35. Спектральный метод ряд фурье и его свойства.

- •36.Классификация усилителей. Основные хар-ки и параметры усилителей,

- •37. Классы усиления.

- •38. Усилитель низкой частоты

- •39. Обратные связи в усилителях.

- •40. Дифференциальные усилительные каскады

- •41. Выходные каскады усиления, характеристики и параметры.

- •46. Чм и фм –модуляция колебания.

- •45. Амплитудная модуляция

- •47. Детектирование сигналов. Детектор.

- •49. Мінімізація логічних пристроїв. Мінімізація із застосуванням карт Вейча.

- •50. Комбінаційні логічні пристрої. Типові функціональні вузли цифрових комбінаційних логічних пристроів

- •51.Перетворювачі кодів. Дешифратори.

- •52.Цифрові компаратори

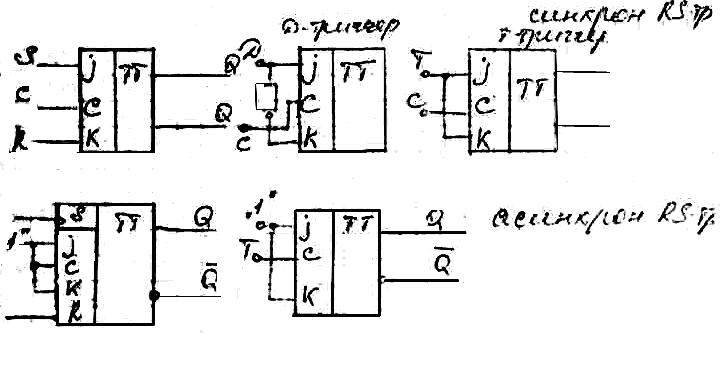

- •53. Синхронний rs-тригери

- •57. Регістри

- •58. Лічильники

- •59. Дискретизация непрерервних сигналiв

- •60. Квантование сигналов

- •61.Фурье перетворення дискретных сигналiв

- •62. Алгоритми швидкого перетворення Фурьє

- •64. Рекурсивные и нерекурсивные фильтры

- •65 Методи синтезу цифрових фільтрів з нескінченною імпульсною характеристикою. Метод білінійного z-перетворення.

- •67.Ефекти кванування в цифрових фільтрах.

- •68. Явище епр. Тонка, надтонка та спер надтонка структура спектрів епр.

- •69. Форма ліній епр. Однорідне та неоднорідне розширення ліній епр.

- •71. Явище ямр. Ямр в рідинах та твердому тілі.

- •73.Двойные резонансы.

- •76. Отрицательные температуры и отрецательный коефициент поглощения.

- •79. Физические принципы лежащие в основе построения модуляторов лазерного излучения. Типы модуляторов.

53. Синхронний rs-тригери

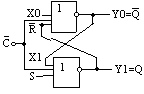

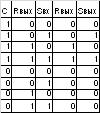

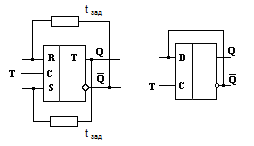

Таблица истинности синхронного RS-триггера Синхронный RS-триггер может быть получен на базе асинхронного RS-триггера введением дополнительной лог схемы, которая бы формировала на его входах активные лог уровни только при наличии дополнительного сигнала синхронизации.

И-НЕ:

ИЛИ-НЕ:

Таблица истинности синхронного RS-триггера

Синтезируем такую схему.

Предположим что триггер снабжен прямыми входами синхронизации. Информационные входы триггера (R,S) тоже прямые. Табл. ист-ти дополнительной схемы будет иметь вид:

Карта Вейча синхронного RS-триггера

Карты Вейча можно представить в виде:

54. D-тригери

Таблица истинности D-триггера

D-триггер снабжен 1-м информационным входом (вход D), информация с которого по определению входа переписывается на выход триггера только по сигналу синхронизации. Таблица истинности D-триггера:

С |

Qn |

Qn+1 |

D |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

ФАЛ D-триггера

Так

как информация на выходе D-триггера

остаётся неизменной до прихода очередного

импульса синхронизации, данный триггер

часто называют триггером с запоминанием

информации или триггером с задержкой.

На рисунке приведен триггер синтезированный

на основе синхронного RS-триггера.

Для реализации работы D-триггера

описанной таблицы истинности сигналы

на RS-входах

должны быть связаны с сигналом D-входа

в соотношении

На рисунке приведен триггер синтезированный

на основе синхронного RS-триггера.

Для реализации работы D-триггера

описанной таблицы истинности сигналы

на RS-входах

должны быть связаны с сигналом D-входа

в соотношении

![]()

Подставим эти соотношения в ФАЛ RS- триггера, и получим ФАЛ описывающую работу D-триггера:

![]()

![]() Структурная

схема D-триггера

Структурная

схема D-триггера

Разновидностью D-триггера является VD-триггер, который дополнительно снабжен входом разрешения работы V. Действие входа V аналогично входу S. При V=1 поведение триггера соответствует уравнению , а при V=0 – триггер хранит записанную в него ранее информацию (Qn+1=Qn).

D-триггер

может быть

снабжен дополнительным входом асинхронной

установки. С учетом входа блокировки V

и инверсных асин-хронных входов установки

![]() ФАЛ D-триггера

имеет вид:

ФАЛ D-триггера

имеет вид:

![]()

Условные обозначение D-триггера

![]()

На рис. показано два варианта условных обозначений D-триггера. Буквы ТТ означают, что триггер двухступенчатый и, следовательно, с внутренней задержкой. Косая черта на входе С означает, что триггер переключается по спаду сигнала С. Два отдельных поля для сигналов R и DC означают, что сигнал С синхронизирует вход D, а вход R несинхронизированый асинхронный.

55. T-тригери.

Таблица переходов Т-триггера

Т–триггер–счётный

триггер. Согласно определению входов

должен изменять своё состояние на

противоположное по каждому активному

логическому сигналу. Действующему на

информационном входе Т. Такому алгоритму

переходов соответствует таблица

переходов, в которой активным является

лог 1 и лог выражение типа:![]()

-

Qn

Qn+1

Т

0

0

0

0

1

1

1

0

1

1

1

0

ФАЛ Т-триггера

Используя

выражение

![]() и замечания, сделанные для синхронного

RS–триггера,

получим ФАЛ Т–триггера:

и замечания, сделанные для синхронного

RS–триггера,

получим ФАЛ Т–триггера:

![]()

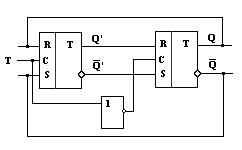

Такой режим обеспечивается введением в RS–триггер или D–триггер цепей дополнительной обратной связи.

Структурная

схема Т-триггера

Такие Т-триггеры не обеспечивают надёжную работу, так как они одновременно должны быть источниками информации и её приёмниками, и при реальном быстродействии лог элементов такие схемы неработоспособны. Так как если к началу изменения сигнала на R, S или D входах, сигнал Т ещё не снят, а происходит следущее переключение триггера, то происходит генерирование незатухающих колебаний. Для их устранения используют дополнительный элемент памяти, запоминающий новые значения сигналов R, S или D и подающий их на информационные входы основного элемента памяти только после снятия активного сигнала на входе Т. Эти принципы реализованы в так называемых двухступенчатых триггерах и триггерах с динамическим управлением.

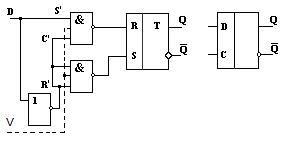

В 2-х ступенчатом триггере противоречие между процессом хранения старого и приема новой информации решены внедрение 2-го запоминающего элемента. При этом новая информация формируется только на входной ступени когда новое состояние ступени сформировано и снят активный уровень сигнала со входа Т и происходит ее перезапись в выходной ступень устройства.

То 2-х ступенчатый триггер фактически состоит из 2-х последовательно соединенных триггеров ведущего и ведомого.

Для устранения режима автоколебаний синхронизация работы ведущего и ведомого триггера осуществляется инверсными логическими уровнями.

2-х

ступенчатые триггеры называют MS-триггеры.

(От английского master

slave)

по структуре 2-х ступенчатые триггеры

могут построены любые типы триггеров.

В качестве примера рассмотрим реальную

структуру 2-х ступенчатого на RS-триггерах,

который носит название триггера с

запрещающими связями.

В качестве примера рассмотрим реальную

структуру 2-х ступенчатого на RS-триггерах,

который носит название триггера с

запрещающими связями.

![]()

На интервале действия сигнала С=0 (для элемента и-не активный уровень при С=0).

На выходах первого DD1 и DD2 элемента 2 и-не присутствуют сигналы логической «1».

Эти сигналы пассивны для 1 го асинхронного RS-триггера DD3. Он находиться в режиме хранения информации.

![]()

Допустим

![]() то

то

![]() этот сигналы совместно с выходными

сигналами элементов DD1

и DD2

попадают на входы 1 го DD4

и второго DD5

элементов 3 и-не. В результате на выходах

2-го асинхронного RS-триггера

устанавливается в единичное состояние.

То в интервале действия сигнала S=0

информация их 1-го триггера переписывается

во 2-й триггер на входы которого

устанавливаться сигналы:

этот сигналы совместно с выходными

сигналами элементов DD1

и DD2

попадают на входы 1 го DD4

и второго DD5

элементов 3 и-не. В результате на выходах

2-го асинхронного RS-триггера

устанавливается в единичное состояние.

То в интервале действия сигнала S=0

информация их 1-го триггера переписывается

во 2-й триггер на входы которого

устанавливаться сигналы:

![]() то

то

![]() .

.

Предположим на входах триггера действуют сигналы R=1 и S=0. тогда по сигналу С=1 непосредственно входах R1 и S1 первого асинхронного триггера DD3 сформируется сигнал R1=0 и S1=1, который сбрасывает его одновременно с этим сигнал логического «0» на выходе 1-го элемента поступает на элементы DD4 и DD5 элементов 3 и-не формирует на их выходах пассивный для 2-го RS-триггера сигналы поэтому триггер находиться в режиме хранения информации.

Следовательно при С=1 входная информация записывается в триггер DD3. Триггер DD6 2-й ступени хранит информацию, которую следует заменить на новую информацию на интервале действия сигнала S=0.

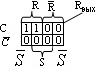

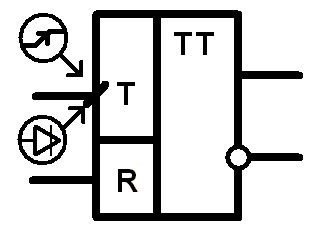

Условные обозначения Т-триггера

![]()

Буквы ТТ означают, что триггер двухступенчатый и, следовательно, с внутренней задержкой. Косая черта на входе С (Т) означает, что триггер переключается по нарастанию сигнала С(Т). Два отдельных поля для сигналов TC и DV означают, что сигнал С синхронизирует вход T, а входы DV несинхронизированы (асинхронные).

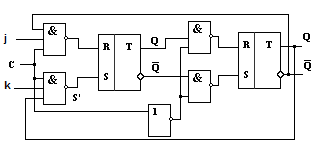

56. JK-тригери

JK-триггер – является наиболее универсальным триггером, так как на его основе могут быть реализованы ранее рассмотренные триггеры.

В отличие от RS-триггера JK-триггер имеет запрещенную комбинацию выходных сигналов, и его таблицей переходов предположено, что активным является сигнал логической «1» имеет вид следующий:

Таблица истинности

Qn |

Qn+1 |

j |

К |

0 |

0 |

0 |

- |

0 |

1 |

1 |

- |

1 |

0 |

- |

1 |

1 |

1 |

- |

0 |

Таблица отражает определение входов j и k, то или подаче на них активного сигнала, соответственно устанавливают и сбрасывают JK-триггер. По приведенной таблице можно получить выражение описывающие работу асинхронного и синхронного JK-триггера.

![]()

Это фал для асинхронного и синхронного JK-триггера.

Из таблицы переходов JK-триггера видно, что при подаче на информационный входы j и k операция 2-х логических уровней триггер работает как счетный.

Следовательно структурная схема должна подобна схеме Т-триггера, тесть должна цепи обратной связи. Поэтому структура JK-триггера базируется на структуре MS-триггера или триггера с одним логическим входом

Введение обратной связи решает задачу запрещенных входных сигналов. Входы jk могут функционировать R и S RS-триггере.

Основные схемы различных триггеров построенных на JK-триггере:

Условные обозначения

Буквы ТТ означают, что триггер двухступенчатый и, следовательно, с внутренней задержкой. Косая черта на входе С означает, что триггер переключается по спаду сигнала С. Три отдельных поля для сигналов S, R, и C,J,K означают, что сигнал С синхронизирует входы J и K, а входы R и S несинхронизированые (асинхронные).

![]()

![]()

![]()

![]()

![]()