- •Contents

- •Preface

- •About This Manual

- •Other Information Sources

- •Syntax Conventions

- •Text Command Syntax

- •About the Graphical User Interface

- •Using Menus

- •Using Forms

- •Introduction to Ambit BuildGates Synthesis

- •Separately Licensed Software Products

- •Low Power Synthesis

- •Physically Knowledgeable Synthesis

- •Datapath Synthesis

- •AC_Shell / DC_Shell Equivalencies

- •Getting Started

- •Invoking Ambit BuildGates Synthesis

- •Exiting Ambit BuildGates Synthesis

- •Files Used in Ambit BuildGates Synthesis Software

- •Key Bindings and Mouse Operations

- •Using the GUI

- •Main Menu Functions

- •File Menu Options

- •Edit Menu Options

- •View Menu Options

- •Commands Menu Options

- •Reports Menu Options

- •Window Menu Options

- •Help Menu Options

- •The Tool Bar

- •The Browsers

- •The Module Browser

- •The Variable Browser

- •Work Area Tools

- •HDL and Tcl Editors

- •Constraints Tool

- •The Schematic Viewer

- •Distributed Processing

- •Update Mode

- •The ac_shell Console

- •The Status Bar

- •Flow Procedures

- •Typical Synthesis Flow

- •Read the Libraries

- •Read the Design Data

- •Build Generic Netlist

- •Set Constraints

- •Optimize the Design

- •Generate Reports

- •Save Final Netlist

- •Viewing the Schematic Design

- •How to Use the Schematic Viewer

- •Keyboard Shortcuts

- •Mouse Operations

- •Objects in the Schematic Database

- •Accessing Context-Sensitive Pop-Up Menus

- •Highlighting Path Between Pins

- •Viewing Bus Properties

- •The Schematic Tool Bar

- •The Module Title Bar

- •Searching for an Object

- •Grouping Instances

- •Dissolving Instances

- •Creating a Unique Module

- •Displaying Logic Cones

- •Extracting Logic Cones

- •Displaying Port Constraints

- •Printing a Schematic

- •Setting Constraints

- •Setting a Hierarchical Context

- •Units in Constraints

- •Timing Constraints

- •Timing Analysis

- •Setting up Timing Context

- •Clock Insertion Delay Time

- •Data Arrival Time

- •External Delay

- •Multicycle Paths

- •Setting Drive Cell for Input Ports

- •Setting Drive Resistance

- •Slew Related Commands

- •Technology and Design Rule Constraints

- •Operating Conditions

- •Estimating Capacitance and Resistance

- •Port Capacitance

- •Capacitance Limit

- •Fanout

- •Fanout Limit

- •External Sources and Sinks

- •Wire Capacitance

- •Wire Resistance

- •Wire Load Model Selection

- •Optimizing Before Place and Route

- •Running do_optimize Command

- •Top-Down Optimization

- •Bottom-Up Optimization

- •Deriving Constraints from Context

- •Time Budgeting

- •Preserving Module Contents

- •Uniquifying Instances

- •Collapsing Hierarchy

- •Incremental Optimization

- •Applying Timing Corrections

- •Optimizing with Logic Transforms

- •Introduction to Transforms

- •Logic Optimization Steps

- •Optimizing Generic Logic

- •Mapping and Unmapping of Generic Logic

- •Constraint-Driven Optimizing

- •Summary Listing of Transform Commands

- •Optimizing After Place and Route

- •Timing Analysis

- •Backannotating

- •A Script Showing the Backannotation of a Design

- •Reading SDF Data

- •Optimizing to Correct Late and Early Slack

- •Report Generation

- •Report Header

- •Timing Reports

- •Area Reports

- •Sample Area Report

- •Library Reports

- •Hierarchy Reports

- •Sample Hierarchy Report

- •Design Rule Violations Reports

- •Sample Design Rule Violations Report

- •VHDL Library Reports

- •Sample VHDL Library Report

- •End Point Slack and Path Histogram Reports

- •Fanin and Fanout Reports

- •Sample Fanin Report

- •Finite State Machine Reports

- •Sample FSM Report

- •Customizing Report Column Width

- •Using Tcl within ac_shell and pks_shell

- •The Tcl Language

- •Procedures

- •Tcl Variables and Control Structures

- •Variables

- •Syntax

- •Tcl Commands

- •get_names Command

- •Abbreviating Commands

- •Searching for Commands

- •Accessing Environment Variables

- •Returning Unix Command Values

- •Error Handling

- •Quick Reference

Ambit BuildGates Synthesis User Guide

Setting Constraints

Wire Load Model Selection

Figure 6-19 provides a flow chart of the algorithm used for selecting a wire load model for a net.

Figure 6-19 Finding Wire Load Model W for a Net N

Net N

Find module modx that encloses net N

Find hierarchically lowest level module M enclosing modx with user specified wire load model W

Wireload mode = enclosed

No |

Yes |

use area of top module

use area of module modx

Lookup wire load model W from module

Wire Load Model W

September 2000 |

163 |

Product Version 4.0 |

Ambit BuildGates Synthesis User Guide

Setting Constraints

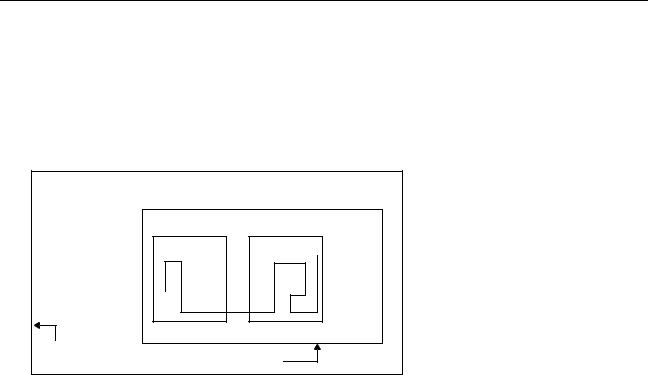

Figure 6-20 depicts the wireload for a net, where T is the current top module, A is an instance inside T, and M1 and M2 are two instances inside A. The net net1 is fully contained inside A, but not fully contained inside either M1 or M2.

Figure 6-20 Estimating the Wireload for a Net

T

A

M1 M2

net1

top

enclosed

The wire load for net1 is estimated as follows:

■Identify the enclosing module for net1. In the figure above, module A is the enclosing module.

■For A or its parent modules (modules in its upward hierarchical path), identify if wire load table is already set.

■If set, use it as the wire load table.

■If not set, check the global wire load mode (by default, this is top).

■If the mode is enclosed, use the area of enclosing module A to identify the wire load table.

■If the mode is top, use the area of top module T to identify the wire load table.

The area look-up table for the wire load model is in the technology file.

September 2000 |

164 |

Product Version 4.0 |