- •Введение

- •Моделирование поведенческого Verilog-описания

- •Пример и моделирование вентильного описания

- •Создание прогнозного SDF файла в системе “Cadence”

- •Моделирование вентильного описания с файлом задержек, сравнение результатов.

- •Пример описания модуля по подготовке файла с результатами моделирования.

Руководство по моделированию на языке Verilog

Маршрут проектирования БИС |

|

Содержание |

|

Введение............................................................................................... |

3 |

Моделирование поведенческого Verilog-описания....................... |

4 |

Пример и моделирование вентильного описания........................ |

7 |

Создание прогнозного SDF файла в системе “Cadence” ............. |

9 |

Моделирование вентильного описания с файлом задержек, |

|

сравнение результатов. ................................................................... |

14 |

Пример описания модуля по подготовке файла с результатами |

|

моделирования. ................................................................................. |

16 |

Версия 2.2 |

2 |

Маршрут проектирования БИС

Введение

Данный документ описывает вариант маршрута этапа логического моделирования. Результатом этого этапа являются отлаженное описание схемы и подготовленный файл входных и ответных реакций, являющийся эталоном функционирования, который в дальнейшем будет использован при измерениях изготовленных БИС. Документ описывает основные принципы и методику этапа логического проектирования в САПР “Cadence”.

Кроме отладки схемы с помощью моделирования, должна быть отлажен файл эталонных входных и ответных реакций. Для этого при описании схемы необходимо сразу продумать, как ее будут “измерять”, необходимо определить длительность элементарной проверки (теста), положение строба считывания. По стробу считывания при моделировании должен получится файл, который максимально полно описывает функционирование схемы и соответствует техническому заданию.

3

Маршрут проектирования БИС

Моделирование поведенческого Verilog-описания

Ниже приведен пример описания счетчика на языке Verilog. Текст справа от символа “//” является комментарием в языке Verilog и содержит пояснения. В данном примере также приведен раздел описания тестов. Для описания тестов имеется большой набор средств. Символ # - символ задержки. По умолчанию задержка в нс (наносекундах). В языке также используются операторы заданий для моделирования, они начинаются со знака $. Здесь же приведен пример формирования текстового файла результатов.

При моделировании используются 2 файла. В одном файле находится описание схемы, в другом описание тестовой оснастки на моделирование. В данном документе рассматривается автономный режим моделирования Verilog-XL .

Более подробное описание языка Verilog и его возможностей приведено в документе “Verilog-XL reference”, входящем в штатную документацию САПР СБИС “Cadence”.

// Исходная поведенческая модель (файл counter.v)

`timescale 1ns / 1ps |

// точность моделирования < 1.0 ns |

module count5(q, data, load, clock, enable, reset); |

// имя схемы и перечисление выводов |

input load, clock, enable, reset; |

// входы |

input [5:1] data; |

// 5-и разрядный вход |

output [5:1] q; |

// 5-и разрядный выход |

reg [5:1] q;

always @(posedge clock or negedge reset)

if (!reset) q = 5'b0; else

if (load) q = data; else if (enable)

if (q == 5'b11111) q = 5'b0; else q = q + 1'b1;

else q = q; endmodule

//регистровая переменная

//цикл всегда при положительном

//фронте clock или отрицательном reset

//если reset равен 0, то q равен 0 (обнуление)

//иначе

//если load равен 1, то в q заносится data

//если enable равен 1 (стоит разрешение)

//если q заполнен, то обнулить

//иначе увеличить q на 1

//иначе оставить q без изменения

module test_t;

// Раздел описания тестов и заданий на моделирование (тестовой оснастки) (файл tests.v)

`define PERIOD 10 |

// длительность периода 10 ns |

|

`define delta1 |

8 |

// задержка строба считывания от начала теста |

`define delta2 |

2 |

// время строба для выравнивания под период |

|

|

// delta1+delta2=PERIOD |

module test_t; |

|

|

reg clock,enable,load,reset; |

// выводы на котрые подаются входные сигналы |

|

reg [5:1] data; |

|

// описываются как reg |

4

|

|

Маршрут проектирования БИС |

||

wire [5:1] q; |

|

|

|

|

reg strob; |

// строб считывания |

|

||

reg [19:0] testnumber; |

// номер теста |

|

||

integer vector_file; |

// переменная для файла результатов |

|||

always |

// всегда |

|

||

begin |

|

|

|

|

#`delta1 strob =1; # `delta2 strob=0; |

// описание строба время delta1 в 1, время delta2 в 0 |

|||

testnumber=testnumber+1; |

// увеличение номера теста |

|||

end |

|

|

|

|

always @(posedge strob ) |

|

// всегда по положительному фронту strob |

||

$fdisplay(vector_file,"%b%b%b%b%b%b%b",clock, clock,enable,load,reset,data,q); |

||||

|

|

|

// выдать в файл состояния по clock, clock,enable,load,reset,data,q |

|

initial |

|

// старт моделирования |

|

|

begin |

|

|

|

|

vector_file = $fopen("test_m.dat"); |

// имя файла результатов |

|||

testnumber=1; strob=0; |

|

// начальные переменные |

||

|

|

// дополнительная выдача при моделировании |

||

$gr_regs("TEST","------","q %d",q,"Testnumber %d",testnumber,""); |

// текстовая панель (окно выдачи) |

|||

$gr_position("regs",0,100,150,200); |

|

|

// позиция текстовой панели |

|

$gr_waves("clock",clock,"data %d",data,"reset",reset, |

// выдача в окне диаграмм |

|||

"q %d",q,"strob",strob,"testN %d",testnumber); |

|

|||

// пример описания тестов |

|

|

|

|

reset = 1'b0; strob=0; |

|

|

|

|

repeat(20) |

|

|

|

|

begin |

|

|

|

|

#`PERIOD clock = 1'b0; data[5:1] = 5'b00000; enable = 1'b1; |

|

|||

load = 1'b0; |

reset = 1'b1; |

|

|

|

#`PERIOD |

clock = 1'b1; |

|

|

|

end |

|

|

|

|

$stop; $finish; |

|

// останов и завершение |

|

|

end |

|

|

|

|

count5 count5(q, data, load, clock, enable, reset); // подключение тестируемой схемы endmodule

Само моделирование для данного примера выполняется по команде

5

Маршрут проектирования БИС

verilog.exe counter.v tests.v

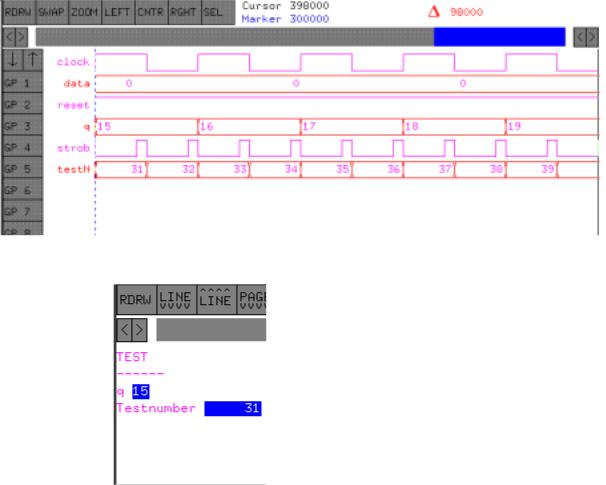

Ниже приведены графические окна дополнительной выдачи.

После останова можно с помощью двух курсоров выбрать участок для просмотра. Установка первого курсора: - нажатие левой кнопки мыши. Установка второго курсора: - SWAP и нажатие левой кнопки мыши. Можно поменять порядок выводимых сигналов, измерить задержки. Чтобы завершить задачу необходимо в терминальном окне набрать символы ”. ” и Enter.

6