- •Лінійні блокові систематичні коди, генеруючи та перебіркова матриця.

- •2. Циклічні коди

- •3. Згорткові коди.

- •4. Імпульсно-кодова модуляція

- •Импульсно-кодовая модуляция

- •7. Властивості лінійних дискретних систем

- •Властивість пам'яті лінійних дискретних систем

- •Стійкість лінійних дискретних систем

- •Оцінка стійкості по імпульсної характеристиці: критерій стійкості

- •Приклад

- •8. Дискретні перетворення сигналів

- •7.5.1. Спектр Фур'є неперервних та дискретних сигналів.

- •10 .Передавальна функція лінійних дискретних систем

- •11 Види ліній зв’язку та їх основні властивості

- •12.Первинні параметри кола

- •Вторинні параметри кола

- •13 Поверхневий ефект. Причина явища.

- •14.Ефект близькості в двопровідній лінії зв’язку. Причина явища.

- •15. Конструктивні елементи кабелів електрозв’язку

- •16. Стандартні інтегральні мікросхеми ттл-логіки

- •17. Типи технологій логічних мікросхем

- •18. Параметри логічних імс

- •19. Методи покращення завадостійкості радіоелектронних пристроїв на інтегральних мікросхемах

- •20. Перетворювачі код-аналог на матрицях r-2r

- •Класифікація зп

- •Перша цифра 1,5,6,7 – напівпровідникові мікросхеми

- •Статичні запам’ятовуючі пристрої

- •Динамічні зп

- •Асинхронна пам’ять (fpm edo bedo)

- •Синхронна пам'ять

- •Пам'ять з внутрішнім кешом

- •Відеопам'ять

- •24. 2.1. Амплітудна модуляція (am)

- •26 Генератори із зовнішнім збудженням.

- •26. Генератори із зовнішнім збудженням.

- •26/1 Генератор із зовнішнім збудженням

- •Принципові схеми генераторів із зовнішнім збудженням

- •2. Схема з загальною сіткою

- •3. Схема з загальним анодом

- •27. Аналіз амплітудно-модульованого коливання

- •28. Основні технічні характеристики антен

- •29.Метод дзеркальних зображень.Дыаграми напрямленосты розыщених над землею выбраторыв.

- •31.Режими роботи фідерів. Коефіцієнти стоячої та біжучої хвиль.

- •32.Трансформуючі властивості фідерних ліній.

- •33.Вплив землі на випромінювання антени

- •35.Елементарний магнітний диполь

- •36.Елементарна випромінююча щілина

- •38. Дзеркальні антени.

- •39. Лінзова антена

- •Принцип дії

- •41Канали зв’язку в інформаційно- вимірювальних системах.

- •42. Види і склад інформаційно-вимірювальних комплексів.

- •43. Параметри радіоелектронних засобів та їх вплив на електромагнітну сумісність.

- •44. Структура електромагнітного поля та принципи екранування.

- •45. Індустріальні джерела завад.

- •Ймoвірнісні методи в задачах оцінки та забезпечення надійності рез.

- •Густина розподілу безвідмовної роботи , () ()

- •53. Активна, реактивна і повна потужності в колах синусоїдального струму.

- •Перехідні процеси велектричних колах

- •Закони комутації

- •Усталений режим. Перехідний режим : струми і напруги перехідного режиму.

- •Порядок розрахунку перехідного процесу класичним методом

- •58.Спектри періодичних і неперіодичних сигналів

- •58. Спектри періодичних і неперіодичних сигналів

- •59. Випадковий процес. Основні моментні функції.

- •60.Спектральний метод аналізу проходження випадкових сигналів через лінійні електричні кола.

- •Середнє значення вихідного сигналу

- •Тому, виконуючи усереднення в обох частинах рівності (8.2), матимемо:

- •Отже, вихідний сигнал зв'язаний з вхідним сигналом співвідношенням

- •61. Тепловий шум резистора, формула Найквіста.

- •8.3.1.1. Формула Найквсіта

- •У цій формулі вважатимемо, що і знайдемо дисперсію . Тут же врахуємо, що, білий шум - це випадковий процес зі сталим на всіх частотах спектром потужності . Тоді

- •З іншого боку,

- •62. Диференційний підсилювач (рис. 113).

- •6.2.4. Диференційні (різницеві) схеми

- •6.2. Методи пониження дрейфу нуля підсилювача.

- •6.2.1. Термостабілізація

- •6.2.2. Термокомпенсація

- •64. Методи пониження потенціалу електродів підсилювальних елементів в підсилювачах постійного струму.

- •65. Підсилювачі постійного струму з перетворенням сигналу.

- •66. Способи задання та стабілізації положення робочої точки.

- •67.Суматори аналогових сигналів на операційних підсилювачах

- •Автоматичнепідстроюваннячастоти

- •4.1 Частотне автоматичне підстроювання частоти

- •71.Інтеггруюча та диференціюючи ланка на оп

- •72. Інвертуючий підсилювач на оп.

- •73. Неінвертуючий підсилювач на оп.

- •74. Аналого – дискретні підсилювачі.

- •3.3 Аналого – дискретні підсилювачі.

- •75. Схемотехнічна реалізація підсилювачів класу d.

- •77/. Вхідні кола

- •78.Розбивка робочого діапазону частот на піддіапазони

- •79. Резонансні підсилювачі.

- •§5.2 Смугові підсилювачі.

- •§6 Перетворювачі частоти.

- •§6.1 Принципи перетворення частоти

- •§6.2 Побічні продукти перетворення.

- •§6.3 Типи перетворювачів частоти.

- •Нормальний закон розподілу випадкової похибки. Середньо-квадратичне значення та дисперсія випадкової похибки.

- •85.Способи вимирювання частоти і часових інтервалів методом калібровочних міток

- •86. Принципи сучасного телебачення. Фізіологічні властивості ока, їх вплив на технічні рішення в телебаченні.

- •87.Параметры разложения изображения в телевидении

- •88.Принципи кольорового телебачення

- •89. Система кольорового телебачення ntsc і pal (спрощенні схеми та спосіб кодування)

- •91. Типи мікрофонів основні характеристики мікрофонів.

- •92. Акустичні фільтри. Пристрої на поверхнево-акустичних хвилях. Приклади застосування.

- •93. Ефект Доплера. Конус Маха. Ультразвукові прилади на основі ефекту Доплера.

- •94. Застосування ультразвуку в медичній галузі.

- •95. Енергетичні характеристики звукового поля. Акустичний імпеданс.

- •96. Принцип дії пасивного інфрачервоного детектора руху.

- •97 . Загальна модель системи захисту об’єкту.

- •98. Типи датчиків, які використовуються в системі протипожежного захисту.

- •99. Класифікація протикрадіжкових систем захисту.

- •100. Основні складові базової системи відеоспостереження.

- •101. Якісні показники та критерії оптимального виявлення та розрізнення сигналів.

- •102.Характеристики сигналів та завад в ртс

- •103. Фазовий метод вимірювання кутових координат.

- •104. Принципи отримання інформації радіолокації

- •105. Залежність дальності спостереження від різних факторів. Узагальнене рівняння радіолокації у вільному просторі.

- •Рівняння дальності при віддзеркаленні радіохвиль від Земної поверхні.

- •Гранична дальність дії. Зона видимості.

- •Вплив умов розповсюдження радіохвиль на дальність дії рлс.

- •Вплив затухання радіохвиль на дальність дії.

- •106.Законодавче та нормативно-технічне забезпечення охорони праці

- •107.Відповідальність за порушення законодавства про охорону праці

- •109. Дія електричного струму на організм людини

- •110. Вплив шуму на організм людини

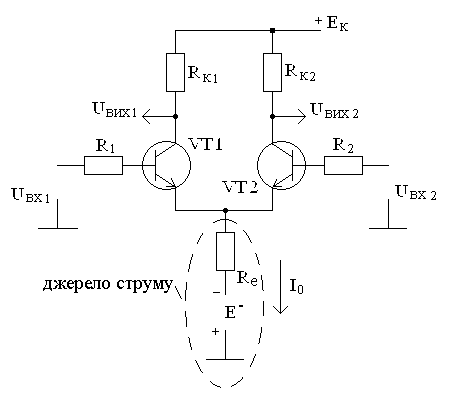

62. Диференційний підсилювач (рис. 113).

Рис. 113

Використовуючи принцип віртуального замикання:

![]()

Величина напруги на неінвертуючому вході рівна:

![]() .

.

Напруга, що буде діяти на виході підсилювача,

![]() ,

,

де

![]() ,

окільки

,

окільки

![]() ,

то величина спаду напруги на резисторі

R4

рівна

,

то величина спаду напруги на резисторі

R4

рівна

![]() .

.

Отже,

![]() .

.

Зробимо заміну U– на U+, і, підставивши відповідні значення, отримаємо:

![]() .

.

В

перших двох доданках винесши за дужки

![]() ,

отримаємо:

,

отримаємо:

![]() .

.

Припустимо, що R1=R2, R3=R4. Провівши відповідні підстановки, отримаємо

![]() .

.

Коефіцієнт підсилення диференційного підсилювача при виконанні умови (R1 = R2, R3 = R4) визначається відношенням опорів ОЗ та вхідного опору.

6.2.4. Диференційні (різницеві) схеми

Ефективним

схемотехнічним способом пониження

дрейфу нуля ППС з гальванічним зв’язком

є використання диференційних (різницевих)

схем.  Рис.

92

Рис.

92

Специфічною особливістю даної схеми є наявність двох вхідних та вихідних клем. Для того, щоб даний підсилювач можна було назвати диференційним (різницевим), необхідно виконати такі умови:

RК1 = RК2.

Всі параметри VT1 дорівнюють всім параметрам VT2.

Для полегшення виконання цих умов транзистори формують в одному кристалі й розміщують в одному корпусі.

Rе разом із джерелом від’ємної напруги

повинні утворити джерело струму,

величина сили струму якого позначена

через І0.

повинні утворити джерело струму,

величина сили струму якого позначена

через І0.

Розглянемо випадки:

а) Uвх1 = Uвх2 = 0

Тоді

![]() і

і ![]() .

.

Виразивши спад напруги на колекторному резисторі через І0, отримаємо:

![]() ;

; ![]() .

.

Оскільки RК1 і RК2 рівні, то при Uвх1 = Uвх2 =0 отримаємо різницю напруг між входами 1 та 2:

∆Uвих = Uвих2 – Uвих1 = 0.

б) Uвх1 Uвх2, Uвх1 > 0, Uвх2 < 0

![]() ;

; ![]() ;

;

Iк1 + Ік2 І0.

Дана рівність наближена тому, що не враховано Іб.

Тепер різниця вихідних напруг дорівнюватиме:

∆Uвих = Uвих2 – Uвих1 = (Iк1 – Ік2)∙Rк.

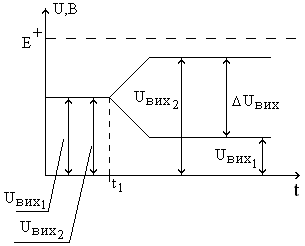

На часовій діаграмі при зміні вхідних сигналів це має вигляд:

Рис. 93

в) Uвх1 = Uвх2 > 0

У випадку ідеального диференційного підсилювача різниця напруг між вихідними клемами у випадку синфазного сигналу залишиться такою, що дорівнює нулеві. У випадку ж реального диференційного підсилювача вказана різниця напруг буде відмінна від нуля.

Для кількісної оцінки диференційного підсилювача за коефіцієнтом підсилення синфазного та диференційного (парафазного) сигналів користуються поняттям коефіцієнта підсилення для одного й іншого випадку. Величини коефіцієнтів підсилення диференційного та синфазного сигналів з достатньою точністю описується формулами:

![]() -

коефіцієнт підсилення диференційного

сигналу;

-

коефіцієнт підсилення диференційного

сигналу;

![]() - коефіцієнт підсилення синфазного

сигналу.

- коефіцієнт підсилення синфазного

сигналу.

Стійкість диференційних підсилювачів (ДП) до синфазних завад оцінюється відношенням:

![]() .

.

Rе виконує роль резистора оберненого зв’язку одночасно для лівого і правого плеча ДП. Щоб забезпечити глибину ОЗ, наприклад, на рівні А 80дБ, опір емітерного резистора повинен складати приблизно 200 кОм. Для транзисторів малої потужності колекторний струм номінальної величини складає Ік ~ 2мА, отже, струм джерела струму І0= 4 мА, тоді спад напруги на Re:

![]() .

.

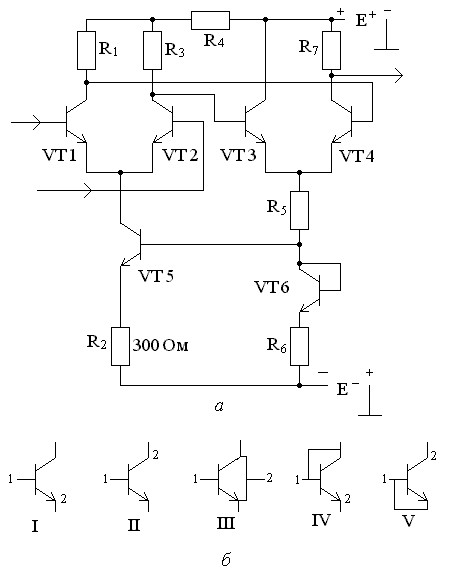

Забезпечення таких високих напруг пов’язане з певними технічними труднощами. До того ж під’єднання схеми з відносно низькими робочими напругами до високовольтного джерела вимагає додаткових заходів безпеки. У зв’язку з цим як елемент ОЗ використовують пристрій, який володіє малим статичним, але високим динамічним опором. Схема зі спільною базою має властивості, що забезпечують високий динамічний вихідний опір при відносно малій величині напруги Uке, тобто величина статичного опору даної схеми відносно мала. Рис. 94

В схемі рис.94, а в якості емітерного

резистора Rе

використовують транзистор VT5, ввімкнений

за схемою зі спільною базою, та резистор

R2.

Струм колектора транзистора VT5 задається

напругою стабілізації стабілітрона

VT6 та спадом напруги на резисторі R6.

У привідкритого VT5 напруга Uке

~ 3 В. При даних номіналах схеми і величині

колекторного струму VT5 І0

= 4 мА, спад напруги на еквівалентному

резисторі буде:

схемі рис.94, а в якості емітерного

резистора Rе

використовують транзистор VT5, ввімкнений

за схемою зі спільною базою, та резистор

R2.

Струм колектора транзистора VT5 задається

напругою стабілізації стабілітрона

VT6 та спадом напруги на резисторі R6.

У привідкритого VT5 напруга Uке

~ 3 В. При даних номіналах схеми і величині

колекторного струму VT5 І0

= 4 мА, спад напруги на еквівалентному

резисторі буде:

![]() .

.

Величина ж динамічного вихідного опору VT5 складає одиниці мегаом.

Схема (рис. 94, а) містить вхідний диференційний каскад (VT1, VT2), каскад переходу від диференційної схеми (схеми з двома виходами) до звичайної однофазної схеми (транзистори VT3, VT4) та параметричний стабілізатор, який містить баластний резистор R5, стабілітрон VT6 та резистор R6. За допомогою R6 здійснюється підгонка величини стабілізованої напруги. Введення резистора R6 дещо погіршує коефіцієнт стабілізації, оскільки цей елемент має рівні за величиною динамічний та статичний опори. Як стабілітрони використано транзистор VT6, ввімкнений за однією з п’яти можливих діодних схем (рис. 94, б).

З технологічного погляду більш виправданим є формування транзисторної, ніж діодної структури, при цьому простіше забезпечити задані параметри стабілітрона. У залежності від того, які електроди транзистора використовуються як робочі, ми отримаємо різні напруги пробою, а отже, різні напруги стабілізації. Найвищу напругу стабілізації одержимо при використанні найбільш високоомного базо-колекторного переходу (випадок II, рис. 94, б).

63. Термокомпенсація та термостатування як метод зниження дрейфу нуля підсилювачів постійного струму. Необхідність пониження потенціалу електродів підсилюючих елементів в підсилювачах постійного струму.

Зменшення величини дрейфу нуля досягається використанням таких заходів:

Термостабілізація.

Термокомпенсація.

Введення загального від’ємного ОЗ.

Використання диференційних (різницевих) схем.

Використання схем з перетворенням сигналу.