- •Лінійні блокові систематичні коди, генеруючи та перебіркова матриця.

- •2. Циклічні коди

- •3. Згорткові коди.

- •4. Імпульсно-кодова модуляція

- •Импульсно-кодовая модуляция

- •7. Властивості лінійних дискретних систем

- •Властивість пам'яті лінійних дискретних систем

- •Стійкість лінійних дискретних систем

- •Оцінка стійкості по імпульсної характеристиці: критерій стійкості

- •Приклад

- •8. Дискретні перетворення сигналів

- •7.5.1. Спектр Фур'є неперервних та дискретних сигналів.

- •10 .Передавальна функція лінійних дискретних систем

- •11 Види ліній зв’язку та їх основні властивості

- •12.Первинні параметри кола

- •Вторинні параметри кола

- •13 Поверхневий ефект. Причина явища.

- •14.Ефект близькості в двопровідній лінії зв’язку. Причина явища.

- •15. Конструктивні елементи кабелів електрозв’язку

- •16. Стандартні інтегральні мікросхеми ттл-логіки

- •17. Типи технологій логічних мікросхем

- •18. Параметри логічних імс

- •19. Методи покращення завадостійкості радіоелектронних пристроїв на інтегральних мікросхемах

- •20. Перетворювачі код-аналог на матрицях r-2r

- •Класифікація зп

- •Перша цифра 1,5,6,7 – напівпровідникові мікросхеми

- •Статичні запам’ятовуючі пристрої

- •Динамічні зп

- •Асинхронна пам’ять (fpm edo bedo)

- •Синхронна пам'ять

- •Пам'ять з внутрішнім кешом

- •Відеопам'ять

- •24. 2.1. Амплітудна модуляція (am)

- •26 Генератори із зовнішнім збудженням.

- •26. Генератори із зовнішнім збудженням.

- •26/1 Генератор із зовнішнім збудженням

- •Принципові схеми генераторів із зовнішнім збудженням

- •2. Схема з загальною сіткою

- •3. Схема з загальним анодом

- •27. Аналіз амплітудно-модульованого коливання

- •28. Основні технічні характеристики антен

- •29.Метод дзеркальних зображень.Дыаграми напрямленосты розыщених над землею выбраторыв.

- •31.Режими роботи фідерів. Коефіцієнти стоячої та біжучої хвиль.

- •32.Трансформуючі властивості фідерних ліній.

- •33.Вплив землі на випромінювання антени

- •35.Елементарний магнітний диполь

- •36.Елементарна випромінююча щілина

- •38. Дзеркальні антени.

- •39. Лінзова антена

- •Принцип дії

- •41Канали зв’язку в інформаційно- вимірювальних системах.

- •42. Види і склад інформаційно-вимірювальних комплексів.

- •43. Параметри радіоелектронних засобів та їх вплив на електромагнітну сумісність.

- •44. Структура електромагнітного поля та принципи екранування.

- •45. Індустріальні джерела завад.

- •Ймoвірнісні методи в задачах оцінки та забезпечення надійності рез.

- •Густина розподілу безвідмовної роботи , () ()

- •53. Активна, реактивна і повна потужності в колах синусоїдального струму.

- •Перехідні процеси велектричних колах

- •Закони комутації

- •Усталений режим. Перехідний режим : струми і напруги перехідного режиму.

- •Порядок розрахунку перехідного процесу класичним методом

- •58.Спектри періодичних і неперіодичних сигналів

- •58. Спектри періодичних і неперіодичних сигналів

- •59. Випадковий процес. Основні моментні функції.

- •60.Спектральний метод аналізу проходження випадкових сигналів через лінійні електричні кола.

- •Середнє значення вихідного сигналу

- •Тому, виконуючи усереднення в обох частинах рівності (8.2), матимемо:

- •Отже, вихідний сигнал зв'язаний з вхідним сигналом співвідношенням

- •61. Тепловий шум резистора, формула Найквіста.

- •8.3.1.1. Формула Найквсіта

- •У цій формулі вважатимемо, що і знайдемо дисперсію . Тут же врахуємо, що, білий шум - це випадковий процес зі сталим на всіх частотах спектром потужності . Тоді

- •З іншого боку,

- •62. Диференційний підсилювач (рис. 113).

- •6.2.4. Диференційні (різницеві) схеми

- •6.2. Методи пониження дрейфу нуля підсилювача.

- •6.2.1. Термостабілізація

- •6.2.2. Термокомпенсація

- •64. Методи пониження потенціалу електродів підсилювальних елементів в підсилювачах постійного струму.

- •65. Підсилювачі постійного струму з перетворенням сигналу.

- •66. Способи задання та стабілізації положення робочої точки.

- •67.Суматори аналогових сигналів на операційних підсилювачах

- •Автоматичнепідстроюваннячастоти

- •4.1 Частотне автоматичне підстроювання частоти

- •71.Інтеггруюча та диференціюючи ланка на оп

- •72. Інвертуючий підсилювач на оп.

- •73. Неінвертуючий підсилювач на оп.

- •74. Аналого – дискретні підсилювачі.

- •3.3 Аналого – дискретні підсилювачі.

- •75. Схемотехнічна реалізація підсилювачів класу d.

- •77/. Вхідні кола

- •78.Розбивка робочого діапазону частот на піддіапазони

- •79. Резонансні підсилювачі.

- •§5.2 Смугові підсилювачі.

- •§6 Перетворювачі частоти.

- •§6.1 Принципи перетворення частоти

- •§6.2 Побічні продукти перетворення.

- •§6.3 Типи перетворювачів частоти.

- •Нормальний закон розподілу випадкової похибки. Середньо-квадратичне значення та дисперсія випадкової похибки.

- •85.Способи вимирювання частоти і часових інтервалів методом калібровочних міток

- •86. Принципи сучасного телебачення. Фізіологічні властивості ока, їх вплив на технічні рішення в телебаченні.

- •87.Параметры разложения изображения в телевидении

- •88.Принципи кольорового телебачення

- •89. Система кольорового телебачення ntsc і pal (спрощенні схеми та спосіб кодування)

- •91. Типи мікрофонів основні характеристики мікрофонів.

- •92. Акустичні фільтри. Пристрої на поверхнево-акустичних хвилях. Приклади застосування.

- •93. Ефект Доплера. Конус Маха. Ультразвукові прилади на основі ефекту Доплера.

- •94. Застосування ультразвуку в медичній галузі.

- •95. Енергетичні характеристики звукового поля. Акустичний імпеданс.

- •96. Принцип дії пасивного інфрачервоного детектора руху.

- •97 . Загальна модель системи захисту об’єкту.

- •98. Типи датчиків, які використовуються в системі протипожежного захисту.

- •99. Класифікація протикрадіжкових систем захисту.

- •100. Основні складові базової системи відеоспостереження.

- •101. Якісні показники та критерії оптимального виявлення та розрізнення сигналів.

- •102.Характеристики сигналів та завад в ртс

- •103. Фазовий метод вимірювання кутових координат.

- •104. Принципи отримання інформації радіолокації

- •105. Залежність дальності спостереження від різних факторів. Узагальнене рівняння радіолокації у вільному просторі.

- •Рівняння дальності при віддзеркаленні радіохвиль від Земної поверхні.

- •Гранична дальність дії. Зона видимості.

- •Вплив умов розповсюдження радіохвиль на дальність дії рлс.

- •Вплив затухання радіохвиль на дальність дії.

- •106.Законодавче та нормативно-технічне забезпечення охорони праці

- •107.Відповідальність за порушення законодавства про охорону праці

- •109. Дія електричного струму на організм людини

- •110. Вплив шуму на організм людини

19. Методи покращення завадостійкості радіоелектронних пристроїв на інтегральних мікросхемах

Завадостійкість. Базовий елемент ІМС у статичному режимі може перебувати в одному із двох стійких станів (0 або 1). Із цієї причини розрізняють статичну завадостійкість ЛЕ (логічний елемент) за рівнем 0 (Uno)і за рівнем 1 (Un1). Статична завадостійкість базових елементів ІМС визначається значенням напруги, що може бути подане на вхід ІМС щодо рівня 0 або 1, не викликаючи її помилкового спрацьовування (наприклад, перехід зі стану 1 у стан 0 або навпаки).

Напруга перешкоди або підвищує, або знижує вхідну напругу. Якщо на вході діє напруга логічного 0 (U0), то небезпечні перешкоди, що мають позитивну полярність, тому що вони підвищують вхідну напругу, що може привести до збою в роботі, тобто помилковій зміні вихідних напруг у цифровому пристрої. При надходженні на вхід напруги логічної 1 (U1) і напруги перешкоди негативної полярності також можливо помилкове перемикання. Максимально припустимі постійні напруги перешкоди позитивної полярності (при напрузі логічного 0 на вході) і негативної полярності (при напрузі логічної 1 на вході) визначають завадостійкість ЛЕ стосовно статичного (довгостроково діючим) перешкодам.

Внутрішні перешкоди в цифровому пристрої виникають при перемиканні ЛЕ, тому їхня амплітуда пропорційна логічному перепаду Uл.

Логічним перепадом називається різниця напруг логічної 1 і логічного 0:

![]() .

.

Для оцінки завадостійкості ЛЕ крім напруг Uп1 й Uп0 використовують відносні величини:

![]() ;

;

![]() ,

,

названі коефіцієнтом завадостійкості.

Для підвищення завадостійкості необхідно збільшувати логічний перепад і зменшувати час перемикання ЛЕ зі стану 1 у стан 0 і навпаки.

Споживана потужність ЛЕ (потужність, споживана ЛЕ від джерела живлення) залежить від його логічного стану, тому що змінюється струм Iи.п. у ланцюзі живлення. ЛЕ споживає струм

![]() при

при

![]() ;

;

![]() при

при

![]() .

.

Тому середня споживана потужність у статичному режимі.

![]() .

.

Знаючи

середню потужність і число ЛЕ в цифровому

пристрої Nл.э.,

можна обчислити середню потужність,

споживану пристроєм; вона дорівнює

![]() .

Зменшити споживану потужність можна,

знизивши напругу або струм живлення.

Однак при цьому понизяться завадостійкість,

а для багатьох типів ЛЕ й швидкодія.

Найбільш ефективний спосіб зменшення

потужності Pср

реалізований у ЛЕ на КМДН-транзисторах

(комплементарний метал-діелектрик-напівпровідник).

У цих елементах струми в статичному

режимі малі, а потужність споживається

тільки при

перемиканні.

Потужність, споживану додатково в

процесі перемикання, називають динамічною.

Вона пропорційна частоті перемикання

ЛЕ. Тому динамічну потужність визначають

при заданій робочій частоті, близької

до максимального.

.

Зменшити споживану потужність можна,

знизивши напругу або струм живлення.

Однак при цьому понизяться завадостійкість,

а для багатьох типів ЛЕ й швидкодія.

Найбільш ефективний спосіб зменшення

потужності Pср

реалізований у ЛЕ на КМДН-транзисторах

(комплементарний метал-діелектрик-напівпровідник).

У цих елементах струми в статичному

режимі малі, а потужність споживається

тільки при

перемиканні.

Потужність, споживану додатково в

процесі перемикання, називають динамічною.

Вона пропорційна частоті перемикання

ЛЕ. Тому динамічну потужність визначають

при заданій робочій частоті, близької

до максимального.

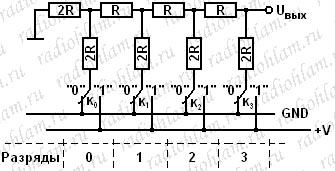

20. Перетворювачі код-аналог на матрицях r-2r

ЦАП на основі резистивної матриці R-2R і його реалізація на мікроконтролері.

1) Використання матриці R-2R у якості паралельного ЦАП.

Розглянемо матрицю, зображену на малюнку.

Очевидно, що якщо всі ключі перебувають у положенні "0", та вихідна напруга буде дорівнює нулю.

Можна порахувати, що якщо ключ нульового розряду встановлений у положення "1", а всі інші в положення "0", то

Uвых=V*1/16,

якщо ключ першого розряду встановлений у положення "1", а всі інші в положення "0", то

Uвых=V*1/8,

якщо ключі нульового й першого розрядів установлені в положення "1", а всі інші в положення "0", то

Uвых=V*(1/16+1/8), і так далі...

У загальному випадку одержимо: Uвых=V*(А0*1/16+А1*1/8+А2*1/4+А3*1/2), де Аi=1, якщо відповідний ключ (Кi) перебуває в положенні "1" й Аi=0, якщо відповідний ключ перебуває в положенні "0".

Тобто, замикаючи різними способами ключі ДО0...ДО3 (або, по іншому говорячи, подаючи на вхід чотирьохбітне число A3A2A1A0) ми можемо одержати 24=16 різних значень вихідної напруги (від Uвых=0 до Uвых=V*(1-1/16) із кроком D=V*1/16).

Таким чином, дана схема являє собою найпростіший паралельний чотирьохбітний цифро-аналоговий перетворювач.

Аналогічним способом можна побудувати восьми, десяти, дванадцяти й взагалі n-бітний ЦАП.

У загальному випадку, для n-бітного ЦАП будемо мати: Uвых=V*S(Ai*1/2n-i), де i - номер розряду (i=0, 1, 2 ... n-1), Ai=1, якщо відповідний ключ замкнуть на шину живлення й Ai=0, якщо відповідний ключ замкнуть на загальне проведення.

крок у цьому випадку визначається по формулі: D=V/2n, де n - загальне число розрядів

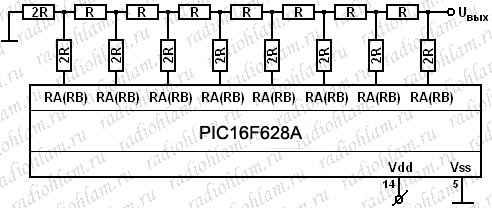

2) Реалізація ЦАП за схемою R-2R на мікроконтролері.

Припустимо у вас немає ЦАП, але є звичайний контролер з достатньою кількістю невикористовуваних ніг. Чи можна, використовуючи мікроконтролер, зробити ЦАП самостійно? Так звичайно ж можна.

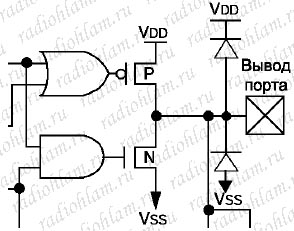

Візьмемо, приміром, контролер PIC16F628A і подивимося в документації, як улаштовані його виходи:

Як бачимо, - на виході два польовика, коли на виході "0" - верхній закритий, нижній відкритий, коли на виході "1" - навпаки, верхній відкритий, нижній закритий. Це саме те, що нам потрібно, - можемо підтягти вихід або до землі, або до харчування. Тоді, задіявши вісім таких висновків і матрицю R-2R, - одержимо восьмибітний цифро-аналоговий перетворювач:

21.ОЗП

Запам’ятовуючі пристрої

Призначення – зберігання інформації на протязі певного відрізку часу.

Запам’ятовуючий пристрій звичайно містить велику кількість елементів пам’яті.

В ЕОМ служить для того, щоб зберігати програму обробки даних, а також проміжні та кінцеві результати обробки.

Структура ЗП складається з n комірок пам’яті, кожна з яких зберігає слово з m бітів. За допомогою двійкової адресації можна викликати n комірок пам’яті ЗП і по командам ЗАПИС/ЧИТАННЯ записати або прочитати в них n слів. При вказанні об’єму ЗП слід користуватись системою позначень, що явно вказує скілька слів та якої довжини може містити даний ЗП. Так, наприклад, ми говоримо про ЗП об’ємом 256х4 біт, який містить 256 комірок пам’яті по 4 біти в кожній. Якщо ми говоримо про ЗП об’ємом 1К4, 2К8 або 16К1, то маємо на увазі структури, що відповідають 1024х4, 2048х8, 65536х1 біт відповідно.