- •1.1. Поняття операційної системи.

- •1.5. Поняття асемблера, компілятора, транслятора, інтерпретатора.

- •1.6. Завантажувачі. Завдання завантажувачів. Принципи побудови завантажувачів.

- •1.7. Принципи об’єктно-орієнтованого програмування (парадигми програмування, поняття класу).

- •1.8. Наслідування (Просте наслідування. Множинне наслідування).

- •1.9. Інкапсуляція. Поняття, сфери застосування.

- •1.10. Поліморфізм. Поняття, сфери застосування.

- •1.11. Принципи розробки розподілених клієнт-серверних програм. Особливості розробки мережевих програм з використанням сокетів.

- •2.1 Багаторівнева комп’ютерна організація – структура й призначення рівнів.

- •2.2 Схема комп’ютера з єдиною шиною. Основні характеристики та принципи роботи шини комп’ютера.

- •2.3 Структура процесора, внутрішні блоки, види регістрів.

- •2.4 Команди процесора, структура команд. Цикл Фон-Неймана.

- •2.5 Структуру пам’яті комп’ютера. Елементи статичної та динамічної пам’яті.

- •2.6 Переривання, типи, алгоритм обробки переривання процесором.

- •2.7 Організація оперативної пам’яті, адресний простір, сегменти пам’яті, дескриптори сегментів.

- •3.1 Загальні відомості з теорії систем. Класифікація систем.

- •3.2 Поняття вимірювальної шкали. Види шкал.

- •3.3 Показники якості та ефективності та крітерії їх оцінювання.

- •3.4 Вирішення багатокрітеріальних задач.

- •3.5 Вирішення задачі вибору.

- •3.6 Декомпозиція. Компроміси між повнотою та простотою.

- •3.7 Агрегування. Види агрегування.

- •3.8 Поняття експертних методів. Експертні системи.

- •4.1. Методи розрахунку часових параметрів і критичних шляхів мережевої моделі проекту. Табличний метод.

- •4.2. Методи розрахунку часових параметрів і критичних шляхів мережевої моделі проекту. Матричний метод визначення часових параметрів.

- •4.3. Метод класичного варіаційного числення. Рішення варіаційної задачі із закріпленими граничними крапками.

- •4.4. Метод класичного варіаційного числення. Рівняння Ейлера-Лагранжа.

- •4.5. Постановка задачі оптимального управління. Класифікація задач оптимального управління.

- •4.6. Характеристика керованості і спостережності. Постановка завдання. Критерії керованості і спостережності.

- •6.1 Основні теоретико-множинні (об’єднання, пересічення, віднімання, декартовий добуток) операції реляційної алгебри. Коротка характеристика та приклади.

- •6.2. Основні нормальні форми. Характеристика і приклади відносин, що знаходяться в 1нф, 2нф, 3нф.

- •Id, category, product1, product2, product3

- •6.3. Основні оператори мови маніпулювання даними. Оператор вибірки даних (одно- і багатотабличні запити оператора select).

- •7.2) Модели детерминированных цифровых сигналов

- •7.3. Алгоритми оптимальної обробки при розрізненні двійкових сигналів.

- •7.4. Потенціальна завадостійкість при прийомі ам, чм та фм сигналів.

- •7.5. Багатократні та комбіновані методи модуляції.

- •7.6. Методи боротьби з помилками, що виникають в каналах зв’язку. Завадостійке кодування.

- •7.7 Основні параметри завадостійких кодів. Принципи виявлення та виправлення помилок.

- •7.8 Циклічні коди. Згортальні коди.

- •7.9 Статичні методи стиснення інформації Алгоритм арифметичного стиснення.

- •7.10 Оптимальне кодування інформації. Алгоритми формування коду Хофмана та Шенона-Фано.

- •7.11 Аналогочислові перетворення безперервного сигналу на базі теореми Котельникова в.А.

- •7.12 Пропускна спроможність двійкового каналу зв’язку з перешкодами та без перешкод.

- •8.1. Протоколи фізичного рівня.

- •8.2. Характеристика лінійних сигналів, що використовуються в комп’ютерних мережах.

- •8.4. Загальні характеристики канального рівня.

- •8.5. Протокол hdlc.

- •8.6. Методи доступу в мережу.

- •8.7. Протокол ip. Адресація в ip-мережах.

- •8.8. Протокол tcp.

- •9.1 Алгоритм принятия решения по управлению кс

- •9.2. Архітектура систем управління комп’ютерними мережами.

- •9.3. Управління потоком інформації шляхом раціонального вибору параметрів протоколу.

- •9.4. Управління обслуговуванням різнорідного трафіку: дисципліни обслуговування, їх переваги та недоліки.

- •9.5. Управління якістю обслуговування. Забезпечення якості обслуговування шляхом управління мережевими ресурсами.

- •9.6. Основні стандарти управління комп’ютерними мережами. Мережеве управління за стандартом tmn: визначення, функціональні області, інтерфейси.

- •9.7. Модель управління протоколів snmp та cmip: структура, стандартизовані елементи, переваги та недоліки.

- •10.1. Основні концепції побудови обчислювальних систем, що самоорганізуються.

- •10.2. Класифікація процесорів по архітектурі системи команд (cisc, risc).

- •10.3. Показники ефективності паралельних часових моделей алгоритмів.

- •10.4. Основні ознаки класифікації Флинна. Фрагмент класифікації Флинна.

- •10.5. Відмінності командної чарунки в vliw-процесорі від командної чарунки процесора з послідовною обробкою даних.

- •11.1Стадії та етапи створення асу тп.

- •11.2 Склад і коротка характеристика розділів технічного проекта.

- •11.3 Склад і зміст проектних рішень з технічного забезпечення.

- •11.4Склад і задачі організацій, що беруть участь у роботах зі створення асу тп.

- •11.5Перелік видів випробувань асу тп та їх короткий зміст.

- •11.6 Розрахунок вартості проектних робіт ресурсним методом.

- •11.7 Застосування елементних кошторисних норм для розрахунку вартості пусконалагоджувальних робіт.

2.7 Організація оперативної пам’яті, адресний простір, сегменти пам’яті, дескриптори сегментів.

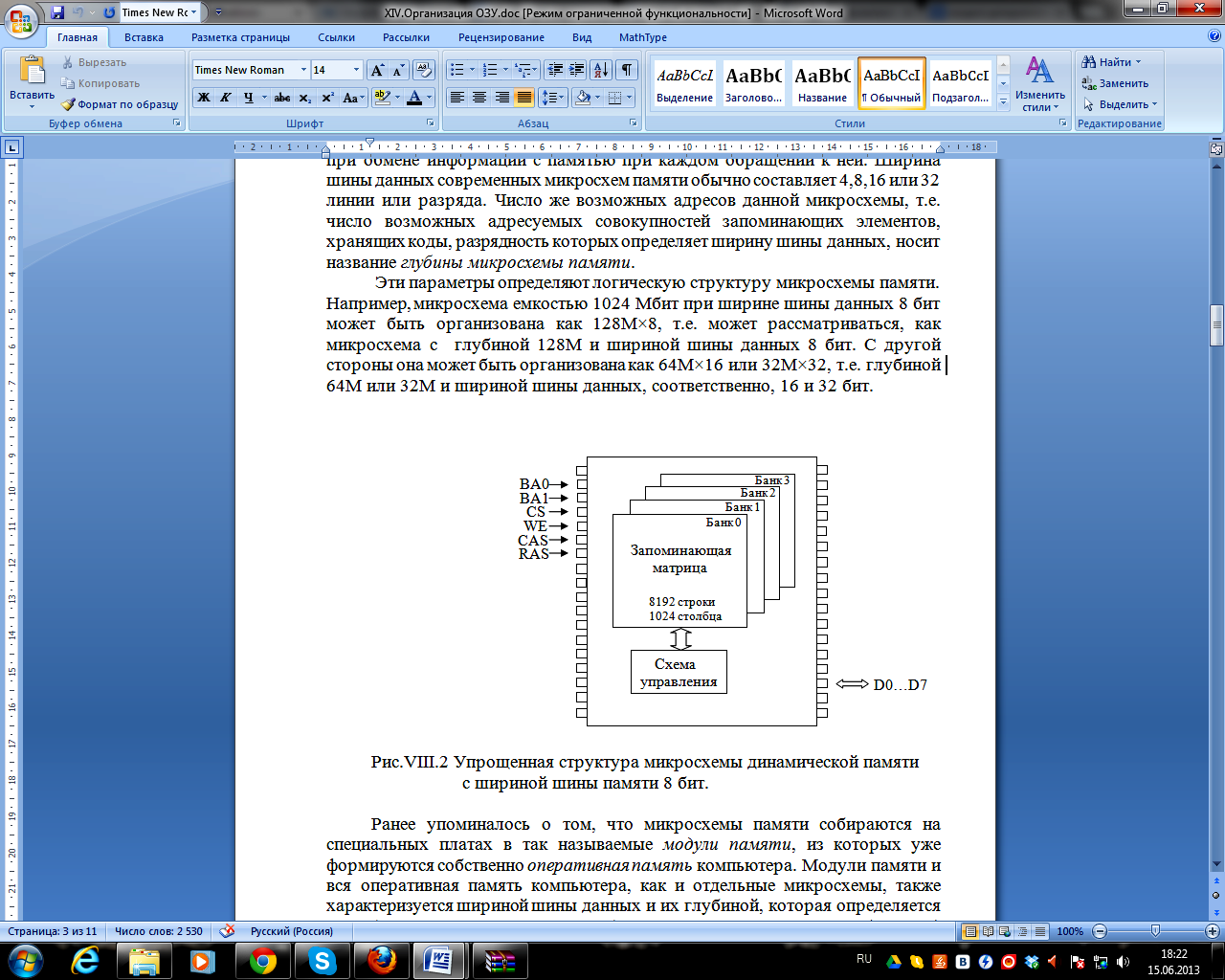

В современных компьютерах основной элементарной адресуемой единицей информации является байт. Поэтому в устройствах оперативной памяти каждая запоминающая ячейка состоит из восьми двоичных элементов памяти, в DRAM – запоминающих емкостей. Каждая микросхема памяти организована как матрица запоминающих ячеек в виде строк и столбцов. Запоминающие ячейки адресуются, т.е. приводятся в состояние готовности для операции записи или считывания из них информации, при совпадении сигналов возбуждения соответствующих строк и столбцов, которые поступают от дешифраторов старших и младших разрядов кода адреса.

Физически

DRAM-память

представляет собой набор запоминающих

ячеек, которые состоят из конденсаторов

и транзисторов, расположенных внутри

полупроводниковых микросхем памяти.

При отсутствии подачи электроэнергии к памяти этого типа происходит разряд конденсаторов, и память опустошается (обнуляется). Для поддержания необходимого напряжения на обкладках конденсаторов ячеек и сохранения их содержимого, их необходимо периодически подзаряжать, прилагая к ним напряжения через коммутирующие транзисторные ключи.

Для ПК характерно типовое распределение непосредственно адресуемой памяти (0…1 Мбайт) между оперативной и постоянной памятью.

Распределение адресного пространства непосредственно адресуемой памяти:

|

Стандартная память 640 Кбайт (Conventional Memory) |

Верхняя память 384 Кбайт (Upper Memory Area – UMA) | |||

|

|

|

|

| |

|

Область служебных программ и данных ОС 64 Кбайт |

Область программ и данных операционной системы и пользователя

576 Кбайт |

Служебная память

256 Кбайт |

Область ПЗУ (программ BIOS)

128 Кбайт | |

|

Оперативная память (ОЗУ) |

ПЗУ | |||

Стандартная (базовая) память доступна DOS и программам реального режима. В некоторых системах верхняя граница этой памяти сдвигается к 704 Кбайт.

Верхняя память зарезервирована для системных нужд. В ней размещаются области буферной памяти адаптеров (например, видеопамять) и постоянная память (BIOS с расширениями).

Область памяти выше первого мегабайта носит название расширенной памяти. Доступ к ячейкам расширенной памяти возможен либо при использовании специальных программ-драйверов, либо в защищенном режиме работы процессора. В реальном режиме расширенная память может быть использована главным образом для хранения данных и некоторых программ ОС.

Распределение адресного пространства основной памяти:

|

Непосредственно адресуемая память |

Расширенная память | ||

|

Стандартная память

0…640 Кбайт |

Верхняя память

640 Кбайт...1024 Кбайт |

Высокая память HMA (High Memory Area)

1024 Кбайт………1088 Кбайт |

Дополнительная память

> 1088 Кбайт |

Сегментная адресация памяти — схема логической адресации памяти компьютера в архитектуре x86. Линейный адрес конкретной ячейки памяти, который в некоторых режимах работы процессора будет совпадать с физическим адресом, делится на две части: сегмент и смещение. Сегментом называется условно выделенная область адресного пространства определённого размера, а смещением — адрес ячейки памяти относительно начала сегмента. Базой сегмента называется линейный адрес (адрес относительно всего объёма памяти), который указывает на начало сегмента в адресном пространстве. В результате получается сегментный (логический) адрес, который соответствует линейному адресу база сегмента+смещение и который выставляется процессором на шину адреса.

Дескриптор сегмента (в архитектуре x86) — служебная структура в памяти, которая определяет сегмент. Длина дескриптора равна 8 байт.

Структура сегментного дескриптора

База (32 бита) — начало сегмента в линейной памяти

Лимит (20 бит) — (размер сегмента в байтах)-1 (База+Лимит = линейный адрес последнего байта)

Права доступа (12 бит) — флаги, определяющие наличие сегмента в памяти, уровень защиты, тип, разрядность + один пользовательский флаг

Байт прав доступа (AR, англ. Access Rights, биты 8-15 на рисунке):

Бит P определяет доступность сегмента (0 — сегмента нет, 1 — есть). При обращении к сегменту со сброшенным битом P происходит исключение #NP, обработчик которого может загрузить/создать сегмент.

Номер привилегий DPL содержит 2-битный номер (0-3), определяющий, к какому уровню (кольцу) защиты относится этот сегмент.

Тип сегмента (биты 8-12 на рисунке). Старший бит (S) определяет сегмент как системный (S=0) или пользовательский (S=1). Значение прочих бит для системных и пользовательских сегментов описано в таблице: