- •1.1. Поняття операційної системи.

- •1.5. Поняття асемблера, компілятора, транслятора, інтерпретатора.

- •1.6. Завантажувачі. Завдання завантажувачів. Принципи побудови завантажувачів.

- •1.7. Принципи об’єктно-орієнтованого програмування (парадигми програмування, поняття класу).

- •1.8. Наслідування (Просте наслідування. Множинне наслідування).

- •1.9. Інкапсуляція. Поняття, сфери застосування.

- •1.10. Поліморфізм. Поняття, сфери застосування.

- •1.11. Принципи розробки розподілених клієнт-серверних програм. Особливості розробки мережевих програм з використанням сокетів.

- •2.1 Багаторівнева комп’ютерна організація – структура й призначення рівнів.

- •2.2 Схема комп’ютера з єдиною шиною. Основні характеристики та принципи роботи шини комп’ютера.

- •2.3 Структура процесора, внутрішні блоки, види регістрів.

- •2.4 Команди процесора, структура команд. Цикл Фон-Неймана.

- •2.5 Структуру пам’яті комп’ютера. Елементи статичної та динамічної пам’яті.

- •2.6 Переривання, типи, алгоритм обробки переривання процесором.

- •2.7 Організація оперативної пам’яті, адресний простір, сегменти пам’яті, дескриптори сегментів.

- •3.1 Загальні відомості з теорії систем. Класифікація систем.

- •3.2 Поняття вимірювальної шкали. Види шкал.

- •3.3 Показники якості та ефективності та крітерії їх оцінювання.

- •3.4 Вирішення багатокрітеріальних задач.

- •3.5 Вирішення задачі вибору.

- •3.6 Декомпозиція. Компроміси між повнотою та простотою.

- •3.7 Агрегування. Види агрегування.

- •3.8 Поняття експертних методів. Експертні системи.

- •4.1. Методи розрахунку часових параметрів і критичних шляхів мережевої моделі проекту. Табличний метод.

- •4.2. Методи розрахунку часових параметрів і критичних шляхів мережевої моделі проекту. Матричний метод визначення часових параметрів.

- •4.3. Метод класичного варіаційного числення. Рішення варіаційної задачі із закріпленими граничними крапками.

- •4.4. Метод класичного варіаційного числення. Рівняння Ейлера-Лагранжа.

- •4.5. Постановка задачі оптимального управління. Класифікація задач оптимального управління.

- •4.6. Характеристика керованості і спостережності. Постановка завдання. Критерії керованості і спостережності.

- •6.1 Основні теоретико-множинні (об’єднання, пересічення, віднімання, декартовий добуток) операції реляційної алгебри. Коротка характеристика та приклади.

- •6.2. Основні нормальні форми. Характеристика і приклади відносин, що знаходяться в 1нф, 2нф, 3нф.

- •Id, category, product1, product2, product3

- •6.3. Основні оператори мови маніпулювання даними. Оператор вибірки даних (одно- і багатотабличні запити оператора select).

- •7.2) Модели детерминированных цифровых сигналов

- •7.3. Алгоритми оптимальної обробки при розрізненні двійкових сигналів.

- •7.4. Потенціальна завадостійкість при прийомі ам, чм та фм сигналів.

- •7.5. Багатократні та комбіновані методи модуляції.

- •7.6. Методи боротьби з помилками, що виникають в каналах зв’язку. Завадостійке кодування.

- •7.7 Основні параметри завадостійких кодів. Принципи виявлення та виправлення помилок.

- •7.8 Циклічні коди. Згортальні коди.

- •7.9 Статичні методи стиснення інформації Алгоритм арифметичного стиснення.

- •7.10 Оптимальне кодування інформації. Алгоритми формування коду Хофмана та Шенона-Фано.

- •7.11 Аналогочислові перетворення безперервного сигналу на базі теореми Котельникова в.А.

- •7.12 Пропускна спроможність двійкового каналу зв’язку з перешкодами та без перешкод.

- •8.1. Протоколи фізичного рівня.

- •8.2. Характеристика лінійних сигналів, що використовуються в комп’ютерних мережах.

- •8.4. Загальні характеристики канального рівня.

- •8.5. Протокол hdlc.

- •8.6. Методи доступу в мережу.

- •8.7. Протокол ip. Адресація в ip-мережах.

- •8.8. Протокол tcp.

- •9.1 Алгоритм принятия решения по управлению кс

- •9.2. Архітектура систем управління комп’ютерними мережами.

- •9.3. Управління потоком інформації шляхом раціонального вибору параметрів протоколу.

- •9.4. Управління обслуговуванням різнорідного трафіку: дисципліни обслуговування, їх переваги та недоліки.

- •9.5. Управління якістю обслуговування. Забезпечення якості обслуговування шляхом управління мережевими ресурсами.

- •9.6. Основні стандарти управління комп’ютерними мережами. Мережеве управління за стандартом tmn: визначення, функціональні області, інтерфейси.

- •9.7. Модель управління протоколів snmp та cmip: структура, стандартизовані елементи, переваги та недоліки.

- •10.1. Основні концепції побудови обчислювальних систем, що самоорганізуються.

- •10.2. Класифікація процесорів по архітектурі системи команд (cisc, risc).

- •10.3. Показники ефективності паралельних часових моделей алгоритмів.

- •10.4. Основні ознаки класифікації Флинна. Фрагмент класифікації Флинна.

- •10.5. Відмінності командної чарунки в vliw-процесорі від командної чарунки процесора з послідовною обробкою даних.

- •11.1Стадії та етапи створення асу тп.

- •11.2 Склад і коротка характеристика розділів технічного проекта.

- •11.3 Склад і зміст проектних рішень з технічного забезпечення.

- •11.4Склад і задачі організацій, що беруть участь у роботах зі створення асу тп.

- •11.5Перелік видів випробувань асу тп та їх короткий зміст.

- •11.6 Розрахунок вартості проектних робіт ресурсним методом.

- •11.7 Застосування елементних кошторисних норм для розрахунку вартості пусконалагоджувальних робіт.

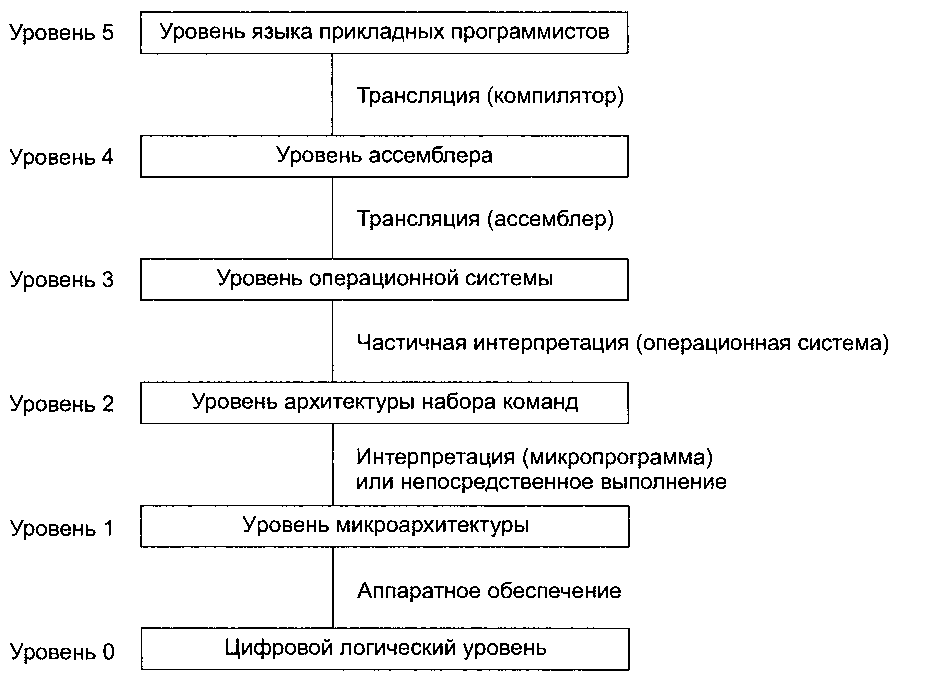

2.1 Багаторівнева комп’ютерна організація – структура й призначення рівнів.

Машинный язык - ограниченный набор простых команд, распознаваемых и выполняемых компьютером.

Разработчик при создании нового компьютера определяет машинный язык, исходя из назначения и задач. Стремятся делать машинные команды проще, чтобы избежать сложностей при конструировании и снизить затраты на электронику.

Многоуровневая компьютерная организация – подход, при котором рассматривается ряд абстракций, каждая из которых надстраивается над абстракцией более низкого уровня. Большинство современных компьютеров состоит из двух и более уровней.

Уровень 0. Цифровой логический уровень. Представляет собой аппаратное обеспечение машины. Его электронные схемы выполняют программы, написанные на языке уровня 1. Ради полноты нужно упомянуть о существовании еще одного уровня, расположенного ниже уровня 0. Он называется уровнем физических устройств.

Уровень 1. Микроархитектурный уровень. Представляет собой локальную память и АЛУ. АЛУ выполняет простые арифметические операции. Регистры вместе с АЛУ формируют тракт данных, по которому поступают данные. Основная операция тракта данных состоит в выполнении простой 2х операндной команды. Работа тракта данных контролируется микропрограммой программой или аппаратными средствами.

Уровень 2. Уровень архитектуры команд. Этот уровень включает набор машинных команд, которые выполняются микропрограммой-интерпретатором или аппаратным обеспечением.

Уровень 3. Уровень операционной системы. Этот уровень включает набор команд уровня 2. Оставшаяся часть команд интерпретируется операционной системой. Особенности уровня: набор новых команд, собственная организация памяти, способность выполнять две и более программ одновременно и др. Уровни с четвертого и выше предназначены для прикладных программистов, решающих конкретные задачи. Другое различие между уровнями 1,2,3 и уровнями 4,5 и выше — особенность языка. Машинные языки уровней 1,2 и 3 — цифровые.

Уровень 4. Уровень языка ассемблера. Представляет собой символическую форму одного из языков более низкого уровня. На этом уровне можно писать программы в приемлемой для человека форме. Эти программы сначала транслируются на язык уровня 1, 2 или 3, а затем интерпретируются соответствующей виртуальной или фактически существующей машиной. Программа, которая выполняет трансляцию, называется ассемблером.

Уровень 5. Язык высокого уровня. Обычно состоит из языков высокого уровня. Наиболее известные среди них — BASIC, С, C++, Java, LISP и Prolog. Программы, написанные на этих языках, обычно транслируются на уровень 3 или 4. Трансляторы, которые обрабатывают эти программы, называются компиляторами.

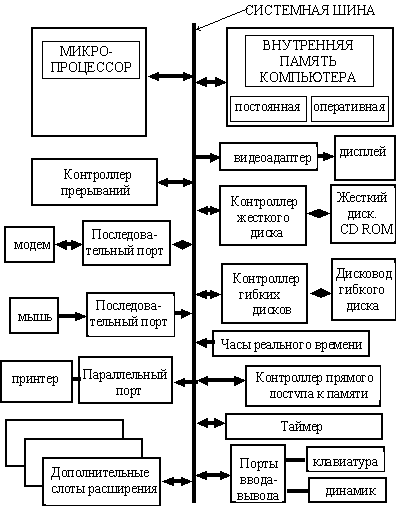

2.2 Схема комп’ютера з єдиною шиною. Основні характеристики та принципи роботи шини комп’ютера.

Аппаратная часть компьютера:

Состоит из центрального процессора, памяти (постоянная, оперативная и внешняя), устройств ввода-вывода, тактового генератора (таймера) и периферийного оборудования. Необходимый набор внешних устройств для пользователя - базовая конфигурация компьютера.

Связь между блоками осуществляется при помощи системы шин: шина адреса, шина данных, шина управления. На рисунке все эти шины объединены в одну системную шину.

Каждое устройство, подключаемое к шине, должно обеспечиваться логической схемой (адаптером), адаптирующей это устройство к правилам работы с шиной.

Работой компьютера всегда управляет программа, состоящая из отдельных команд (операторов).

Каждая команда принимается процессором, он расшифровывает содержание команды, выполняет арифметические и логические операции над данными и управляет работой всех устройств компьютера, участвующих в выполнении команды.

Для каждой операции, выполняемой процессором, требуется время, определяемое количеством тактов синхронизации.

Для синхронизации работы процессора и всех составляющих компьютера служит специальный генератор - таймер.

Открытая магистрально-модульная архитектура предназначена для того, чтобы можно было добавлять адаптеры дополнительных устройств и приспосабливать компьютеры к потребностям каждого пользователя.

История шин расширения начинается с первого компьютера IBM PC и его единственной шины ISA. (8-битная шина с тактовой частотой 4,77 МГц и скоростью передачи данных 4,77 МБ/с. 62 контакта: 8 – для данных, 20 – линии адреса, 6 – для прерываний).

Единственным способом реального повышения производительности стала разработка принципиально новой шины расширения. Работа в этом направлении привела к появлению шины PCI (тактовую частоту 33 МГц, могла быть 32- или 64-битной, а устройства работали с сигналами в 5 или 3,3 В), а в AGP(32-битная системная шина для видеокарты) (Accelerated Graphics Port).

Последней появилась шина PCI–Express. Устройства PCI Express взаимодействуют через среду, образованную коммутаторами, при этом каждое устройство напрямую связано соединением типа «точка – точка» с коммутатором. Разрядность шины – 64 бит; Пропускная способность – до 16 Гбайт/с (PCI Express х16) и до 32 Гбайт/с (PCI Express х32).