- •1.1. Поняття операційної системи.

- •1.5. Поняття асемблера, компілятора, транслятора, інтерпретатора.

- •1.6. Завантажувачі. Завдання завантажувачів. Принципи побудови завантажувачів.

- •1.7. Принципи об’єктно-орієнтованого програмування (парадигми програмування, поняття класу).

- •1.8. Наслідування (Просте наслідування. Множинне наслідування).

- •1.9. Інкапсуляція. Поняття, сфери застосування.

- •1.10. Поліморфізм. Поняття, сфери застосування.

- •1.11. Принципи розробки розподілених клієнт-серверних програм. Особливості розробки мережевих програм з використанням сокетів.

- •2.1 Багаторівнева комп’ютерна організація – структура й призначення рівнів.

- •2.2 Схема комп’ютера з єдиною шиною. Основні характеристики та принципи роботи шини комп’ютера.

- •2.3 Структура процесора, внутрішні блоки, види регістрів.

- •2.4 Команди процесора, структура команд. Цикл Фон-Неймана.

- •2.5 Структуру пам’яті комп’ютера. Елементи статичної та динамічної пам’яті.

- •2.6 Переривання, типи, алгоритм обробки переривання процесором.

- •2.7 Організація оперативної пам’яті, адресний простір, сегменти пам’яті, дескриптори сегментів.

- •3.1 Загальні відомості з теорії систем. Класифікація систем.

- •3.2 Поняття вимірювальної шкали. Види шкал.

- •3.3 Показники якості та ефективності та крітерії їх оцінювання.

- •3.4 Вирішення багатокрітеріальних задач.

- •3.5 Вирішення задачі вибору.

- •3.6 Декомпозиція. Компроміси між повнотою та простотою.

- •3.7 Агрегування. Види агрегування.

- •3.8 Поняття експертних методів. Експертні системи.

- •4.1. Методи розрахунку часових параметрів і критичних шляхів мережевої моделі проекту. Табличний метод.

- •4.2. Методи розрахунку часових параметрів і критичних шляхів мережевої моделі проекту. Матричний метод визначення часових параметрів.

- •4.3. Метод класичного варіаційного числення. Рішення варіаційної задачі із закріпленими граничними крапками.

- •4.4. Метод класичного варіаційного числення. Рівняння Ейлера-Лагранжа.

- •4.5. Постановка задачі оптимального управління. Класифікація задач оптимального управління.

- •4.6. Характеристика керованості і спостережності. Постановка завдання. Критерії керованості і спостережності.

- •6.1 Основні теоретико-множинні (об’єднання, пересічення, віднімання, декартовий добуток) операції реляційної алгебри. Коротка характеристика та приклади.

- •6.2. Основні нормальні форми. Характеристика і приклади відносин, що знаходяться в 1нф, 2нф, 3нф.

- •Id, category, product1, product2, product3

- •6.3. Основні оператори мови маніпулювання даними. Оператор вибірки даних (одно- і багатотабличні запити оператора select).

- •7.2) Модели детерминированных цифровых сигналов

- •7.3. Алгоритми оптимальної обробки при розрізненні двійкових сигналів.

- •7.4. Потенціальна завадостійкість при прийомі ам, чм та фм сигналів.

- •7.5. Багатократні та комбіновані методи модуляції.

- •7.6. Методи боротьби з помилками, що виникають в каналах зв’язку. Завадостійке кодування.

- •7.7 Основні параметри завадостійких кодів. Принципи виявлення та виправлення помилок.

- •7.8 Циклічні коди. Згортальні коди.

- •7.9 Статичні методи стиснення інформації Алгоритм арифметичного стиснення.

- •7.10 Оптимальне кодування інформації. Алгоритми формування коду Хофмана та Шенона-Фано.

- •7.11 Аналогочислові перетворення безперервного сигналу на базі теореми Котельникова в.А.

- •7.12 Пропускна спроможність двійкового каналу зв’язку з перешкодами та без перешкод.

- •8.1. Протоколи фізичного рівня.

- •8.2. Характеристика лінійних сигналів, що використовуються в комп’ютерних мережах.

- •8.4. Загальні характеристики канального рівня.

- •8.5. Протокол hdlc.

- •8.6. Методи доступу в мережу.

- •8.7. Протокол ip. Адресація в ip-мережах.

- •8.8. Протокол tcp.

- •9.1 Алгоритм принятия решения по управлению кс

- •9.2. Архітектура систем управління комп’ютерними мережами.

- •9.3. Управління потоком інформації шляхом раціонального вибору параметрів протоколу.

- •9.4. Управління обслуговуванням різнорідного трафіку: дисципліни обслуговування, їх переваги та недоліки.

- •9.5. Управління якістю обслуговування. Забезпечення якості обслуговування шляхом управління мережевими ресурсами.

- •9.6. Основні стандарти управління комп’ютерними мережами. Мережеве управління за стандартом tmn: визначення, функціональні області, інтерфейси.

- •9.7. Модель управління протоколів snmp та cmip: структура, стандартизовані елементи, переваги та недоліки.

- •10.1. Основні концепції побудови обчислювальних систем, що самоорганізуються.

- •10.2. Класифікація процесорів по архітектурі системи команд (cisc, risc).

- •10.3. Показники ефективності паралельних часових моделей алгоритмів.

- •10.4. Основні ознаки класифікації Флинна. Фрагмент класифікації Флинна.

- •10.5. Відмінності командної чарунки в vliw-процесорі від командної чарунки процесора з послідовною обробкою даних.

- •11.1Стадії та етапи створення асу тп.

- •11.2 Склад і коротка характеристика розділів технічного проекта.

- •11.3 Склад і зміст проектних рішень з технічного забезпечення.

- •11.4Склад і задачі організацій, що беруть участь у роботах зі створення асу тп.

- •11.5Перелік видів випробувань асу тп та їх короткий зміст.

- •11.6 Розрахунок вартості проектних робіт ресурсним методом.

- •11.7 Застосування елементних кошторисних норм для розрахунку вартості пусконалагоджувальних робіт.

2.5 Структуру пам’яті комп’ютера. Елементи статичної та динамічної пам’яті.

Для обеспечения высокой производительности ЭВМ необходимо, чтобы её память удовлетворяла следующим требованиям:

большая емкость (не менее сотен Мбайт);

высокое быстродействие (время доступа не более десятка нс);

энергонезависимость, т.е. обеспечение хранения программ и данных при выключении ЭВМ).

Функционально

она делится на две части: внутреннюю

и внешнюю.

Внутренняя

память, в свою очередь, делится на

оперативную (ОЗУ), постоянную (ПЗУ) память

и быструю кэш-память.

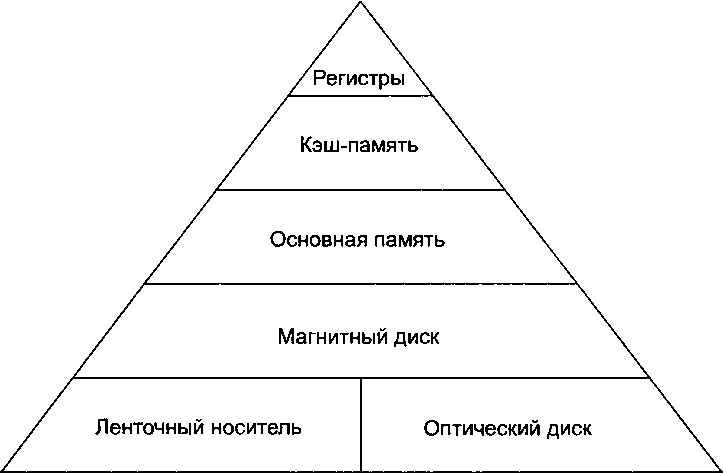

Иерархическая структура памяти является традиционным решением проблемы хранения больших объемов данных.

По мере продвижения сверху вниз по иерархии меняются три параметра. Во-первых, увеличивается время доступа. Во-вторых, растет объем памяти. В третьих, увеличивается количество битов, которое вы получаете за 1 доллар.

Память компьютера построена из двоичных запоминающих элементов — битов, объединенных в группы по 8 битов, которые называются байтами. Все байты пронумерованы. Номер байта называется его адресом.

Байты могут объединяться в ячейки, которые называются также словами. Для каждого компьютера характерна определенная длина слова — два, четыре или восемь байтов. Это не исключает использования ячеек памяти другой длины (например, полуслово, двойное слово).

Статическая оперативная память с произвольным доступом (SRAM, static random access memory) — полупроводниковая оперативная память, в которой каждый двоичный или троичный разряд хранится в схеме с положительной обратной связью, позволяющей поддерживать состояние без регенерации, необходимой в динамической памяти (DRAM). Тем не менее, сохранять данные без перезаписи SRAM может только пока есть питание, то есть SRAM остается энергозависимым типом памяти.

Типичная ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии состоит из двух перекрёстно (кольцом) включённых инверторов и ключевых транзисторов для обеспечения доступа к ячейке.

Преимущества

Быстрый доступ. SRAM — это действительно память произвольного доступа, доступ к любой ячейке памяти в любой момент занимает одно и то же время.

Простая схемотехника — SRAM не требуются сложные контроллеры.

Возможны очень низкие частоты синхронизации, вплоть до полной остановки синхроимпульсов.

Низкое энергопотребление.

Недостатки

Невысокая плотность записи (шесть-восемь элементов на бит, вместо двух у DRAM).

Вследствие чего — дороговизна килобайта памяти.

Тем не менее, высокое энергопотребление не является принципиальной особенностью SRAM, оно обусловлено высокими скоростями обмена с данным видом внутренней памяти процессора. Энергия потребляется только в момент изменения информации в ячейке SRAM.

Применение

SRAM применяется в микроконтроллерах и ПЛИС, в которых объём ОЗУ невелик (единицы килобайт), зато нужны низкое энергопотребление (за счёт отсутствия сложного контроллера динамической памяти), предсказываемое с точностью до такта[5] время работы подпрограмм и отладка прямо на устройстве.

В устройствах с большим объёмом ОЗУ рабочая память выполняется как DRAM. SRAM’ом же делают регистры и кеш-память.

DRAM (Dynamic random access memory, Динамическая память с произвольным доступом) — тип энергозависимой полупроводниковой памяти с произвольным доступом; DRAM широко используемая в качестве оперативной памяти современных компьютеров, а также в качестве постоянного хранилища информации в системах, требовательных к задержкам.

Физически DRAM состоит из ячеек, созданных в полупроводниковом материале, в каждой из которых можно хранить определённый объём данных, строку от 1 до 4 бит. Совокупность ячеек такой памяти образуют условный «прямоугольник», состоящий из определённого количества строк и столбцов. Один такой «прямоугольник» называется страницей, а совокупность страниц называется банком. Весь набор ячеек условно делится на несколько областей.

Как запоминающее устройство, DRAM представляет собой модуль памяти различных конструктивов, состоящий из электрической платы, на которой расположены микросхемы памяти и разъёма, необходимого для подключения модуля к материнской плате.

Физически DRAM-память представляет собой набор запоминающих ячеек, которые состоят из конденсаторов и транзисторов, расположенных внутри полупроводниковых микросхем памяти.

При отсутствии подачи электроэнергии к памяти этого типа происходит разряд конденсаторов, и память опустошается (обнуляется). Для поддержания необходимого напряжения на обкладках конденсаторов ячеек и сохранения их содержимого, их необходимо периодически подзаряжать, прилагая к ним напряжения через коммутирующие транзисторные ключи.

Основными характеристиками DRAM являются рабочая частота и тайминги.

При обращении к ячейке памяти контроллер памяти задаёт номер банка, номер страницы в нём, номер строки и номер столбца и на все эти запросы тратится время, помимо этого довольно большой период уходит на открытие и закрытие банка после самой операции. На каждое действие требуется время, называемое таймингом.

Основными таймингами DRAM являются: задержка между подачей номера строки и номера столбца, называемая временем полного доступа (англ. RAS to CAS delay), задержка между подачей номера столбца и получением содержимого ячейки, называемая временем рабочего цикла (англ. CAS delay), задержка между чтением последней ячейки и подачей номера новой строки (англ. RAS precharge). Тайминги измеряются в наносекундах или тактах, и чем меньше величина этих таймингов, тем быстрее работает оперативная память.