- •Features

- •Pin Configurations

- •Overview

- •Block Diagram

- •Disclaimer

- •Pin Descriptions

- •Port A (PA7..PA0)

- •Port B (PB7..PB0)

- •Port C (PC7..PC0)

- •Port D (PD7..PD0)

- •Port E(PE2..PE0)

- •RESET

- •XTAL1

- •XTAL2

- •AVR CPU Core

- •Introduction

- •Architectural Overview

- •Status Register

- •Stack Pointer

- •Interrupt Response Time

- •In-System Reprogrammable Flash Program memory

- •SRAM Data Memory

- •Data Memory Access Times

- •EEPROM Data Memory

- •EEPROM Read/Write Access

- •I/O Memory

- •Overview

- •Address Latch Requirements

- •Pull-up and Bus Keeper

- •Timing

- •Using all Locations of External Memory Smaller than 64 KB

- •Using all 64KB Locations of External Memory

- •Clock Systems and their Distribution

- •Clock Sources

- •Default Clock Source

- •Crystal Oscillator

- •External RC Oscillator

- •External Clock

- •Idle Mode

- •Power-down Mode

- •Standby Mode

- •Analog Comparator

- •Brown-out Detector

- •Internal Voltage Reference

- •Watchdog Timer

- •Port Pins

- •Resetting the AVR

- •Reset Sources

- •Power-on Reset

- •External Reset

- •Brown-out Detection

- •Watchdog Reset

- •Watchdog Timer

- •Timed Sequences for Changing the Configuration of the Watchdog Timer

- •Safety Level 0

- •Safety Level 1

- •Safety Level 2

- •Interrupts

- •Moving Interrupts between Application and Boot Space

- •I/O Ports

- •Introduction

- •Configuring the Pin

- •Reading the Pin Value

- •Unconnected pins

- •Alternate Port Functions

- •Alternate Functions of Port A

- •Alternate Functions Of Port B

- •Alternate Functions of Port C

- •Alternate Functions of Port D

- •Alternate Functions of Port E

- •Register Description for I/O Ports

- •External Interrupts

- •8-bit Timer/Counter0 with PWM

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Output Compare Unit

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •Internal Clock Source

- •Prescaler Reset

- •External Clock Source

- •16-bit Timer/Counter1

- •Overview

- •Registers

- •Definitions

- •Compatibility

- •Counter Unit

- •Input Capture Unit

- •Input Capture Trigger Source

- •Noise Canceler

- •Using the Input Capture Unit

- •Output Compare Units

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •Slave Mode

- •Master Mode

- •Data Modes

- •USART

- •Single USART

- •Clock Generation

- •External Clock

- •Synchronous Clock Operation

- •Frame Formats

- •Parity Bit Calculation

- •USART Initialization

- •Sending Frames with 5 to 8 Data Bits

- •Sending Frames with 9 Data Bits

- •Parity Generator

- •Disabling the Transmitter

- •Receiving Frames with 5 to 8 Data Bits

- •Receiving Frames with 9 Data Bits

- •Receiver Error Flags

- •Parity Checker

- •Disabling the Receiver

- •Flushing the Receive Buffer

- •Asynchronous Data Recovery

- •Using MPCM

- •Write Access

- •Read Access

- •Analog Comparator

- •Features

- •Application Section

- •Boot Loader Lock bits

- •Performing a Page Write

- •Using the SPM Interrupt

- •Setting the Boot Loader Lock bits by SPM

- •Reading the Fuse and Lock bits from Software

- •Preventing Flash Corruption

- •Simple Assembly Code Example for a Boot Loader

- •Program and Data Memory Lock bits

- •Fuse bits

- •Latching of Fuses

- •Signature Bytes

- •Calibration Byte

- •Calibration Byte

- •Signal Names

- •Parallel Programming

- •Enter Programming Mode

- •Chip Erase

- •Programming the Flash

- •Programming the EEPROM

- •Reading the Flash

- •Reading the EEPROM

- •Programming the Lock bits

- •Reading the Signature Bytes

- •Reading the Calibration Byte

- •Serial Downloading

- •Data Polling Flash

- •Data Polling EEPROM

- •Electrical Characteristics

- •Absolute Maximum Ratings*

- •External Clock Drive Waveforms

- •External Clock Drive

- •External Data Memory Timing

- •Active Supply Current

- •Idle Supply Current

- •Standby Supply Current

- •Pin Pull-up

- •Pin Driver Strength

- •Internal Oscillator Speed

- •Register Summary

- •Instruction Set Summary

- •Ordering Information

- •Packaging Information

- •Errata

- •ATmega8515(L) Rev. B

- •Changes from Rev. 2512F-12/03 to Rev. 2512G-03/05

- •Changes from Rev. 2512F-12/03 to Rev. 2512E-09/03

- •Changes from Rev. 2512D-02/03 to Rev. 2512E-09/03

- •Changes from Rev. 2512C-10/02 to Rev. 2512D-02/03

- •Changes from Rev. 2512B-09/02 to Rev. 2512C-10/02

- •Changes from Rev. 2512A-04/02 to Rev. 2512B-09/02

- •Table of Contents

Special Function IO Register –

SFIOR

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit |

7 |

6 |

|

5 |

4 |

3 |

2 |

1 |

0 |

|

||

|

|

|

|

|

|

|

|

|

|

|

||

|

– |

XMBK |

|

XMM2 |

XMM1 |

XMM0 |

PUD |

– |

PSR10 |

SFIOR |

||

Read/Write |

R/W |

R/W |

|

R/W |

R/W |

R/W |

R/W |

R/W |

R/W |

|

||

Initial Value |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

||

• Bit 6 – XMBK: External Memory Bus Keeper Enable

Writing XMBK to one enables the Bus Keeper on the AD7:0 lines. When the Bus Keeper is enabled, AD7:0 will keep the last driven value on the lines even if the XMEM interface has tri-stated the lines. Writing XMBK to zero disables the Bus Keeper. XMBK is not qualified with SRE, so even if the XMEM interface is disabled, the Bus Keepers are still activated as long as XMBK is one.

• Bit 5..3 – XMM2, XMM1, XMM0: External Memory High Mask

When the External Memory is enabled, all Port C pins are used for the high address byte by default. If the full 64,928 bytes address space is not required to access the External Memory, some, or all, Port C pins can be released for normal Port Pin function as described in Table 4. As described in “Using all 64KB Locations of External Memory” on page 32, it is possible to use the XMMn bits to access all 64KB locations of the External Memory.

Table 4. Port C Pins Released as Normal Port Pins when the External Memory is Enabled

XMM2 |

XMM1 |

XMM0 |

# Bits for External Memory Address |

Released Port Pins |

|

|

|

|

|

0 |

0 |

0 |

8 (Full 64,928 Bytes Space) |

None |

|

|

|

|

|

0 |

0 |

1 |

7 |

PC7 |

|

|

|

|

|

0 |

1 |

0 |

6 |

PC7 - PC6 |

|

|

|

|

|

0 |

1 |

1 |

5 |

PC7 - PC5 |

|

|

|

|

|

1 |

0 |

0 |

4 |

PC7 - PC4 |

|

|

|

|

|

1 |

0 |

1 |

3 |

PC7 - PC3 |

|

|

|

|

|

1 |

1 |

0 |

2 |

PC7 - PC2 |

|

|

|

|

|

1 |

1 |

1 |

No Address High bits |

Full Port C |

|

|

|

|

|

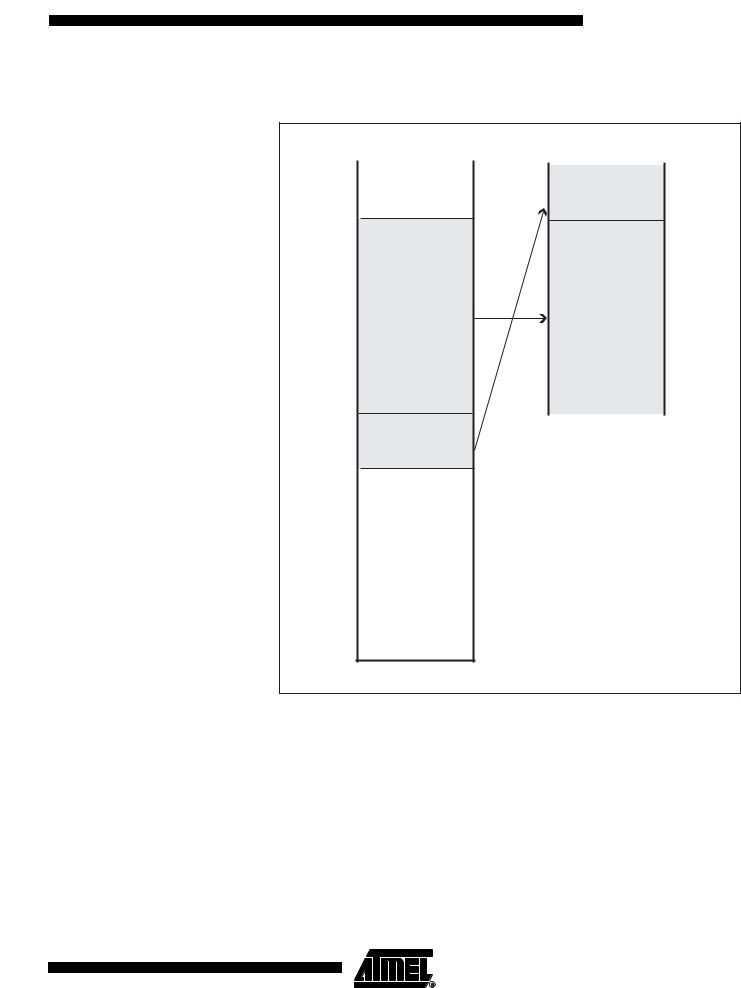

Using all Locations of External Memory Smaller than 64 KB

Since the external memory is mapped after the internal memory as shown in Figure 11, the external memory is not addressed when addressing the first 608 bytes of data space. It may appear that the first 608 bytes of the external memory are inaccessible (external memory addresses 0x0000 to 0x025F). However, when connecting an external memory smaller than 64 KB, for example 32 KB, these locations are easily accessed simply by addressing from address 0x8000 to 0x825F. Since the External Memory Address bit A15 is not connected to the external memory, addresses 0x8000 to 0x825F will appear as addresses 0x0000 to 0x025F for the external memory. Addressing above address 0x825F is not recommended, since this will address an external memory location that is already accessed by another (lower) address. To the Application software, the external 32 KB memory will appear as one linear 32 KB address space from 0x0260 to 0x825F. This is illustrated in Figure 17.

30 ATmega8515(L)

2512G–AVR–03/05

ATmega8515(L)

Figure 17. Address Map with 32 KB External Memory

Memory Configuration

|

|

AVR Memory Map |

|

|

External 32K SRAM |

|

0x0000 |

|

|

|

|

|

0x0000 |

|

Internal Memory |

|

|

|

||

|

|

|

|

|||

0x025F |

|

|

|

0x025F |

||

|

|

|

|

|||

0x0260 |

|

|

|

|

0x0260 |

|

0x7FFF |

External |

||

|

|

0x7FFF |

|

0x8000 |

Memory |

||

0x825F |

|

|

|

0x8260 |

|

|

|

(Unused)

0xFFFF

31

2512G–AVR–03/05

Using all 64KB Locations of External Memory

Since the External Memory is mapped after the Internal Memory as shown in Figure 11, only 64,928 bytes of External Memory is available by default (address space 0x0000 to 0x025F is reserved for Internal Memory). However, it is possible to take advantage of the entire External Memory by masking the higher address bits to zero. This can be done by using the XMMn bits and control by software the most significant bits of the address. By setting Port C to output 0x00, and releasing the most significant bits for normal Port Pin operation, the Memory Interface will address 0x0000 - 0x1FFF. See code example below.

Assembly Code Example(1)

;OFFSET is defined to 0x2000 to ensure

;external memory access

;Configure Port C (address high byte) to

;output 0x00 when the pins are released

;for normal Port Pin operation

ldi r16, 0xFF out DDRC, r16 ldi r16, 0x00 out PORTC, r16 ; release PC7:5

ldi r16, (1<<XMM1)|(1<<XMM0) out SFIOR, r16

;write 0xAA to address 0x0001 of external

;memory

ldi r16, 0xaa

sts 0x0001+OFFSET, r16

;re-enable PC7:5 for external memory ldi r16, (0<<XMM1)|(0<<XMM0)

out SFIOR, r16

;store 0x55 to address (OFFSET + 1) of

;external memory

ldi r16, 0x55

sts 0x0001+OFFSET, r16

C Code Example(1)

#define OFFSET 0x2000

void XRAM_example(void)

{

unsigned char *p = (unsigned char *) (OFFSET + 1);

DDRC = 0xFF;

PORTC = 0x00;

SFIOR = (1<<XMM1) | (1<<XMM0);

*p = 0xaa;

SFIOR = 0x00;

*p = 0x55;

}

Note: 1. See “About Code Examples” on page 6.

Care must be exercised using this option as most of the memory is masked away.

32 ATmega8515(L)

2512G–AVR–03/05