- •Features

- •Pin Configurations

- •Overview

- •Block Diagram

- •Disclaimer

- •Pin Descriptions

- •Port A (PA7..PA0)

- •Port B (PB7..PB0)

- •Port C (PC7..PC0)

- •Port D (PD7..PD0)

- •Port E(PE2..PE0)

- •RESET

- •XTAL1

- •XTAL2

- •AVR CPU Core

- •Introduction

- •Architectural Overview

- •Status Register

- •Stack Pointer

- •Interrupt Response Time

- •In-System Reprogrammable Flash Program memory

- •SRAM Data Memory

- •Data Memory Access Times

- •EEPROM Data Memory

- •EEPROM Read/Write Access

- •I/O Memory

- •Overview

- •Address Latch Requirements

- •Pull-up and Bus Keeper

- •Timing

- •Using all Locations of External Memory Smaller than 64 KB

- •Using all 64KB Locations of External Memory

- •Clock Systems and their Distribution

- •Clock Sources

- •Default Clock Source

- •Crystal Oscillator

- •External RC Oscillator

- •External Clock

- •Idle Mode

- •Power-down Mode

- •Standby Mode

- •Analog Comparator

- •Brown-out Detector

- •Internal Voltage Reference

- •Watchdog Timer

- •Port Pins

- •Resetting the AVR

- •Reset Sources

- •Power-on Reset

- •External Reset

- •Brown-out Detection

- •Watchdog Reset

- •Watchdog Timer

- •Timed Sequences for Changing the Configuration of the Watchdog Timer

- •Safety Level 0

- •Safety Level 1

- •Safety Level 2

- •Interrupts

- •Moving Interrupts between Application and Boot Space

- •I/O Ports

- •Introduction

- •Configuring the Pin

- •Reading the Pin Value

- •Unconnected pins

- •Alternate Port Functions

- •Alternate Functions of Port A

- •Alternate Functions Of Port B

- •Alternate Functions of Port C

- •Alternate Functions of Port D

- •Alternate Functions of Port E

- •Register Description for I/O Ports

- •External Interrupts

- •8-bit Timer/Counter0 with PWM

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Output Compare Unit

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •Internal Clock Source

- •Prescaler Reset

- •External Clock Source

- •16-bit Timer/Counter1

- •Overview

- •Registers

- •Definitions

- •Compatibility

- •Counter Unit

- •Input Capture Unit

- •Input Capture Trigger Source

- •Noise Canceler

- •Using the Input Capture Unit

- •Output Compare Units

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •Slave Mode

- •Master Mode

- •Data Modes

- •USART

- •Single USART

- •Clock Generation

- •External Clock

- •Synchronous Clock Operation

- •Frame Formats

- •Parity Bit Calculation

- •USART Initialization

- •Sending Frames with 5 to 8 Data Bits

- •Sending Frames with 9 Data Bits

- •Parity Generator

- •Disabling the Transmitter

- •Receiving Frames with 5 to 8 Data Bits

- •Receiving Frames with 9 Data Bits

- •Receiver Error Flags

- •Parity Checker

- •Disabling the Receiver

- •Flushing the Receive Buffer

- •Asynchronous Data Recovery

- •Using MPCM

- •Write Access

- •Read Access

- •Analog Comparator

- •Features

- •Application Section

- •Boot Loader Lock bits

- •Performing a Page Write

- •Using the SPM Interrupt

- •Setting the Boot Loader Lock bits by SPM

- •Reading the Fuse and Lock bits from Software

- •Preventing Flash Corruption

- •Simple Assembly Code Example for a Boot Loader

- •Program and Data Memory Lock bits

- •Fuse bits

- •Latching of Fuses

- •Signature Bytes

- •Calibration Byte

- •Calibration Byte

- •Signal Names

- •Parallel Programming

- •Enter Programming Mode

- •Chip Erase

- •Programming the Flash

- •Programming the EEPROM

- •Reading the Flash

- •Reading the EEPROM

- •Programming the Lock bits

- •Reading the Signature Bytes

- •Reading the Calibration Byte

- •Serial Downloading

- •Data Polling Flash

- •Data Polling EEPROM

- •Electrical Characteristics

- •Absolute Maximum Ratings*

- •External Clock Drive Waveforms

- •External Clock Drive

- •External Data Memory Timing

- •Active Supply Current

- •Idle Supply Current

- •Standby Supply Current

- •Pin Pull-up

- •Pin Driver Strength

- •Internal Oscillator Speed

- •Register Summary

- •Instruction Set Summary

- •Ordering Information

- •Packaging Information

- •Errata

- •ATmega8515(L) Rev. B

- •Changes from Rev. 2512F-12/03 to Rev. 2512G-03/05

- •Changes from Rev. 2512F-12/03 to Rev. 2512E-09/03

- •Changes from Rev. 2512D-02/03 to Rev. 2512E-09/03

- •Changes from Rev. 2512C-10/02 to Rev. 2512D-02/03

- •Changes from Rev. 2512B-09/02 to Rev. 2512C-10/02

- •Changes from Rev. 2512A-04/02 to Rev. 2512B-09/02

- •Table of Contents

|

|

|

|

|

|

|

ATmega8515(L) |

|

|

|

|

|

|

|

|

|

Electrical Characteristics |

|

|||||

|

|

|

|||||

|

|

|

|||||

|

Absolute Maximum Ratings* |

|

|

||||

|

|

*NOTICE: Stresses beyond those listed under “Absolute |

|||||

|

Operating Temperature.................................. -55°C to +125°C |

||||||

|

|

|

|

|

|

Maximum Ratings” may cause permanent dam- |

|

|

Storage Temperature ..................................... -65°C to +150°C |

age to the device. This is a stress rating only and |

|||||

|

|

|

|

|

|

functional operation of the device at these or |

|

|

Voltage on any Pin except |

RESET |

|

other conditions beyond those indicated in the |

|||

|

with respect to Ground ................................-0.5V to VCC+0.5V |

operational sections of this specification is not |

|||||

|

Voltage on |

|

with respect to Ground......-0.5V to +13.0V |

implied. Exposure to absolute maximum rating |

|||

|

RESET |

conditions for extended periods may affect |

|||||

|

Maximum Operating Voltage ............................................ 6.0V |

device reliability. |

|||||

|

|

|

|||||

|

DC Current per I/O Pin ............................................... 40.0 mA |

|

|

||||

|

DC Current VCC and GND Pins................................ 200.0 mA |

|

|

||||

|

|

|

|

|

|

|

|

DC Characteristics

TA = -40°C to 85°C, VCC = 2.7V to 5.5V (Unless Otherwise Noted)

Symbol |

|

Parameter |

Condition |

|

Min |

|

Typ |

Max |

Units |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

Input Low Voltage except |

|

|

|

|

|

|

|

(1) |

|

|||

VIL |

|

XTAL1 and |

|

pins |

VCC=2.7V - 5.5V |

-0.5 |

|

|

0.2 VCC |

V |

||||

RESET |

|

|

||||||||||||

VIH |

|

Input High Voltage except |

VCC=2.7V - 5.5V |

0.6 VCC |

(2) |

|

VCC + 0.5 |

V |

||||||

|

XTAL1 and |

RESET |

pins |

|

|

|||||||||

VIL1 |

|

Input Low Voltage |

VCC=2.7V - 5.5V |

-0.5 |

|

|

(1) |

V |

||||||

|

XTAL1 pin |

|

|

0.1 VCC |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

VIH1 |

|

Input High Voltage |

VCC=2.7V - 5.5V |

0.8 VCC |

(2) |

|

VCC + 0.5 |

V |

||||||

|

|

|

|

|

|

|||||||||

|

XTAL1 pin |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

VIL2 |

|

Input Low Voltage |

VCC=2.7V - 5.5V |

-0.5 |

|

|

0.2 VCC |

V |

||||||

|

|

|

|

|

|

|

||||||||

RESET pin |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

VIH2 |

|

Input High Voltage |

VCC=2.7V - 5.5V |

0.9 VCC |

(2) |

|

VCC + 0.5 |

V |

||||||

|

|

|

|

|

|

|||||||||

|

RESET pin |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

Output Low Voltage(3) |

I |

OL |

= 20 mA, V |

= 5V |

|

|

|

0.7 |

V |

|||

VOL |

|

|

|

|

|

|

|

CC |

|

|

|

|

|

|

|

(Ports A,B,C,D,E) |

IOL = 10 mA, VCC = 3V |

|

|

|

0.5 |

V |

|||||||

|

|

|

|

|

||||||||||

VOH |

|

Output High Voltage(4) |

IOH = -20 mA, VCC = 5V |

4.2 |

|

|

|

V |

||||||

|

(Ports A,B,C,D,E) |

IOH = -10 mA, VCC = 3V |

2.2 |

|

|

|

V |

|||||||

|

|

|

|

|

||||||||||

IIL |

|

Input Leakage |

VCC = 5.5V, pin low |

|

|

|

1 |

µA |

||||||

|

Current I/O Pin |

(absolute value) |

|

|

|

|||||||||

IIH |

|

Input Leakage |

VCC = 5.5V, pin high |

|

|

|

1 |

µA |

||||||

|

Current I/O Pin |

(absolute value) |

|

|

|

|||||||||

RRST |

|

Reset Pull-up Resistor |

|

|

|

|

30 |

|

|

60 |

kΩ |

|||

Rpu |

|

I/O Pin Pull-up Resistor |

|

|

|

|

20 |

|

|

50 |

kΩ |

|||

195

2512G–AVR–03/05

DC Characteristics (Continued)

TA = -40°C to 85°C, VCC = 2.7V to 5.5V (Unless Otherwise Noted)

Symbol |

Parameter |

Condition |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

|

|

Active 4 MHz, VCC = 3V |

|

|

4 |

mA |

|

|

(ATmega8515L) |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Active 8 MHz, VCC = 5V |

|

|

12 |

mA |

|

|

(ATmega8515) |

|

|

||

|

Power Supply Current |

|

|

|

|

|

|

|

|

|

|

|

|

ICC |

Idle 4 MHz, VCC = 3V |

|

|

1.5 |

mA |

|

|

|

|

||||

|

(ATmega8515L) |

|

|

|||

|

|

|

|

|

||

|

|

Idle 8 MHz, VCC = 5V |

|

|

5.5 |

mA |

|

|

(ATmega8515) |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power-down mode(5) |

WDT enabled, VCC = 3V |

|

|

< 13 |

µA |

|

WDT disabled, VCC = 3V |

|

|

< 2 |

µA |

|

|

|

|

|

|||

VACIO |

Analog Comparator |

VCC = 5V |

|

|

40 |

mV |

Input Offset Voltage |

Vin = VCC/2 |

|

|

|||

|

|

|

|

|

||

IACLK |

Analog Comparator |

VCC = 5V |

-50 |

|

50 |

nA |

Input Leakage Current |

Vin = VCC/2 |

|

||||

|

|

|

|

|

||

tACPD |

Analog Comparator |

VCC = 2.7V |

|

750 |

|

ns |

Propagation Delay |

VCC = 4.0V |

|

500 |

|

||

|

|

|

|

Notes: 1. “Max” means the highest value where the pin is guaranteed to be read as low.

2.“Min” means the lowest value where the pin is guaranteed to be read as high.

3.Although each I/O port can sink more than the test conditions (20 mA at VCC = 5V, 10 mA at VCC = 3V) under steady state conditions (non-transient), the following must be observed:

1] The sum of all IOL, for all ports, should not exceed 200 mA.

2] The sum of all IOL, for ports B0 - B7, D0 - D7, and XTAL2, should not exceed 100 mA. 3] The sum of all IOL, for ports A0 - A7, E0 - E2, and C0 - C7 should not exceed 100 mA.

4.Although each I/O port can source more than the test conditions (20 mA at VCC = 5V, 10 mA at VCC = 3V) under steady state conditions (non-transient),the following must be observed:

1] The sum of all IOH,for all ports, should not exceed 200 mA.

2] The sum of all IOH,for ports B0 - B7, D0 - D7, and XTAL2,should not exceed 100 mA. 3] The sum of all IOH,for ports A0 - A7, E0 - E2, and C0 - C7 should not exceed 100 mA.

5.Minimum VCC for Power-down is 2.5V.

196 ATmega8515(L)

2512G–AVR–03/05

ATmega8515(L)

ATmega8515(L)

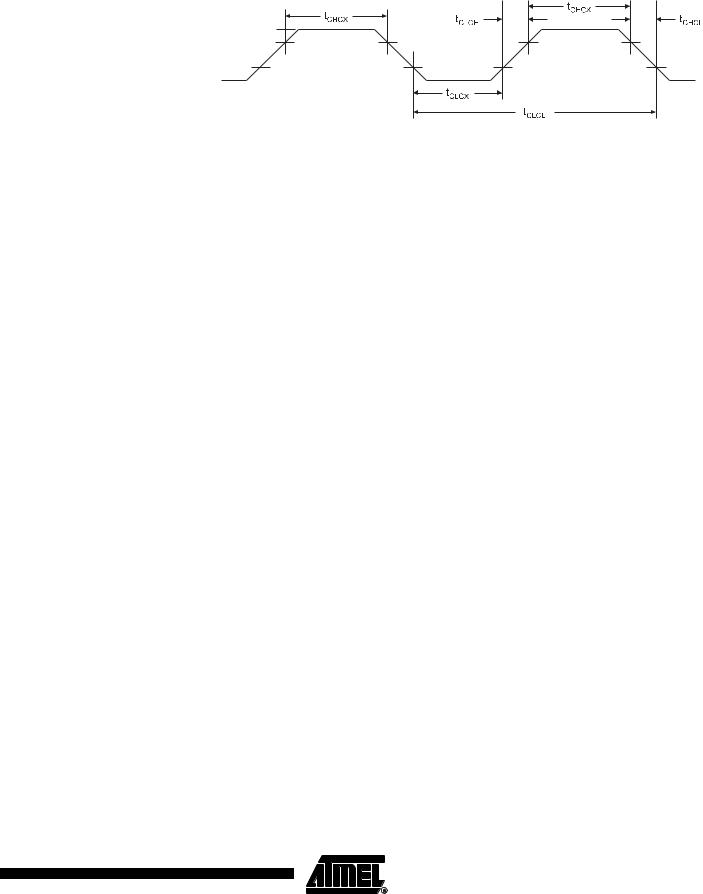

External Clock Drive

Waveforms

External Clock Drive

Figure 86. External Clock Drive Waveforms

VIH1

VIL1

Table 95. External Clock Drive

|

|

|

VCC = 2.7 - 5.5V |

VCC = 4.5 - 5.5V |

|

|

||||

Symbol |

Parameter |

Min |

|

Max |

Min |

Max |

|

Units |

||

|

|

|

|

|

|

|

|

|

|

|

1/tCLCL |

Oscillator Frequency |

0 |

|

8 |

0 |

|

16 |

|

MHz |

|

tCLCL |

Clock Period |

125 |

|

|

62.5 |

|

|

ns |

||

tCHCX |

High Time |

50 |

|

|

25 |

|

|

ns |

||

tCLCX |

Low Time |

50 |

|

|

25 |

|

|

ns |

||

tCLCH |

Rise Time |

|

|

1.6 |

|

|

0.5 |

|

µs |

|

tCHCL |

Fall Time |

|

|

1.6 |

|

|

0.5 |

|

µs |

|

∆tCLCL |

Change in period from |

|

|

|

|

|

|

|

|

|

one clock cycle to the |

|

|

2 |

|

|

2 |

|

% |

||

|

next(1) |

|

|

|

|

|

|

|

|

|

Note: 1. |

Refer to “External Clock” on page 39 for details. |

|

|

|

|

|

||||

Table 96. External RC Oscillator, Typical Frequencies (VCC = 5V) |

|

|

|

|||||||

|

R [kΩ](1) |

|

|

C [pF] |

|

|

f(2) |

|

||

|

100 |

|

|

47 |

|

|

87 kHz |

|

||

|

|

|

|

|

|

|

|

|

||

|

33 |

|

|

22 |

|

|

650 kHz |

|

||

|

|

|

|

|

|

|

|

|

||

|

10 |

|

|

22 |

|

|

2.0 MHz |

|

||

|

|

|

|

|

|

|

|

|

|

|

Notes: 1. R should be in the range 3 kΩ - 100 kΩ, and C should be at least 20 pF. The C values given in the table includes pin capacitance. This will vary with package type.

2. The frequency will vary with package type and board layout.

197

2512G–AVR–03/05

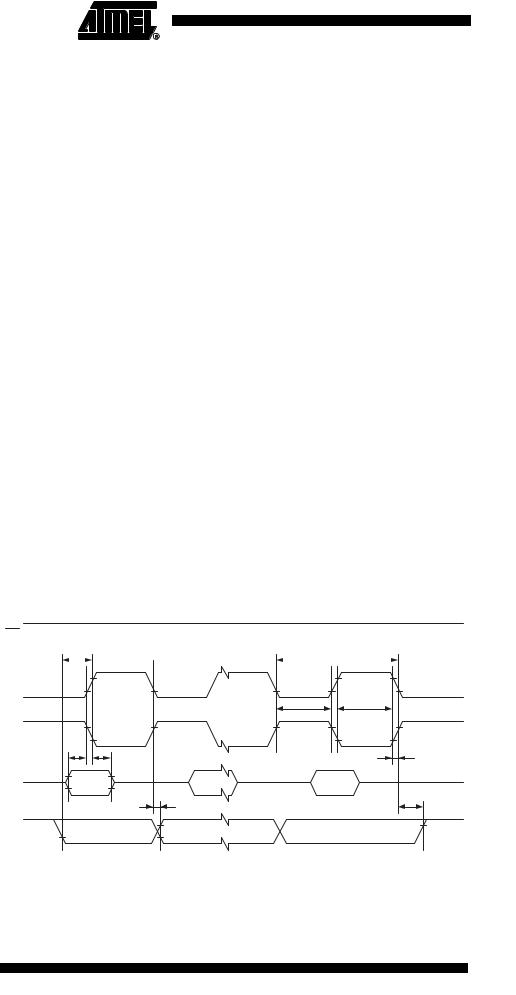

SPI Timing

Characteristics

See Figure 87 and Figure 88 for details.

Table 97. SPI Timing Parameters

|

|

|

|

Description |

Mode |

Min |

Typ |

Max |

|

|||

|

|

|

|

|

|

|

|

|

|

|||

1 |

|

|

|

SCK period |

Master |

|

See Table 58 |

|

|

|||

|

|

|

|

|

|

|

|

|

||||

2 |

|

|

SCK high/low |

Master |

|

50% duty cycle |

|

|

||||

|

|

|

|

|

|

|

|

|

||||

3 |

|

|

Rise/Fall time |

Master |

|

3.6 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||

4 |

|

|

|

|

Setup |

Master |

|

10 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

5 |

|

|

|

|

Hold |

Master |

|

10 |

|

|

||

|

|

|

|

|

|

|

|

|

ns |

|||

6 |

|

|

|

Out to SCK |

Master |

|

0.5 • tSCK |

|

||||

7 |

|

|

|

SCK to out |

Master |

|

10 |

|

|

|||

|

|

|

|

|

|

|

|

|||||

8 |

|

SCK to out high |

Master |

|

10 |

|

|

|||||

|

|

|

|

|

|

|

|

|

||||

9 |

|

|

SS low to out |

Slave |

|

15 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|||

10 |

|

|

|

SCK period |

Slave |

4 • tck |

|

|

|

|||

11 |

|

SCK high/low(1) |

Slave |

2 • t |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

ck |

|

|

|

12 |

|

|

Rise/Fall time |

Slave |

|

|

1.6 |

µs |

||||

|

|

|

|

|

|

|

|

|

|

|

||

13 |

|

|

|

|

Setup |

Slave |

10 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

14 |

|

|

|

|

Hold |

Slave |

tck |

|

|

|

||

15 |

|

|

|

SCK to out |

Slave |

|

15 |

|

ns |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

|

SCK to |

|

high |

Slave |

20 |

|

|

||||

|

SS |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|||

17 |

|

|

|

high to tri-state |

Slave |

|

10 |

|

|

|||

|

SS |

|

|

|

||||||||

18 |

|

|

|

|

low to SCK |

Salve |

2 • tck |

|

|

|

||

|

|

SS |

|

|

|

|||||||

Note: |

1. In SPI Programming mode the minimum SCK high/low period is: |

|

|

|||||||||

-2 tCLCL for fCK < 12 MHz

-3 tCLCL for fCK >12 MHz

Figure 87. SPI Interface Timing Requirements (Master Mode)

SS

6 |

|

1 |

SCK |

|

|

|

|

(CPOL = 0) |

|

|

|

|

|

|

2 |

2 |

|

SCK |

|

|

|

|

(CPOL = 1) |

|

|

|

|

4 |

5 |

|

3 |

|

MISO |

MSB |

... |

LSB |

|

(Data Input) |

||||

|

|

|

||

|

|

7 |

8 |

|

MOSI |

MSB |

... |

LSB |

|

(Data Output) |

||||

|

|

|

198 ATmega8515(L)

2512G–AVR–03/05

ATmega8515(L)

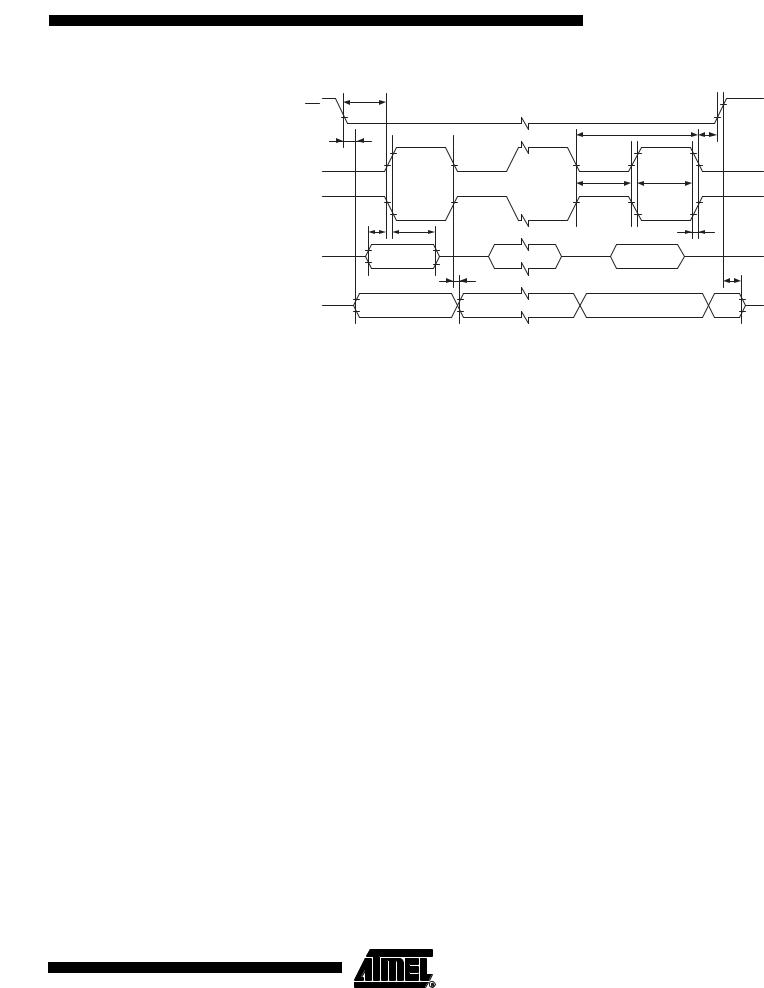

Figure 88. SPI Interface Timing Requirements (Slave Mode)

18 |

|

|

|

|

|

SS |

|

|

|

|

|

9 |

|

|

10 |

16 |

|

|

|

|

|

||

SCK |

|

|

|

|

|

(CPOL = 0) |

|

|

|

|

|

|

|

11 |

11 |

|

|

SCK |

|

|

|

|

|

(CPOL = 1) |

|

|

|

|

|

13 |

14 |

|

|

12 |

|

MOSI |

MSB |

... |

LSB |

|

|

(Data Input) |

|

||||

|

|

|

|

||

|

|

15 |

|

17 |

|

MISO |

MSB |

... |

LSB |

X |

|

(Data Output) |

|||||

|

|

|

|

199

2512G–AVR–03/05