- •Полупроводниковые приборы. Классификация. Область применения.

- •Полупроводниковые диоды. Классификация. Область применения.

- •Полупроводниковые транзисторы. Классификация. Область применения.

- •Полупроводниковые резисторы. Классификация. Область применения.

- •Фотоэлектрические приборы. Классификация. Область применения.

- •Аналоговые усилители. Классификация. Основные характеристики и параметры.

- •Избирательные усилители. Усилители постоянного тока. Усилители мощности. Область применения.

- •Стабилизаторы напряжения. Классификация. Параметры. Область применения.

- •Логические операции. Схемная реализация.

- •Цифровые устройства. Классификация. Комбинационные цу. Дешифраторы. Шифраторы, мультиплексоры, демультиплексоры.

- •Комбинационные сумматоры.

- •Триггера. Классификация. Область применения.

- •Регистры и счетчики. Классификация. Схемы. Область применения.

- •Цифро-аналоговые преобразователи. Назначение. Принцип работы. Матрица r-2r. Область применения.

- •Аналого-цифровые преобразователи. Классификация. Область применения. Параллельные ацп. Ацп поразрядного взвешивания.

- •Интегрирующие ацп. Ацп двойного интегрирования

- •Таймеры. Классификация. Область применения.

- •Источники вторичного напряжения. Структурные схемы. Выпрямители и фильтры.

- •Транзисторный усилительный каскад с общим эммитером

- •Дискретные цифровые сар: математическое описание, z передаточные функции.

- •Анализ дискретных сар

- •23. Логарифмические частотные характеристики сар.

- •24. Переходные функции и переходные характеристики сар. Реакция сар на произвольный входной сигнал

- •25.Типовые звенья сар и их частотные и временные характеристики Апериодическое звено

- •Интегрирующее звено

- •26. Устойчивость линейных сар: определение, теоремы Ляпунова, алгебраический критерий устойчивости Гурвица.

- •27. Частотные критерии устойчивости линейных сар

- •28. Анализ качества линейных сар.

- •29. Синтез корректирующих устройств линейных сар.

- •30. Анализ нелинейных сар.

- •31. Показатели качества эс

- •33. Себестоимость и уровень качества эс

- •34. Корреляционная связь показателей эc Диаграмма разброса (поле корреляции)

- •35. Метод расслаивания чм.

- •36. Метод «авс-анализ»

- •Складские запасы изделий

- •37. Виды статистического контроля эс

- •38. Количественные показатели надежности эс

- •39. Последовательная модель надежности

- •40. Параллельная модель надежности эс

- •41. Основные этапы автоматизации: их характеристики и особенности.

- •42. Назначение, классификация и области применения роботов

- •43. Манипуляционные роботы: типы, характеристики, применение

- •44. Структура механизмов манипуляц-х роботов и характеристики их геом. Свойств

- •45. Приводы манипуляторов и роботов: классификация, особенности применения

- •46. Конструкции схватов промышленных роботов(пр), особенности применения

- •47. Проектирование архитектуры интегрированной компьютерной системы управления (иксу)

- •48. Описание технологического процесса как объекта автоматизированного управления

- •49. Описание производственного процесса как объекта автоматизированного управления: реализации арм различных уровней

- •50. Выбор датчиков тп:типы измерительных устройств, подключение

- •51. Теорема Котельникова (теорема отсчетов). Квазидетерминированные сигналы.

- •52. Преобразование измерительных сигналов. Виды модуляций

- •53. Цифровые частотомеры

- •54. Цифровые фазометры

- •55. Цифровые вольтметры (цв) временного преобразования

- •56. Микропроцессорные цифровые измерительные приборы.

- •57. Резистивные датчики (реостатные, тензорезисторы)

- •58. Электромагнитные датчики (индуктивные, трансформаторные, магнитоупруние).

- •59. Пьезоэлектрические датчики

- •60. Тепловые датчики (термопары, термометры сопротивления).

- •61. Организация и этапы разработки конструкторских документов.

- •62. Виды кд.

- •63. Стандартизация и бнк.

- •64. Виды и типы схем, обозначения по ескд.

- •65. Методы компоновки конструкции эвс.

- •66. Климатические зоны и категории исполнения.

- •67. Способы защиты эвс от влаги.

- •Примеры конструкций средств защиты

- •68. Защита эвс от механических воздействий.

- •Рекомендации по защите рэа от вибрационных воздействий

- •69. Способы обеспечения теплового режима эвс.

- •70. Электромагнитные воздействия. Виды экранов.

- •Экран из ферромагнитного материала с большой магнитной проницаемостью (метод шунтирования экраном).

- •71. Виды линий связи.

- •72. Особенности конструирования бортовых эвс.

- •73. Особенности конструкций персональных эвм.

- •74. Унификация. Разновидности стандартизации.

- •Разновидности стандартизации

- •75. Требования к трассировке пп

- •76. Электромонтажные провода. Припои и флюсы.

- •77. Волоконно-оптические линии связи (волс). Примеры использования.

- •78. Эргономические требования к пультам и органам управления и сигнализации

- •79. Эргономика конструирования лицевой панели прибора.

- •80. Защита эс от воздействия радиации.

- •81. Производственный и технологический процесс и их составляющие

- •82. Исходные данные для разработки технологических процессов. Основные этапы разработки единичного технологического процесса.

- •83. Требования к оформлению технологической документации. Примеры записи технологических операций.

- •84. Основные методы изготовления печатных плат и их особенности

- •85. Конструктивно-технологические разновидности радиоэлектронных узлов и их сопоставительный анализ.

- •86. Основные технологические операции при изготовлении радиоэлектронных узлов с монтажом на поверхность

- •87. Нанесение паяльной пасты и клея и используемое при этом оборудование

- •88. Принципы организации работы сборочных автоматов

- •89. Особенности выполнения пайки при изготовлении электронных модулей ( пайка оплавлением, волной припоя, селективная пайка).

- •90. Особенности выполнения ремонтных работ: демонтаж и монтаж компонентов.

- •91. Материалы, используемые в технологии монтажа на поверхность.

- •92 Виды соединительных операций при сборке.

- •94. Соединение пайкой: разновидности, области применения, примеры выполнения паяных соединений.

- •95. Разработка схемы сборки изделий.

- •96. Нормирование затрат времени при проектировании технологических процессов (штучное и подготовительно-заключительное время, определение такта и ритма выпуска изделий).

- •97. Изготовление деталей эс методом литья

- •98. Разделительные и формообразующие операции холодной штамповки

- •99. Общая характеристика методов формообразования материалов и деталей при производстве эс

- •100. Изготовление электронных модулей по технологии внутреннего монтажа.

- •101. Приведите структуру контроллера (микроЭвм) с раздельными шинами адрес/данные и следующим составом:

- •102. Укажите место на структурной схеме эвм различных интерфейсов. Как объединять эвм в систему? Какие условия следует выполнить при передаче данных? Обоснуйте.

- •103.Расставьте по убыванию значимости параметры эвм по критерию производительности. Охарактеризуйте эти параметры.

- •105. Сопоставьте принципы печати лазерного и струйного принтеров, опишите и сравните их.

- •107. Выберите способ обмена данными между процессором и внешним устройством. Обоснуйте выбор. Напишите процедуру ввода или вывода данных в память эвм в мнемонике команд (уровень ассемблера).

- •108. Приведите основные архитектурные варианта построения операционных систем. Поясните понятие «виртуальная машина»

- •110. Спроектировать устройство микропрограммного управления автономного типа. Источник управляющих кодов – счетчик микрокоманд, число состояний счетчика – 32. Разрядность регистра микрокоманд – 24

- •112. Прерывания как способ изменения адреса в управляющей команде. Привести пример системы прерывания. Описать процедуру опознавания запроса на прерывание с маскированием

- •С линией запроса

- •113. Системы памяти эвм. Назначение каждого типа элементов памяти и место его в иерархии. Что дает для характеристик эвм каждый тип элементов памяти

- •114. Память программ. Виды носителей. Жесткие диски и их твердотельные аналоги

- •115. Компиляторы. Назначение компиляторов, их виды. Последовательность процедуры компиляции

- •116. Контроль информации при последовательной передаче двоичного кода. Методы контроля. Контроль передачи информации при обмене словами (байтами). Методы.

- •117. Приведите основные структуры объединения процессоров в многопроцессорных системах. В чем суть ограничений архитектуры Фон-Неймана

- •118. Сравните структуры двух мпк, имеющих организацию smp и mpp. Приведите их структурные схемы

- •119. Сравните характеристики двух последовательных интерфейсов rs-232с и usb. Приведите структурную организацию интерфейсов и формат передаваемых данных

- •121. Основные понятия процесса проектирования систем управления. Цель процесса проектирования.

- •122. Системный подход к проектированию.

- •123. Структура процесса автоматизированного проектирования

- •124. Основные типы автоматизированных систем, разновидности сапр.

- •Структура сапр

- •125. Стадии проектирования автоматизированных систем и аспекты их описания.

- •126. Особенности проектирования автоматизированных систем.

- •127. Понятие о cals-технологиях.

- •128. Открытые системы.

- •129. Техническое обеспечение систем автоматизированного проектирования

- •130. Типы сетей, методы доступа в сетях, протоколы и стеки протоколов в вычислительных сетях

- •Стеки протоколов и типы сетей в ас

- •131. Сапр систем управления

- •132. Автоматизация управления предприятием, логистические системы.

- •133. Асутп, автоматизированные системы делопроизводства.

- •Автоматизированные системы делопроизводства

- •134. Математическое обеспечение анализа проектных решений.

- •135. Компоненты математического обеспечения, структура вычислительного процесса анализа.

- •136. Математические модели в процедурах анализа на макроуровне

- •137. Математическое обеспечение анализа на микроуровне

- •138. Математическое обеспечение анализа на функционально-логическом уровне

- •139. Математическое обеспечение на системном уровне

- •140. Математическое обеспечение подсистем машинной графики и геометрического моделирования.

- •141. Схемы мультивибратора на транзисторах и оу.

- •142. Схема одновибратора на транзисторах.

- •144. Повторитель на оу

- •145. Двухтактный трансформаторный усилитель мощности, работающий в режиме ав.

- •150. Генератор гармонических колебаний на транзисторах.

- •151. Архитектурные принципы Фон-Неймана. Ограничения.

- •152. Основные понятия информационно-вычислительных систем, классификация по критерию потоков информации

- •153. Совмещение операций и многопрограммная работа. Режим работы в реальном времени

- •154.Типы структур многопроцессорных вс. Параллельные эвм, классификация. Три архитектурных класса машин

- •Классификация по программной организации

- •Классификация по архитектуре

- •155. Принципы ввода-вывода информации в пэвм. Роль и структура контроллера ввода информации

- •Принцип ввода-вывода информации в пэвм. Роль и структура контроллера ввода информации

- •156. Программная реализация ввода чисел с клавиатуры. Привести алгоритм ввода двухразрядного числа с клавиатуры для его суммирования с другими числами

- •157. Вывод и.На дисплей.Принципы отображения информации на экране дисплея. Lcd-дисплеи

- •158. Процедура вывода символьной информации на дискретные индикаторы.

- •159. Загрузчики. Процедура загрузки. Статистические и динамические загрузки.

- •160. Управление реальной памятью. Виртуальная память. Таблица соответствия адресов

155. Принципы ввода-вывода информации в пэвм. Роль и структура контроллера ввода информации

Функционирование любого вычислителя складывается из процедур передачи информации между его отдельными функциональными блоками. При этом передача информации между внутренними РОН называется пересылка, между процессором и памятью чтение/запись, а между памятью и внешними устройствами ввод/вывод информации. Наиболее длинными во времени процедурами считают операции ввода/вывода, поскольку внешние устройства в большинстве случаев имеют меньшее быстродействие, чем процессор или память, поэтому большое внимание на возможные варианты пересылки информации, рассматривая их с точки зрения снижения времени всей процедуры.

Доступ к внешним устройствам в большинстве случаев адресный, т. е. по структуре ввод/вывод не должен отличаться от чтения/записи. Но объем памяти значителен, значительна и шина адреса (минимум 16 разрядов). В тоже время число внешних устройств не может быть физически большим. В вычислителях системы DEC, i360 было принято ограничение на число внешних устройств 255. Это связано с байтом, хотя реально их значительно меньше. Поэтому, сохраняя адресную выборку ВУ ввод/вывод выполнялся с некоторым отличием от чтения/записи:

сигналы разрешения ввода/вывода формировались шинным контролером, в то время ОЗУ/ПЗУ блокируется;

адрес выставлялся на младшем байте и дублировался на старшем. Старший байт практически не использовался.

ШД соединяла выход процессора и вход внешнего устройства (при выводе) и наоборот.

Способы обмена.

Обмен информацией между внешними устройствами и памятью реализуется в одном из трех подходов:

1) Программный режим.

Процессор читает содержимое нужной ячейки памяти ОЗУ и выводит это содержимое (РОН) во внешнее устройство. Не преобразуя информацию процессор выступает лишь как временное хранилище (буферная память). Способ позволяет синхронизировать быстродействие ВУ и памяти. Процедура выполняется за две команды. Адреса на внешнее устройство байтовые. Способ возможен, если в наборе команд имеется команды ввода и вывода.

2) Ввод/вывод с отображением в память.

Наиболее универсальный способ, применяется, когда нет команд ввода/вывода. Последовательность выполнения та же самая: ОЗУCPU, CPUВУ. Отличие: процессор на внешнее устройство выставляет полный адрес, поэтому из адресного пространства исключаются адреса внешних устройств. Вывод с отображением используется часто, поскольку чтение/запись во многом похожи на ввод/вывод. Основной недостаток второго способа — занимается часть адресного пространства. Поэтому способ рекомендуется, если имеются свободные области в адресном пространстве.

3) Прямой доступ к памяти (ПДП).

Суть способа в том, что процессор как бы отключается от ШД и содержимое ОЗУ напрямую копируется во внешнее устройство. Главная цель применения ПДП — сократить время ввода/вывода с одновременным использованием процессора для выполнения следующей операции. Существует три способа обеспечения режима ПДП:

1) с блокировкой процессора.

С приходом запроса на ПДП, процессор отключается, его выходные шины адреса, данных и управления переводятся в третье состояние. Микрокоманды не расшифровываются устройством управления. Процессор не может выполнять операции, хотя тактовый сигнал и питание поступают. Чтобы перевести процессор в такой режим требуется небольшое время. Для обеспечения управления (сигналы выборки, сопровождения, формирование сигналов адреса) необходимо новое устройство, называемое контролер ПДП. Контролер должен заменить процессор при формировании указанных сигналов. Обратный переход также требует некоторого времени. Способ характерен для несложных микропроцессоров имеющих один или несколько регистров команд и не имеющих внутреннего ОЗУ данных.

2) с квантованием цикла.

В каждом цикле обращения к памяти (ОЗУ, ПЗУ) процессор должен успеть выполнить это обращение за время t/2. Во второй половине цикла процессор отключает свои выходы, позволяя контролеру ПДП выставить свой адрес на шину. За второй интервал выполняется процедура ввода/вывода. Такое условие требует быстродействующей памяти, следовательно, смены элементной базы (переход к ЭСЛ). Последнее затрудняет использование такого подхода, поэтому он практически не применяется.

3) с отъемом цикла.

При работе процессора имеющего внутреннюю буферную память команд и данных реализуется ПДП с отъемом цикла. Процессор начинает команду с выборки — обращение к ПЗУ, далее ОЗУ или ввод/вывод. Третий способ заключается в том, что вместо положенного обращения процессора в память (стандартный цикл) выполняется процедура ввода/вывода режима ПДП. При этом процессор выполняет текущую команду, поскольку в его буфере команд стоит очередь следующих друг за другом команд. Выходные разряды процессора переводятся в третье состояние и не оказывают влияния на состояние шин адреса и данных. Главное отличие от первого способа — процессор выполняет текущую, следующую команды не останавливаясь. Поскольку процессор не занимает шины в этом режиме процедура ввода/вывода выполняется как бы одновременно с основной операцией.

В любом режиме ПДП необходим контроллер

— специализированная схема работающая

синхронно с процессором. Контролеры

входят в МП комплекты соответствующих

серий. Основу их составляют счетчики

адреса с произвольной загрузкой и

небольшая схема управления.

любом режиме ПДП необходим контроллер

— специализированная схема работающая

синхронно с процессором. Контролеры

входят в МП комплекты соответствующих

серий. Основу их составляют счетчики

адреса с произвольной загрузкой и

небольшая схема управления.

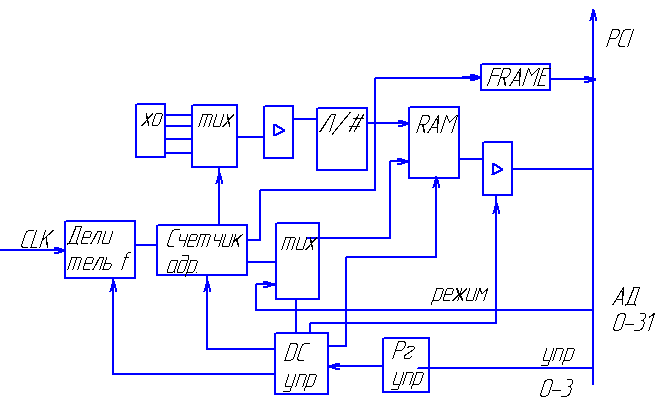

Типовые устройства ввода аналоговой информации подключаются к шинам PCI, ISA, а также к COM и USB. Выпускаются модули ввода, работающие с шинами PCI на разное число входных сигналов (1-128). Модуль встраивается в стандартный слот PCI, тем самым трансформируя универсальную ЭВМ в информационно-измерительную систему. В составе модуля – типовые преобразователи аналог-цифра, буферная память и схема сопряжения с шиной. Модуль работает в 2 режимах: 1. режим измерения - накопление информации; 2. режим ввода информации по шине. В зависимости от характеристик скорость накопления и ввода различна. Процедура накопления м.б. медленной время опроса аналогового сигнала регламентировано теоремой Котельникова. Пересылка же накопленной информации в память ЭВМ выполняется по стандартному протоколу PCI- шиной, с частотой 32 МГц. Возможен пропуск каждого второго такта при неготовности источника, если ОЗУ медленное, то сигнал не успевает сформироваться на буферных шинах PCI в одном такте. Для его извлечения из буферного ОЗУ потребуется 2 такта, т.е. пропуск каждого 2 такта. Скорость ввода при этом уменьшается в 2 раза. Вид устройства

Цикл работы начинается с того, что по команде ввода CPU (контроллер шины PCI) выставляет 4 управляющих разряда – команда инициализации. Сигналы управления с шины записываются в Рг управления сигналом CLK шины и расшифровываются дешифратором в отдельные управляющие сигналы. В этом режиме 1 разряд дешифратора обнуляет состояние делителя и счетчика адреса, и схема приводится в режим накопления: MUX адресов коммутирует на свой вход состояние адресного счетчика, память переводится в режим записи и делитель частоты CLK начинает работать. Последовательный счетчик адреса управляет переключением адресов MUX и формирует текущий адрес для записи результата в память. Пока состояние адреса не переполнилось, входная аналоговая информация преобразуется в двоичный код и полученные разряды пишутся в буферную память в этом режиме сигнал готовности модуля пассивный и контроллер шины PCI не может сам начать чтение. Как только буферная память заполнится, модуль посылает на шину сигнал FRAME, разрешающий контроллеру начать обмен с памятью. MUX переключает 2 вход. В Итоге сигналы адреса с шины поступают на адрес входной памяти. Память переключается в режим чтения и на каждый адрес с шины из памяти читается 32 разряда данных. Контроллер запоминает в своей буферной памяти этот блок до той поры, пока он не прочтется полностью. После этого модуль готов ко 2 циклу ввода - накопление, а контроллер шины PCI отправляет полученный блок в память.