- •Полупроводниковые приборы. Классификация. Область применения.

- •Полупроводниковые диоды. Классификация. Область применения.

- •Полупроводниковые транзисторы. Классификация. Область применения.

- •Полупроводниковые резисторы. Классификация. Область применения.

- •Фотоэлектрические приборы. Классификация. Область применения.

- •Аналоговые усилители. Классификация. Основные характеристики и параметры.

- •Избирательные усилители. Усилители постоянного тока. Усилители мощности. Область применения.

- •Стабилизаторы напряжения. Классификация. Параметры. Область применения.

- •Логические операции. Схемная реализация.

- •Цифровые устройства. Классификация. Комбинационные цу. Дешифраторы. Шифраторы, мультиплексоры, демультиплексоры.

- •Комбинационные сумматоры.

- •Триггера. Классификация. Область применения.

- •Регистры и счетчики. Классификация. Схемы. Область применения.

- •Цифро-аналоговые преобразователи. Назначение. Принцип работы. Матрица r-2r. Область применения.

- •Аналого-цифровые преобразователи. Классификация. Область применения. Параллельные ацп. Ацп поразрядного взвешивания.

- •Интегрирующие ацп. Ацп двойного интегрирования

- •Таймеры. Классификация. Область применения.

- •Источники вторичного напряжения. Структурные схемы. Выпрямители и фильтры.

- •Транзисторный усилительный каскад с общим эммитером

- •Дискретные цифровые сар: математическое описание, z передаточные функции.

- •Анализ дискретных сар

- •23. Логарифмические частотные характеристики сар.

- •24. Переходные функции и переходные характеристики сар. Реакция сар на произвольный входной сигнал

- •25.Типовые звенья сар и их частотные и временные характеристики Апериодическое звено

- •Интегрирующее звено

- •26. Устойчивость линейных сар: определение, теоремы Ляпунова, алгебраический критерий устойчивости Гурвица.

- •27. Частотные критерии устойчивости линейных сар

- •28. Анализ качества линейных сар.

- •29. Синтез корректирующих устройств линейных сар.

- •30. Анализ нелинейных сар.

- •31. Показатели качества эс

- •33. Себестоимость и уровень качества эс

- •34. Корреляционная связь показателей эc Диаграмма разброса (поле корреляции)

- •35. Метод расслаивания чм.

- •36. Метод «авс-анализ»

- •Складские запасы изделий

- •37. Виды статистического контроля эс

- •38. Количественные показатели надежности эс

- •39. Последовательная модель надежности

- •40. Параллельная модель надежности эс

- •41. Основные этапы автоматизации: их характеристики и особенности.

- •42. Назначение, классификация и области применения роботов

- •43. Манипуляционные роботы: типы, характеристики, применение

- •44. Структура механизмов манипуляц-х роботов и характеристики их геом. Свойств

- •45. Приводы манипуляторов и роботов: классификация, особенности применения

- •46. Конструкции схватов промышленных роботов(пр), особенности применения

- •47. Проектирование архитектуры интегрированной компьютерной системы управления (иксу)

- •48. Описание технологического процесса как объекта автоматизированного управления

- •49. Описание производственного процесса как объекта автоматизированного управления: реализации арм различных уровней

- •50. Выбор датчиков тп:типы измерительных устройств, подключение

- •51. Теорема Котельникова (теорема отсчетов). Квазидетерминированные сигналы.

- •52. Преобразование измерительных сигналов. Виды модуляций

- •53. Цифровые частотомеры

- •54. Цифровые фазометры

- •55. Цифровые вольтметры (цв) временного преобразования

- •56. Микропроцессорные цифровые измерительные приборы.

- •57. Резистивные датчики (реостатные, тензорезисторы)

- •58. Электромагнитные датчики (индуктивные, трансформаторные, магнитоупруние).

- •59. Пьезоэлектрические датчики

- •60. Тепловые датчики (термопары, термометры сопротивления).

- •61. Организация и этапы разработки конструкторских документов.

- •62. Виды кд.

- •63. Стандартизация и бнк.

- •64. Виды и типы схем, обозначения по ескд.

- •65. Методы компоновки конструкции эвс.

- •66. Климатические зоны и категории исполнения.

- •67. Способы защиты эвс от влаги.

- •Примеры конструкций средств защиты

- •68. Защита эвс от механических воздействий.

- •Рекомендации по защите рэа от вибрационных воздействий

- •69. Способы обеспечения теплового режима эвс.

- •70. Электромагнитные воздействия. Виды экранов.

- •Экран из ферромагнитного материала с большой магнитной проницаемостью (метод шунтирования экраном).

- •71. Виды линий связи.

- •72. Особенности конструирования бортовых эвс.

- •73. Особенности конструкций персональных эвм.

- •74. Унификация. Разновидности стандартизации.

- •Разновидности стандартизации

- •75. Требования к трассировке пп

- •76. Электромонтажные провода. Припои и флюсы.

- •77. Волоконно-оптические линии связи (волс). Примеры использования.

- •78. Эргономические требования к пультам и органам управления и сигнализации

- •79. Эргономика конструирования лицевой панели прибора.

- •80. Защита эс от воздействия радиации.

- •81. Производственный и технологический процесс и их составляющие

- •82. Исходные данные для разработки технологических процессов. Основные этапы разработки единичного технологического процесса.

- •83. Требования к оформлению технологической документации. Примеры записи технологических операций.

- •84. Основные методы изготовления печатных плат и их особенности

- •85. Конструктивно-технологические разновидности радиоэлектронных узлов и их сопоставительный анализ.

- •86. Основные технологические операции при изготовлении радиоэлектронных узлов с монтажом на поверхность

- •87. Нанесение паяльной пасты и клея и используемое при этом оборудование

- •88. Принципы организации работы сборочных автоматов

- •89. Особенности выполнения пайки при изготовлении электронных модулей ( пайка оплавлением, волной припоя, селективная пайка).

- •90. Особенности выполнения ремонтных работ: демонтаж и монтаж компонентов.

- •91. Материалы, используемые в технологии монтажа на поверхность.

- •92 Виды соединительных операций при сборке.

- •94. Соединение пайкой: разновидности, области применения, примеры выполнения паяных соединений.

- •95. Разработка схемы сборки изделий.

- •96. Нормирование затрат времени при проектировании технологических процессов (штучное и подготовительно-заключительное время, определение такта и ритма выпуска изделий).

- •97. Изготовление деталей эс методом литья

- •98. Разделительные и формообразующие операции холодной штамповки

- •99. Общая характеристика методов формообразования материалов и деталей при производстве эс

- •100. Изготовление электронных модулей по технологии внутреннего монтажа.

- •101. Приведите структуру контроллера (микроЭвм) с раздельными шинами адрес/данные и следующим составом:

- •102. Укажите место на структурной схеме эвм различных интерфейсов. Как объединять эвм в систему? Какие условия следует выполнить при передаче данных? Обоснуйте.

- •103.Расставьте по убыванию значимости параметры эвм по критерию производительности. Охарактеризуйте эти параметры.

- •105. Сопоставьте принципы печати лазерного и струйного принтеров, опишите и сравните их.

- •107. Выберите способ обмена данными между процессором и внешним устройством. Обоснуйте выбор. Напишите процедуру ввода или вывода данных в память эвм в мнемонике команд (уровень ассемблера).

- •108. Приведите основные архитектурные варианта построения операционных систем. Поясните понятие «виртуальная машина»

- •110. Спроектировать устройство микропрограммного управления автономного типа. Источник управляющих кодов – счетчик микрокоманд, число состояний счетчика – 32. Разрядность регистра микрокоманд – 24

- •112. Прерывания как способ изменения адреса в управляющей команде. Привести пример системы прерывания. Описать процедуру опознавания запроса на прерывание с маскированием

- •С линией запроса

- •113. Системы памяти эвм. Назначение каждого типа элементов памяти и место его в иерархии. Что дает для характеристик эвм каждый тип элементов памяти

- •114. Память программ. Виды носителей. Жесткие диски и их твердотельные аналоги

- •115. Компиляторы. Назначение компиляторов, их виды. Последовательность процедуры компиляции

- •116. Контроль информации при последовательной передаче двоичного кода. Методы контроля. Контроль передачи информации при обмене словами (байтами). Методы.

- •117. Приведите основные структуры объединения процессоров в многопроцессорных системах. В чем суть ограничений архитектуры Фон-Неймана

- •118. Сравните структуры двух мпк, имеющих организацию smp и mpp. Приведите их структурные схемы

- •119. Сравните характеристики двух последовательных интерфейсов rs-232с и usb. Приведите структурную организацию интерфейсов и формат передаваемых данных

- •121. Основные понятия процесса проектирования систем управления. Цель процесса проектирования.

- •122. Системный подход к проектированию.

- •123. Структура процесса автоматизированного проектирования

- •124. Основные типы автоматизированных систем, разновидности сапр.

- •Структура сапр

- •125. Стадии проектирования автоматизированных систем и аспекты их описания.

- •126. Особенности проектирования автоматизированных систем.

- •127. Понятие о cals-технологиях.

- •128. Открытые системы.

- •129. Техническое обеспечение систем автоматизированного проектирования

- •130. Типы сетей, методы доступа в сетях, протоколы и стеки протоколов в вычислительных сетях

- •Стеки протоколов и типы сетей в ас

- •131. Сапр систем управления

- •132. Автоматизация управления предприятием, логистические системы.

- •133. Асутп, автоматизированные системы делопроизводства.

- •Автоматизированные системы делопроизводства

- •134. Математическое обеспечение анализа проектных решений.

- •135. Компоненты математического обеспечения, структура вычислительного процесса анализа.

- •136. Математические модели в процедурах анализа на макроуровне

- •137. Математическое обеспечение анализа на микроуровне

- •138. Математическое обеспечение анализа на функционально-логическом уровне

- •139. Математическое обеспечение на системном уровне

- •140. Математическое обеспечение подсистем машинной графики и геометрического моделирования.

- •141. Схемы мультивибратора на транзисторах и оу.

- •142. Схема одновибратора на транзисторах.

- •144. Повторитель на оу

- •145. Двухтактный трансформаторный усилитель мощности, работающий в режиме ав.

- •150. Генератор гармонических колебаний на транзисторах.

- •151. Архитектурные принципы Фон-Неймана. Ограничения.

- •152. Основные понятия информационно-вычислительных систем, классификация по критерию потоков информации

- •153. Совмещение операций и многопрограммная работа. Режим работы в реальном времени

- •154.Типы структур многопроцессорных вс. Параллельные эвм, классификация. Три архитектурных класса машин

- •Классификация по программной организации

- •Классификация по архитектуре

- •155. Принципы ввода-вывода информации в пэвм. Роль и структура контроллера ввода информации

- •Принцип ввода-вывода информации в пэвм. Роль и структура контроллера ввода информации

- •156. Программная реализация ввода чисел с клавиатуры. Привести алгоритм ввода двухразрядного числа с клавиатуры для его суммирования с другими числами

- •157. Вывод и.На дисплей.Принципы отображения информации на экране дисплея. Lcd-дисплеи

- •158. Процедура вывода символьной информации на дискретные индикаторы.

- •159. Загрузчики. Процедура загрузки. Статистические и динамические загрузки.

- •160. Управление реальной памятью. Виртуальная память. Таблица соответствия адресов

108. Приведите основные архитектурные варианта построения операционных систем. Поясните понятие «виртуальная машина»

109. Спроектировать устройство управления программного типа. Число микрокоманд в цикле – не более 7. Привести примеры циклов: выборка команды, чтение памяти и запись в память. Чем определяется период следования тактового сигнала

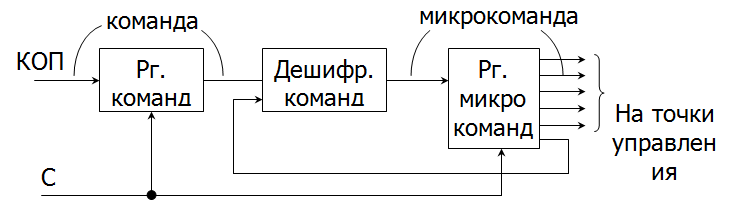

Распространены в CPU с командным управлением. С выхода регистра микрокоманд часть разрядов возвращается на дешифратор – это обратная связь. Цепь разделена регистром и соответственно изменяет состояние по тактовому сигналу «С». Поэтому если в обратной связи 2 разряда, то на двух разрядах вернувшихся на вход дешифратора возможны 4 комбинации. Т.е. из одного КОП мы можем сделать 4 комбинации микрокоманд. Основной блок устройства дешифратор имеет жесткие связи (пайка, металл на ИМС), поэтому изменить микрокоды возможно только если заменить схему на новую. Предлагалось сделать дешифратор на основе программируемой матрицы. Мы запрограммировали матрицу – получили свои микрокоды. Где-то эти микрокоды нас не устроили. Мы можем перепрограммировать этот дешифратор и получить новые микрокоды. Микрокоды считаются секретными, поскольку именно от них зависит время выполнения команды. На практике дешифраторы размещают на кристалле процессора и настраивают (программируют) металлом, выполняя соединение в матрице. В тех случаях, когда время выполнения команд должно быть строго фиксировано лучше применять микропрограммный способ управления.

110. Спроектировать устройство микропрограммного управления автономного типа. Источник управляющих кодов – счетчик микрокоманд, число состояний счетчика – 32. Разрядность регистра микрокоманд – 24

В отличие от управления с жесткими связями, в микропрограммных устройствах используют не дешифратор команд, а микропрограммную память с тем, чтобы просто из нее извлекать коды. На вход устройства подается код операции (управляющий код из ПЗУ). Однако из этого кода мы получаем начальный адрес подпрограммы которая выполнит нужную команду. Для чего схема управления адресом микрокоманд на всякий такт генератора формирует следующий адрес по которому из микропрограммной памяти мы читаем код микрокоманды. Обычно разбитый по полям (как 8 полей тренажера МТ 1804). Обратная связь из памяти и с выхода регистра позволяет выполнять переходы на следующий адрес (поле управляет видом перехода и адресом перехода если нужно). На схему управления могут подаваться сигналы признаков с выхода АЛУ CPU. Признаки позволяют выполнять условные переходы. Регистр микрокоманд включает не только сами коды управления посылаемые на микропроцессор, но и дополнительные сигналы которые могут управлять другими блоками схемы (мультиплекс. сдвига, чтение/запись из памяти, разрешение доступа в ОЗУ, ПЗУ и т.д.). Поскольку МПП можно сделать программируемой, то мы можем сами корректировать микрокоманды, делать сигналы управления такими какими они нам нужны в реальности. Основное достоинство микропрограммного способа – гибкость в написании кодов.

Недостаток: большие аппаратные затраты т.к. разрядность микрокоманды может быть большой до 100 и больше, что требует большого количества корпусов и регистров.

111. Привести примеры процедур с различными способами адресации для пересылки содержимого ячейки памяти команд в ячейку памяти данных в мнемонике команд, адресация в пределах одной страницы (64 кб). Пояснить необходимость модификации адресов для доступа к данным и возможные их способы

Принцип работы любого вычислителя основан на использовании содержимого памяти: по адресу читаем содержимое, модифицируем его и возвращаем назад в память. При этом в вычислителе выделяем два потока информации: 1) команды от ПЗУ до регистра команд, адрес выбирает команды устанавливаемые счетчиком адресов процессора. Последовательная выборка, переходы выполняются только с использованием этого счетчика. 2) данные. Объем памяти данных значительно больше памяти команд. К данным процессора обращается по адресу зачастую зависимому от алгоритма – пользователя. Поэтому чтение (запись) возможно с применением нескольких способов формирования адреса данных. Эти способы называют – адресацией. Переход от одного типа к другому объясняется стремлением пользователя упростить процедуру написания программы, сэкономить память команд. Основными типами адресации данных являются: 1) прямая адресация 2) косвенная 3) непосредственная.

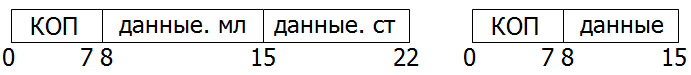

прямая адресация применяется для R/W данных в ОЗУ. Формат команды прямой адресации имеет вид.

КОП младший байт старший байт

Прямая адресация наиболее проста. Она обеспечивает произвольный доступ к любой ячейки памяти в интервале всего адресного пространства. В большинстве систем команд разрядность 16, следовательно, прямая адресация обеспечит доступ к любой ячейке памяти в интервале 64К.

Недостаток – способ не позволяет произвольно обращаться к большей памяти. Прямая адресация осталась основной в малых вычислителях, в которых нет расширения памяти. В ЭВМ прямая адресация применяется для работы внутри сегмента. Последовательность прохождения сигнала: процессор читает КОП по признаку. В КОП он выбирает следующие два бита, записывает их в регистр адреса ,и содержимое регистра адреса выставляет на шину адреса. От туда идет в ОЗУ и из него в регистр входа данных процессора. Т. о. Такая команда требует 4 цикла при выполнении. Прямая адресация основа для расширения модификации адресов.

2) непосредственная адресация. Применяют для ввода данных, начальных данных, констант в ОЗУ. Эти данные должны храниться в ПЗУ. Эти данные не могут быть модифицированы, поэтому работа с ними возможна с ними только через ОЗУ. Такая адресация применяется во всех командах загрузки данных. Формат

КОП

данные КОП младший байт старший

байт данные

КОП

данные КОП младший байт старший

байт данные

Основные ограничения на непосредственную адресацию – это сам операнд. Поскольку операнд должен храниться в памяти команд невозможно оперативно его изменить. Отсюда команды применяются только для загрузки.

3) Наиболее удобным способом обращения к ОЗУ – косвенная адресация. Как правило она применяется при работе с масштабами: формирование масштаба, накопление данных, ввод данных, при чтении и выводе информации на дисплей через ЦАП на процессор. В основе косвенного метода лежит использование промежуточного ОЗУ для получения физического адреса. Последовательность формирования адреса:

КОП адрес промежуточное ОЗУ ША ОЗУ

В поле команды за КОП располагается адресная часть, ее разрядность не велика, поэтому она занимает немного места. Содержимое адресной части: адрес 1 поступает на промежуточное ОЗУ, выбирая из него ячейку содержащую физический адрес. Последний пересылается на ША. По нему выбирается нужная ячейка ОЗУ. В старых разработках в качестве промежуточного ОЗУ применяли специальные схемы СОЗУ малой емкости. Число слов хранения в них 16-32. В тоже время, разрядность таких СОЗУ соответствовала полной разрядности памяти данных (16,20). С появлением процессора промежуточное ОЗУ начали размещать непосредственно на кристалле микропроцессора, поэтому связь кода команды с промежуточным ОЗУ – по внутренним сигналам процессора. Пользователь не ощущает этого промежуточного ОЗУ. Га ША появляется уже физический адрес. В отличие от прямой адресации косвенная: 1) формат команды короче, он занимает один байт. Адресная часть размещена в КОП. Количество адресов (объем промежуточного ОЗУ) уменьшилось, но команда занимает в памяти меньше места. 2) Любая команда прямой адресации требует нескольких обращений в память команд. КОП, адрес младший, адрес старший и адрес доступа к данным, т.е. минимум 4 раза на ША. Косвенная адресация обходится двумя циклами: КОП, физический адрес доступа к данным. В косвенной адресации прежде чем воспользоваться ее, требуется определить содержимое памяти: в регистровую пару необходимо занести адрес начальной ячейки памяти данных, т.е. определить составные этой памяти. Если это не сделать, обращение произойдет по нулевому адресу, либо по случайному адресу. При обращении к следующей ячейке содержимое регистровой пары следует увеличить (уменьшить) на единицу специальной командой. Команды косвенной адресации дают заметное преимущество, если массив пересылает данных более 10. Тем более, что косвенная адресация легко вписывается в цикл – прямая же нет. Косвенная адресация позволяет просто организовать цикл в программе, прямая – затруднительно.

(2) С расширением адресного пространства ОЗУ стала проблема увеличения разрядности адреса без изменения процессора. С этой целью разрабатываются различные подходы к получению физического адреса при сохранности структуры самого процессора.

1) страничная адресация – это варианты позволяющие увеличить разрядность шины адреса. Дополнительно к адресной шине процессор комплексируется разряды с триггера адреса.

Все способы модификации ориентируются на критерий: минимальное время формирования адреса при максимальном адресном пространстве. Прежде чем начать работу с процессором надо определить все его регистры. Можно использовать и композицию, объеденные способы увеличения адресов, если возникает в том необходимость. В системе DEC существуют два дополнительных способа: автоинкремент и автодекримент. При косвенной адресации увеличение/ уменьшение на1 (2) содержимого адресного регистра происходит автоматически после обращения в память.

Рассмотренные способы адресации позволяют успешно обращаться к любым ячейкам памяти в предельно максимальный адрес системы.

Согласно принципам программного управления вся информация хранится в ячейках памяти по адресам, т.е. при работе ЭВМ необходимо как-то формировать адреса для доступа к ячейкам памяти. Адресный счетчик CPU формирует адреса для схемы памяти команд. И если нам нужно обратиться за командой – адреса берем из счетчика адреса, либо с его помощью. Существует 3 способа формирования адресов (способов добычи данных из памяти), также есть один четвертый по умолчанию.

П

рямая

адресация.

Формат команды прямой адресации должен

иметь min

2 части: код операции и адресную часть.

В коде операции содержится управляющий

код для выполнения команды. В этом коде

включен тип адресации, направление

передачи данных, источник/приемник.

Адресная

часть

– это адрес 1 байт, 2 байта той ячейки,

к которой производится доступ. Если

адрес 1 байт – эти команды работают с

внешними устройствами (у них адрес

однобайтный). Адреса ВУ вынесены из

общего адресного пространства.

Двухбайтный адрес – обращение к памяти

данных. 16-разрядов данных позволяет

обращаться лишь к 64К адресов. Этот объем

называется страницей. Команда прямой

адресации содержит прямой адрес т.е. в

коде операции содержится код команды,

во 2-ом байте младший байт прямого

адреса, в 3-ем старший байт прямого

адреса. Деление на байты вызвано тем,

что система команд работает с однобайтной

шиной. Основной недостаток

адресации – значительное время

требующееся на подготовку самой

пересылки.

рямая

адресация.

Формат команды прямой адресации должен

иметь min

2 части: код операции и адресную часть.

В коде операции содержится управляющий

код для выполнения команды. В этом коде

включен тип адресации, направление

передачи данных, источник/приемник.

Адресная

часть

– это адрес 1 байт, 2 байта той ячейки,

к которой производится доступ. Если

адрес 1 байт – эти команды работают с

внешними устройствами (у них адрес

однобайтный). Адреса ВУ вынесены из

общего адресного пространства.

Двухбайтный адрес – обращение к памяти

данных. 16-разрядов данных позволяет

обращаться лишь к 64К адресов. Этот объем

называется страницей. Команда прямой

адресации содержит прямой адрес т.е. в

коде операции содержится код команды,

во 2-ом байте младший байт прямого

адреса, в 3-ем старший байт прямого

адреса. Деление на байты вызвано тем,

что система команд работает с однобайтной

шиной. Основной недостаток

адресации – значительное время

требующееся на подготовку самой

пересылки.

Достоинства: логически простая т.к. адрес видит пользователь, он сам пишет к какой ячейке обратиться. Поскольку команда длинная, она используется не часто, обычно когда требуется работать с выделенными, замечательными, особенными ячейками памяти.

Косвенная адресация. Основной тип адресного доступа к памяти данных. Работает с массивами (малыми, большими), таблицами. Код операции включает только код операции и признак адресации. Чтобы выполнить такую команду нужно предварительно заготовить в каких либо регистрах CPU адрес который эта команда привлечет для своего выполнения. В малых микропроцессорах для этих целей существуют регистровые пары HL, DE, BC. В 16-разрядных и выше CPU используются самостоятельные регистры (базовые, индексные). Смысл косвенной адресации состоит в том, что содержимое адресного регистра просто модифицировать.

<Ci+1> инкремент

<Ci-1> декремент

Команда косвенной адресации выполняется в следующей последовательности:

0 подготовить адрес

1 выбираем КОП (Сч.А -> ША -> ПЗУ -> <КОП> ->ШД -> Рг.команд процессора)

2 <HL> -> ША -> ОЗУ -> <данные> -> ШД -> Рг.процессора

1-й цикл: выборка стандартная

2-ой цикл: содержимое регистровой пары (адресного регистра в CPU) коммутируем на ША и выполняем обращение к памяти данных (ОЗУ). Выбирается ячейка из которой можно прочитать в CPU либо в которую можно записать из Рг.процессора. Косвенной – эта адресация называется потому, что адрес не присутствует в коде команды, он подразумевается как находящийся в CPU. При описании команды указываем не сам адрес, а лишь место его хранения. Косвенная адресация позволяет использовать цикл для работы с массивом произвольной длины.

Непосредственная адресация.

Любая процедура решения задачи предусматривает ввод начальных, исходных данных. Эти данные обычно берутся из памяти команд. Непосредственно в командах указываем начальные данные, которые присваиваются той или иной переменной. Единственный способ сохранить их вписать в память команд. Поэтому команды непосредственной адресации работают с данными, но эти данные хранятся в ПЗУ. Как таковой адрес ячейки для обращения к ОЗУ нам не нужен. Нам проще писать эти данные в команды и читать их вместе с кодами операций. Таким образом процедура инициализации предусматривает ввод начальных данных из памяти команд. Последовательность выполнения команды:

1-ое ввод 1 байта начальных данных

- выборка Сч.А -> ША -> ПЗУ -> <КОП> -> ШД -> Рг.команд процессора

2-ое Сч.А+1 -> ША -> ПЗУ -> <начальн. данные> -> ШД -> Рг.процессора

Способ непосредственной адресации можно назвать способом ввода начальных данных из ПЗУ. Поскольку как такового адреса в ПЗУ мы не ищем.

Кроме основных существует: прямая регистровая – когда выполняется пересылка из одного регистра в другой в самом CPU, в память данных мы не ходим, но адреса регистров нужно определить, они прописываются в коде операции, в старшей и младшей части кода.

Неявная адресация – обычно это выбор нескольких замечательных ячеек. Ее можно назвать адресацией по умолчанию. Адрес ячейки хранится где либо в CPU. Причем мы не интересуемся этим адресом. Например запись в программный стэк выполняется неявно: по содержанию указателя стэка.

Главным недостатком является то, что разрядность адреса в них небольшая что ограничивает объем адресуемой памяти одной страницей (64К). Поэтому в современных системах, где ОЗУ имеет большой объем применяют модификацию адресов – способ увеличить длину адреса и тем самым дать возможность увеличить объем памяти или сегодня получить возможность просто изменять адрес (прыгать по адресному пространству).

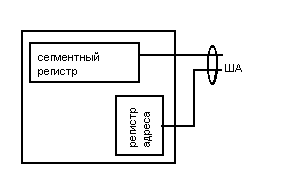

Первым способом модификации адресов считается страничная адресация. К типовой ША, например 16-разрядов добавляем еще 4 взятых с выхода регистра. Информацию в этот регистр мы можем записать с ШД, обратившись к нему как к любому внешнему устройству (16+4=20) и объем адресного пространства увеличивается до 1 Мбайта. Все поле памяти делим на страницы номера которых хранит 4-разрядный регистр. Пока его состояние неизменно мы находимся в пределах одной страницы (64К). Чтобы перейти на другую требуется поменять состояние регистра. Такое подключение использовали в системе сбора, когда применялся небольшой МП с 16-разрядной ША.

Использование сумматоров в адресных цепях CPU. Способ оказался более перспективен т.к. легко модифицируется, занимает мало времени. В CPU имеются 16-разрядные регистры. Поэтому напрямую чтение регистра не увеличивает разрядность. Тогда предложили объединить содержимое двух регистров на сумматоре по следующей схеме. 4 младших разряда одного регистра выводятся напрямую на ША, а оставшиеся 12 объединяются (складываются) в сумматоре с 16-разрядами другого регистра. Получаем 16-разрядов старших и в целом 20 разрядов по адресу. Объединение содержимого двух регистров позволило выполнить быстрые манипуляции с адресами.

С ростом разрядности внутренних регистров до 32 модификация адресов проводится с другой целью: возможность быстрого изменения адреса в текущей программе. С этой целью выбираем некий базовый регистр (BX) и регистр смещения. Счетчик адреса в такой манипуляции сохраняет свое старое состояние (+1), но диапазон адресов другой. В зависимости от того какой регистр мы используем в качестве базового (начального) и различают виды модификации: базовая – использует базовый регистр BX; индексная – использует индексный регистр; индексно – относительная адресация это совместное использование индексной и базовой относительной адресации.

Использование комбинаций адресных регистров позволило относительно быстро менять физический адрес выставляемый на ША. При этом состояние счетчика адреса практически не меняется и мы контролируем через счетчик адреса начальные адреса. Стоит такая модификация дополнительных затрат оборудования: сумматор, дополнительный регистр, которые в устройстве управления явно не предусмотрены.