- •Полупроводниковые приборы. Классификация. Область применения.

- •Полупроводниковые диоды. Классификация. Область применения.

- •Полупроводниковые транзисторы. Классификация. Область применения.

- •Полупроводниковые резисторы. Классификация. Область применения.

- •Фотоэлектрические приборы. Классификация. Область применения.

- •Аналоговые усилители. Классификация. Основные характеристики и параметры.

- •Избирательные усилители. Усилители постоянного тока. Усилители мощности. Область применения.

- •Стабилизаторы напряжения. Классификация. Параметры. Область применения.

- •Логические операции. Схемная реализация.

- •Цифровые устройства. Классификация. Комбинационные цу. Дешифраторы. Шифраторы, мультиплексоры, демультиплексоры.

- •Комбинационные сумматоры.

- •Триггера. Классификация. Область применения.

- •Регистры и счетчики. Классификация. Схемы. Область применения.

- •Цифро-аналоговые преобразователи. Назначение. Принцип работы. Матрица r-2r. Область применения.

- •Аналого-цифровые преобразователи. Классификация. Область применения. Параллельные ацп. Ацп поразрядного взвешивания.

- •Интегрирующие ацп. Ацп двойного интегрирования

- •Таймеры. Классификация. Область применения.

- •Источники вторичного напряжения. Структурные схемы. Выпрямители и фильтры.

- •Транзисторный усилительный каскад с общим эммитером

- •Дискретные цифровые сар: математическое описание, z передаточные функции.

- •Анализ дискретных сар

- •23. Логарифмические частотные характеристики сар.

- •24. Переходные функции и переходные характеристики сар. Реакция сар на произвольный входной сигнал

- •25.Типовые звенья сар и их частотные и временные характеристики Апериодическое звено

- •Интегрирующее звено

- •26. Устойчивость линейных сар: определение, теоремы Ляпунова, алгебраический критерий устойчивости Гурвица.

- •27. Частотные критерии устойчивости линейных сар

- •28. Анализ качества линейных сар.

- •29. Синтез корректирующих устройств линейных сар.

- •30. Анализ нелинейных сар.

- •31. Показатели качества эс

- •33. Себестоимость и уровень качества эс

- •34. Корреляционная связь показателей эc Диаграмма разброса (поле корреляции)

- •35. Метод расслаивания чм.

- •36. Метод «авс-анализ»

- •Складские запасы изделий

- •37. Виды статистического контроля эс

- •38. Количественные показатели надежности эс

- •39. Последовательная модель надежности

- •40. Параллельная модель надежности эс

- •41. Основные этапы автоматизации: их характеристики и особенности.

- •42. Назначение, классификация и области применения роботов

- •43. Манипуляционные роботы: типы, характеристики, применение

- •44. Структура механизмов манипуляц-х роботов и характеристики их геом. Свойств

- •45. Приводы манипуляторов и роботов: классификация, особенности применения

- •46. Конструкции схватов промышленных роботов(пр), особенности применения

- •47. Проектирование архитектуры интегрированной компьютерной системы управления (иксу)

- •48. Описание технологического процесса как объекта автоматизированного управления

- •49. Описание производственного процесса как объекта автоматизированного управления: реализации арм различных уровней

- •50. Выбор датчиков тп:типы измерительных устройств, подключение

- •51. Теорема Котельникова (теорема отсчетов). Квазидетерминированные сигналы.

- •52. Преобразование измерительных сигналов. Виды модуляций

- •53. Цифровые частотомеры

- •54. Цифровые фазометры

- •55. Цифровые вольтметры (цв) временного преобразования

- •56. Микропроцессорные цифровые измерительные приборы.

- •57. Резистивные датчики (реостатные, тензорезисторы)

- •58. Электромагнитные датчики (индуктивные, трансформаторные, магнитоупруние).

- •59. Пьезоэлектрические датчики

- •60. Тепловые датчики (термопары, термометры сопротивления).

- •61. Организация и этапы разработки конструкторских документов.

- •62. Виды кд.

- •63. Стандартизация и бнк.

- •64. Виды и типы схем, обозначения по ескд.

- •65. Методы компоновки конструкции эвс.

- •66. Климатические зоны и категории исполнения.

- •67. Способы защиты эвс от влаги.

- •Примеры конструкций средств защиты

- •68. Защита эвс от механических воздействий.

- •Рекомендации по защите рэа от вибрационных воздействий

- •69. Способы обеспечения теплового режима эвс.

- •70. Электромагнитные воздействия. Виды экранов.

- •Экран из ферромагнитного материала с большой магнитной проницаемостью (метод шунтирования экраном).

- •71. Виды линий связи.

- •72. Особенности конструирования бортовых эвс.

- •73. Особенности конструкций персональных эвм.

- •74. Унификация. Разновидности стандартизации.

- •Разновидности стандартизации

- •75. Требования к трассировке пп

- •76. Электромонтажные провода. Припои и флюсы.

- •77. Волоконно-оптические линии связи (волс). Примеры использования.

- •78. Эргономические требования к пультам и органам управления и сигнализации

- •79. Эргономика конструирования лицевой панели прибора.

- •80. Защита эс от воздействия радиации.

- •81. Производственный и технологический процесс и их составляющие

- •82. Исходные данные для разработки технологических процессов. Основные этапы разработки единичного технологического процесса.

- •83. Требования к оформлению технологической документации. Примеры записи технологических операций.

- •84. Основные методы изготовления печатных плат и их особенности

- •85. Конструктивно-технологические разновидности радиоэлектронных узлов и их сопоставительный анализ.

- •86. Основные технологические операции при изготовлении радиоэлектронных узлов с монтажом на поверхность

- •87. Нанесение паяльной пасты и клея и используемое при этом оборудование

- •88. Принципы организации работы сборочных автоматов

- •89. Особенности выполнения пайки при изготовлении электронных модулей ( пайка оплавлением, волной припоя, селективная пайка).

- •90. Особенности выполнения ремонтных работ: демонтаж и монтаж компонентов.

- •91. Материалы, используемые в технологии монтажа на поверхность.

- •92 Виды соединительных операций при сборке.

- •94. Соединение пайкой: разновидности, области применения, примеры выполнения паяных соединений.

- •95. Разработка схемы сборки изделий.

- •96. Нормирование затрат времени при проектировании технологических процессов (штучное и подготовительно-заключительное время, определение такта и ритма выпуска изделий).

- •97. Изготовление деталей эс методом литья

- •98. Разделительные и формообразующие операции холодной штамповки

- •99. Общая характеристика методов формообразования материалов и деталей при производстве эс

- •100. Изготовление электронных модулей по технологии внутреннего монтажа.

- •101. Приведите структуру контроллера (микроЭвм) с раздельными шинами адрес/данные и следующим составом:

- •102. Укажите место на структурной схеме эвм различных интерфейсов. Как объединять эвм в систему? Какие условия следует выполнить при передаче данных? Обоснуйте.

- •103.Расставьте по убыванию значимости параметры эвм по критерию производительности. Охарактеризуйте эти параметры.

- •105. Сопоставьте принципы печати лазерного и струйного принтеров, опишите и сравните их.

- •107. Выберите способ обмена данными между процессором и внешним устройством. Обоснуйте выбор. Напишите процедуру ввода или вывода данных в память эвм в мнемонике команд (уровень ассемблера).

- •108. Приведите основные архитектурные варианта построения операционных систем. Поясните понятие «виртуальная машина»

- •110. Спроектировать устройство микропрограммного управления автономного типа. Источник управляющих кодов – счетчик микрокоманд, число состояний счетчика – 32. Разрядность регистра микрокоманд – 24

- •112. Прерывания как способ изменения адреса в управляющей команде. Привести пример системы прерывания. Описать процедуру опознавания запроса на прерывание с маскированием

- •С линией запроса

- •113. Системы памяти эвм. Назначение каждого типа элементов памяти и место его в иерархии. Что дает для характеристик эвм каждый тип элементов памяти

- •114. Память программ. Виды носителей. Жесткие диски и их твердотельные аналоги

- •115. Компиляторы. Назначение компиляторов, их виды. Последовательность процедуры компиляции

- •116. Контроль информации при последовательной передаче двоичного кода. Методы контроля. Контроль передачи информации при обмене словами (байтами). Методы.

- •117. Приведите основные структуры объединения процессоров в многопроцессорных системах. В чем суть ограничений архитектуры Фон-Неймана

- •118. Сравните структуры двух мпк, имеющих организацию smp и mpp. Приведите их структурные схемы

- •119. Сравните характеристики двух последовательных интерфейсов rs-232с и usb. Приведите структурную организацию интерфейсов и формат передаваемых данных

- •121. Основные понятия процесса проектирования систем управления. Цель процесса проектирования.

- •122. Системный подход к проектированию.

- •123. Структура процесса автоматизированного проектирования

- •124. Основные типы автоматизированных систем, разновидности сапр.

- •Структура сапр

- •125. Стадии проектирования автоматизированных систем и аспекты их описания.

- •126. Особенности проектирования автоматизированных систем.

- •127. Понятие о cals-технологиях.

- •128. Открытые системы.

- •129. Техническое обеспечение систем автоматизированного проектирования

- •130. Типы сетей, методы доступа в сетях, протоколы и стеки протоколов в вычислительных сетях

- •Стеки протоколов и типы сетей в ас

- •131. Сапр систем управления

- •132. Автоматизация управления предприятием, логистические системы.

- •133. Асутп, автоматизированные системы делопроизводства.

- •Автоматизированные системы делопроизводства

- •134. Математическое обеспечение анализа проектных решений.

- •135. Компоненты математического обеспечения, структура вычислительного процесса анализа.

- •136. Математические модели в процедурах анализа на макроуровне

- •137. Математическое обеспечение анализа на микроуровне

- •138. Математическое обеспечение анализа на функционально-логическом уровне

- •139. Математическое обеспечение на системном уровне

- •140. Математическое обеспечение подсистем машинной графики и геометрического моделирования.

- •141. Схемы мультивибратора на транзисторах и оу.

- •142. Схема одновибратора на транзисторах.

- •144. Повторитель на оу

- •145. Двухтактный трансформаторный усилитель мощности, работающий в режиме ав.

- •150. Генератор гармонических колебаний на транзисторах.

- •151. Архитектурные принципы Фон-Неймана. Ограничения.

- •152. Основные понятия информационно-вычислительных систем, классификация по критерию потоков информации

- •153. Совмещение операций и многопрограммная работа. Режим работы в реальном времени

- •154.Типы структур многопроцессорных вс. Параллельные эвм, классификация. Три архитектурных класса машин

- •Классификация по программной организации

- •Классификация по архитектуре

- •155. Принципы ввода-вывода информации в пэвм. Роль и структура контроллера ввода информации

- •Принцип ввода-вывода информации в пэвм. Роль и структура контроллера ввода информации

- •156. Программная реализация ввода чисел с клавиатуры. Привести алгоритм ввода двухразрядного числа с клавиатуры для его суммирования с другими числами

- •157. Вывод и.На дисплей.Принципы отображения информации на экране дисплея. Lcd-дисплеи

- •158. Процедура вывода символьной информации на дискретные индикаторы.

- •159. Загрузчики. Процедура загрузки. Статистические и динамические загрузки.

- •160. Управление реальной памятью. Виртуальная память. Таблица соответствия адресов

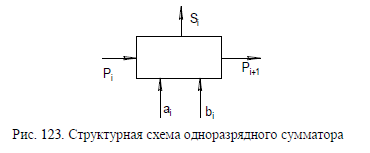

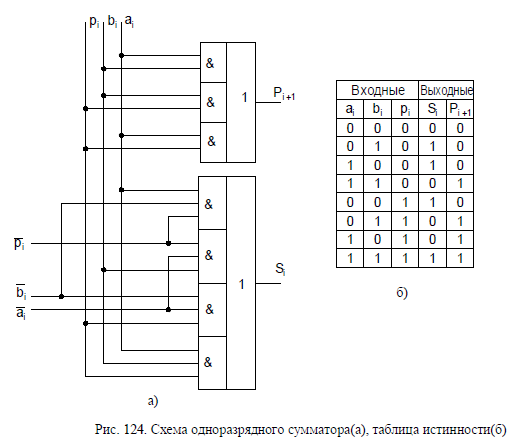

Комбинационные сумматоры.

Комбинационный сумматор – это цифровое устройство, предназначенное для арифметического сложения чисел, представленных в виде двоичных кодов.

Обычно сумматор представляет собой комбинацию одноразрядных сумматоров. При сложении двух чисел в каждом разряде производится сложение трех цифр: цифры первого слагаемого ai, цифры второго слагаемого bi и цифры переноса из младшего разряда Pi. В результате суммирования на выходных шинах получается сумма Si и перенос в старший разряд Pi+1.

На рис. 139,б приведена таблица истинности одноразрядного сумматора.

Используя карты Вейча, можно записать ФАЛ, описывающие работу сумматора, и построить схему сумматора.

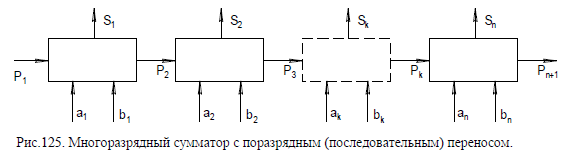

Параллельный (многоразрядный) сумматор может быть составлен из одноразрядных сумматоров путем их соединения по сигналам переноса Pi.

Сумматоры с поразрядным переносом выпускаются в виде микросхем на 2 и 4 разряда. Например, К561ИМ1 – сумматор на 4 разряда. Для увеличения разрядности до 8 необходимо взять две микросхемы и соединить их последовательно по цепи переноса. Сумматор с поразрядным последовательным переносом наиболее прост с точки зрения схемной реализации, однако имеет низкое быстродействие. Время выполнения операции Топ зависит от разрядности.

Tоп1n,

где 1 – время распространения переноса в одноразрядном сумматоре;

n – количество разрядов.

Для повышения быстродействия используются сумматоры с параллельным переносом.

При построении арифметико-логических устройств (АЛУ) необходимо наряду с операцией суммирования выполнять ряд логических операций. Для этого можно использовать ИС К561ИП3, которая представляет собой четырехразрядное АЛУ, выполняющее 16 логических и арифметико-логических операций.

Триггера. Классификация. Область применения.

Триггером называется цифровое устройство, которое может находиться в одном из двух устойчивых состояний и переходит из одного состояния в другое под действием входных сигналов. Триггеры можно классифицировать по способу приема информации, принципу построения, функциональным возможностям. По способу приема информации триггеры подразделяются на асинхронные и синхронные. Асинхронный триггер изменяет свое состояние в момент прихода сигнала на его информационные входы. Синхронные триггеры изменяют свое состояние под воздействием входных сигналов только в момент прихода активного сигнала на его синхронизирующий вход С.По виду активного сигнала, действующего на информационных входах, триггеры подразделяются на статические и динамические. Первые переключаются потенциалом (уровнем напряжения), а вторые – перепадом (передним или задним фронтом импульса). Входные информационные сигналы могут быть прямыми и инверсными.

По принципу построения триггеры со статическим управлением можно подразделить на одноступенчатые и двухступенчатые. В одноступенчатых триггерах имеется одна ступень запоминания. В двухступенчатых триггерах имеются две ступени запоминания. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе.

По функциональным возможностям триггеры делятся на: RS-триггеры, D-триггеры, T-триггеры, JK-триггеры, VD и VT-триггеры.

Триггеры характеризуются быстродействием, чувствительностью, потребляемой мощностью, помехоустойчивостью, функциональными возможностями.

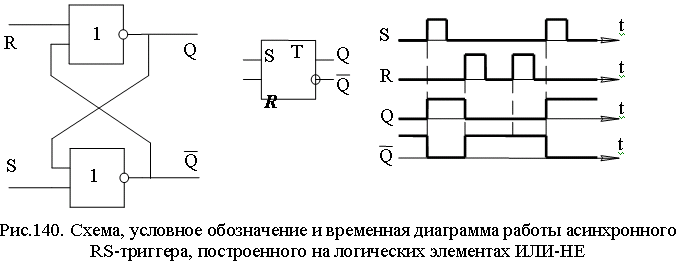

Асинхронный

RS-триггер

имеет две входные информационные шины

R

и S

и две выходные шины Q

и

.

Под действием входного сигнала S

триггер устанавливается в состояние 1

(Q=1,

=0),

а под действием сигнала R

– переходит в состояние "0" (Q=1,

=0).

.

Под действием входного сигнала S

триггер устанавливается в состояние 1

(Q=1,

=0),

а под действием сигнала R

– переходит в состояние "0" (Q=1,

=0).

Таблица истинности для R-S триггера имеет вид:

Здесь одновременная подача входных сигналов R и S запрещена. Из диаграммы Вейча следует:

RS-триггеры строятся на базе логических элементов ИЛИ-НЕ или И-НЕ.

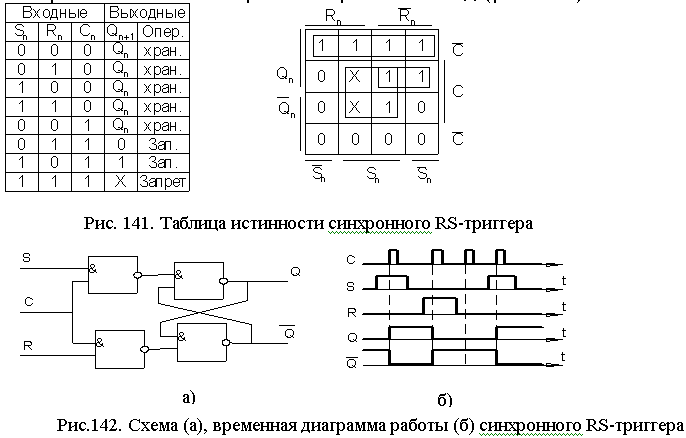

Синхронный

RS-триггер

имеет дополнительный синхронизирующий

вход C.

Таблица истинности и карта Вейча имеют

вид (рис.141):

Синхронный

RS-триггер

имеет дополнительный синхронизирующий

вход C.

Таблица истинности и карта Вейча имеют

вид (рис.141):

Триггер может быть построен на логических элементах И-НЕ, ИЛИ-НЕ. На рис.142 приведена схема синхронного RS-триггера на логическом элементе И-НЕ. Работа триггера описывается уравнением

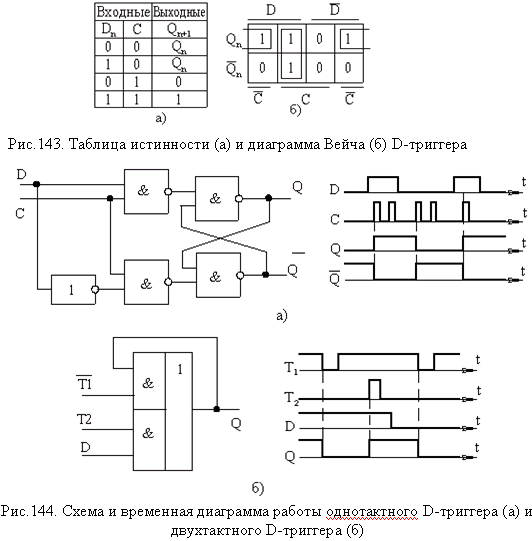

D-триггер

имеет только один информационный вход

D,

с которого информация записывается и

выдается на выходные шины по сигналу

синхронизации. Это означает, что

D-триггеры

могут быть только синхронными. Таблица

истинности и карта Вейча приведены на

рис.143. Работа триггера из карты Вейча

описывается выражением

.

.

D-триггеры могут быть однотактными и двухтактными.

Работа триггеров поясняется временной диаграммой работы.

Разновидностью D-триггера является VD-триггер, который дополнительно снабжен входом разрешения работы V. При V=1 триггер функционирует как обычный D-триггер, при V=0 работает в режиме хранения информации.

Триггеры выпускаются в виде ИС. В одном корпусе может быть 2, 4, 8, 16 триггеров.

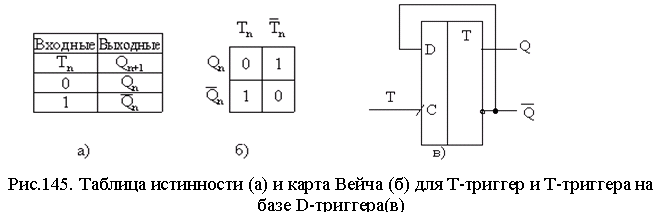

Т-триггеры имеют один информационный вход Т и изменяют свое состояние на противоположное при поступлении на этот вход сигнала Т.

Функционирование Т-триггера описывается уравнением

Т-триггер можно построить на базе D – триггера.

Более надежны двухступенчатые Т-триггеры, выполненные в виде двух последовательно соединенных триггеров – ведущего и ведомого. При этом новая информация вначале записывается в первый триггер, а затем переписывается во второй. На принципиальных схемах двухступенчатые триггеры обозначаются сдвоенной буквой ТТ.

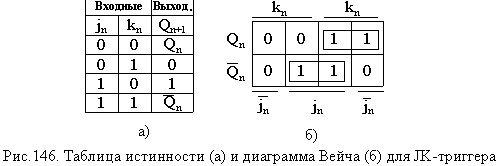

JK-триггер в отличие от RS-триггера не имеет запрещенных комбинаций входных сигналов. При поступлении сигналов на оба входа J и K триггер изменяет свое состояние на противоположное. Уравнение работы асинхронного и синхронного JK-триггеров имеет вид:

-

для асинхронного;

-

для асинхронного;

-

для синхронного.

-

для синхронного.

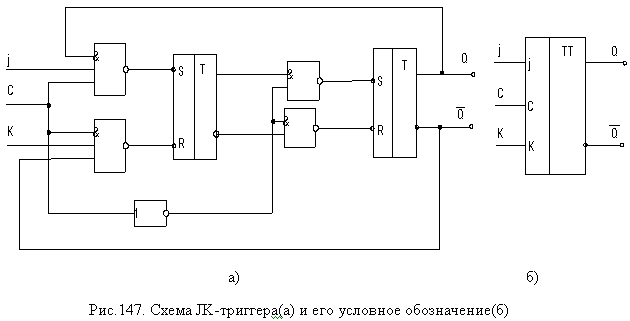

На рис.147 приведена схема JK-триггера, построенная на базе двухступенчатого RS-триггера с запрещенными связями.

JK-триггер является универсальным триггером. На его основе можно построить RS, D, T-триггеры.

Триггеры с динамическим управлением. в них переключение триггера происходит в течение короткого времени вблизи фронта или среза импульса синхронизации. Если триггер переключается передним фронтом синхроимпульса, то он имеет прямой динамический вход, если переключается задним фронтом – снабжен инверсным динамическим входом.

Таким образом, триггер с динамическим управлением не чувствителен к изменению информационных сигналов при действии сигналов С=1 и С=0. Переключение триггера происходит по переднему или заднему фронту синхроимпульса.

Среди триггеров с динамическим управлением широкое распространение получила так называемая схема трех триггеров. Триггеры выпускаются в виде интегральных схем.

Триггеры входят в состав многих функциональных последовательных цифровых устройств, таких как регистры, счетчики, накапливающие сумматоры и т.д.