- •Полупроводниковые приборы. Классификация. Область применения.

- •Полупроводниковые диоды. Классификация. Область применения.

- •Полупроводниковые транзисторы. Классификация. Область применения.

- •Полупроводниковые резисторы. Классификация. Область применения.

- •Фотоэлектрические приборы. Классификация. Область применения.

- •Аналоговые усилители. Классификация. Основные характеристики и параметры.

- •Избирательные усилители. Усилители постоянного тока. Усилители мощности. Область применения.

- •Стабилизаторы напряжения. Классификация. Параметры. Область применения.

- •Логические операции. Схемная реализация.

- •Цифровые устройства. Классификация. Комбинационные цу. Дешифраторы. Шифраторы, мультиплексоры, демультиплексоры.

- •Комбинационные сумматоры.

- •Триггера. Классификация. Область применения.

- •Регистры и счетчики. Классификация. Схемы. Область применения.

- •Цифро-аналоговые преобразователи. Назначение. Принцип работы. Матрица r-2r. Область применения.

- •Аналого-цифровые преобразователи. Классификация. Область применения. Параллельные ацп. Ацп поразрядного взвешивания.

- •Интегрирующие ацп. Ацп двойного интегрирования

- •Таймеры. Классификация. Область применения.

- •Источники вторичного напряжения. Структурные схемы. Выпрямители и фильтры.

- •Транзисторный усилительный каскад с общим эммитером

- •Дискретные цифровые сар: математическое описание, z передаточные функции.

- •Анализ дискретных сар

- •23. Логарифмические частотные характеристики сар.

- •24. Переходные функции и переходные характеристики сар. Реакция сар на произвольный входной сигнал

- •25.Типовые звенья сар и их частотные и временные характеристики Апериодическое звено

- •Интегрирующее звено

- •26. Устойчивость линейных сар: определение, теоремы Ляпунова, алгебраический критерий устойчивости Гурвица.

- •27. Частотные критерии устойчивости линейных сар

- •28. Анализ качества линейных сар.

- •29. Синтез корректирующих устройств линейных сар.

- •30. Анализ нелинейных сар.

- •31. Показатели качества эс

- •33. Себестоимость и уровень качества эс

- •34. Корреляционная связь показателей эc Диаграмма разброса (поле корреляции)

- •35. Метод расслаивания чм.

- •36. Метод «авс-анализ»

- •Складские запасы изделий

- •37. Виды статистического контроля эс

- •38. Количественные показатели надежности эс

- •39. Последовательная модель надежности

- •40. Параллельная модель надежности эс

- •41. Основные этапы автоматизации: их характеристики и особенности.

- •42. Назначение, классификация и области применения роботов

- •43. Манипуляционные роботы: типы, характеристики, применение

- •44. Структура механизмов манипуляц-х роботов и характеристики их геом. Свойств

- •45. Приводы манипуляторов и роботов: классификация, особенности применения

- •46. Конструкции схватов промышленных роботов(пр), особенности применения

- •47. Проектирование архитектуры интегрированной компьютерной системы управления (иксу)

- •48. Описание технологического процесса как объекта автоматизированного управления

- •49. Описание производственного процесса как объекта автоматизированного управления: реализации арм различных уровней

- •50. Выбор датчиков тп:типы измерительных устройств, подключение

- •51. Теорема Котельникова (теорема отсчетов). Квазидетерминированные сигналы.

- •52. Преобразование измерительных сигналов. Виды модуляций

- •53. Цифровые частотомеры

- •54. Цифровые фазометры

- •55. Цифровые вольтметры (цв) временного преобразования

- •56. Микропроцессорные цифровые измерительные приборы.

- •57. Резистивные датчики (реостатные, тензорезисторы)

- •58. Электромагнитные датчики (индуктивные, трансформаторные, магнитоупруние).

- •59. Пьезоэлектрические датчики

- •60. Тепловые датчики (термопары, термометры сопротивления).

- •61. Организация и этапы разработки конструкторских документов.

- •62. Виды кд.

- •63. Стандартизация и бнк.

- •64. Виды и типы схем, обозначения по ескд.

- •65. Методы компоновки конструкции эвс.

- •66. Климатические зоны и категории исполнения.

- •67. Способы защиты эвс от влаги.

- •Примеры конструкций средств защиты

- •68. Защита эвс от механических воздействий.

- •Рекомендации по защите рэа от вибрационных воздействий

- •69. Способы обеспечения теплового режима эвс.

- •70. Электромагнитные воздействия. Виды экранов.

- •Экран из ферромагнитного материала с большой магнитной проницаемостью (метод шунтирования экраном).

- •71. Виды линий связи.

- •72. Особенности конструирования бортовых эвс.

- •73. Особенности конструкций персональных эвм.

- •74. Унификация. Разновидности стандартизации.

- •Разновидности стандартизации

- •75. Требования к трассировке пп

- •76. Электромонтажные провода. Припои и флюсы.

- •77. Волоконно-оптические линии связи (волс). Примеры использования.

- •78. Эргономические требования к пультам и органам управления и сигнализации

- •79. Эргономика конструирования лицевой панели прибора.

- •80. Защита эс от воздействия радиации.

- •81. Производственный и технологический процесс и их составляющие

- •82. Исходные данные для разработки технологических процессов. Основные этапы разработки единичного технологического процесса.

- •83. Требования к оформлению технологической документации. Примеры записи технологических операций.

- •84. Основные методы изготовления печатных плат и их особенности

- •85. Конструктивно-технологические разновидности радиоэлектронных узлов и их сопоставительный анализ.

- •86. Основные технологические операции при изготовлении радиоэлектронных узлов с монтажом на поверхность

- •87. Нанесение паяльной пасты и клея и используемое при этом оборудование

- •88. Принципы организации работы сборочных автоматов

- •89. Особенности выполнения пайки при изготовлении электронных модулей ( пайка оплавлением, волной припоя, селективная пайка).

- •90. Особенности выполнения ремонтных работ: демонтаж и монтаж компонентов.

- •91. Материалы, используемые в технологии монтажа на поверхность.

- •92 Виды соединительных операций при сборке.

- •94. Соединение пайкой: разновидности, области применения, примеры выполнения паяных соединений.

- •95. Разработка схемы сборки изделий.

- •96. Нормирование затрат времени при проектировании технологических процессов (штучное и подготовительно-заключительное время, определение такта и ритма выпуска изделий).

- •97. Изготовление деталей эс методом литья

- •98. Разделительные и формообразующие операции холодной штамповки

- •99. Общая характеристика методов формообразования материалов и деталей при производстве эс

- •100. Изготовление электронных модулей по технологии внутреннего монтажа.

- •101. Приведите структуру контроллера (микроЭвм) с раздельными шинами адрес/данные и следующим составом:

- •102. Укажите место на структурной схеме эвм различных интерфейсов. Как объединять эвм в систему? Какие условия следует выполнить при передаче данных? Обоснуйте.

- •103.Расставьте по убыванию значимости параметры эвм по критерию производительности. Охарактеризуйте эти параметры.

- •105. Сопоставьте принципы печати лазерного и струйного принтеров, опишите и сравните их.

- •107. Выберите способ обмена данными между процессором и внешним устройством. Обоснуйте выбор. Напишите процедуру ввода или вывода данных в память эвм в мнемонике команд (уровень ассемблера).

- •108. Приведите основные архитектурные варианта построения операционных систем. Поясните понятие «виртуальная машина»

- •110. Спроектировать устройство микропрограммного управления автономного типа. Источник управляющих кодов – счетчик микрокоманд, число состояний счетчика – 32. Разрядность регистра микрокоманд – 24

- •112. Прерывания как способ изменения адреса в управляющей команде. Привести пример системы прерывания. Описать процедуру опознавания запроса на прерывание с маскированием

- •С линией запроса

- •113. Системы памяти эвм. Назначение каждого типа элементов памяти и место его в иерархии. Что дает для характеристик эвм каждый тип элементов памяти

- •114. Память программ. Виды носителей. Жесткие диски и их твердотельные аналоги

- •115. Компиляторы. Назначение компиляторов, их виды. Последовательность процедуры компиляции

- •116. Контроль информации при последовательной передаче двоичного кода. Методы контроля. Контроль передачи информации при обмене словами (байтами). Методы.

- •117. Приведите основные структуры объединения процессоров в многопроцессорных системах. В чем суть ограничений архитектуры Фон-Неймана

- •118. Сравните структуры двух мпк, имеющих организацию smp и mpp. Приведите их структурные схемы

- •119. Сравните характеристики двух последовательных интерфейсов rs-232с и usb. Приведите структурную организацию интерфейсов и формат передаваемых данных

- •121. Основные понятия процесса проектирования систем управления. Цель процесса проектирования.

- •122. Системный подход к проектированию.

- •123. Структура процесса автоматизированного проектирования

- •124. Основные типы автоматизированных систем, разновидности сапр.

- •Структура сапр

- •125. Стадии проектирования автоматизированных систем и аспекты их описания.

- •126. Особенности проектирования автоматизированных систем.

- •127. Понятие о cals-технологиях.

- •128. Открытые системы.

- •129. Техническое обеспечение систем автоматизированного проектирования

- •130. Типы сетей, методы доступа в сетях, протоколы и стеки протоколов в вычислительных сетях

- •Стеки протоколов и типы сетей в ас

- •131. Сапр систем управления

- •132. Автоматизация управления предприятием, логистические системы.

- •133. Асутп, автоматизированные системы делопроизводства.

- •Автоматизированные системы делопроизводства

- •134. Математическое обеспечение анализа проектных решений.

- •135. Компоненты математического обеспечения, структура вычислительного процесса анализа.

- •136. Математические модели в процедурах анализа на макроуровне

- •137. Математическое обеспечение анализа на микроуровне

- •138. Математическое обеспечение анализа на функционально-логическом уровне

- •139. Математическое обеспечение на системном уровне

- •140. Математическое обеспечение подсистем машинной графики и геометрического моделирования.

- •141. Схемы мультивибратора на транзисторах и оу.

- •142. Схема одновибратора на транзисторах.

- •144. Повторитель на оу

- •145. Двухтактный трансформаторный усилитель мощности, работающий в режиме ав.

- •150. Генератор гармонических колебаний на транзисторах.

- •151. Архитектурные принципы Фон-Неймана. Ограничения.

- •152. Основные понятия информационно-вычислительных систем, классификация по критерию потоков информации

- •153. Совмещение операций и многопрограммная работа. Режим работы в реальном времени

- •154.Типы структур многопроцессорных вс. Параллельные эвм, классификация. Три архитектурных класса машин

- •Классификация по программной организации

- •Классификация по архитектуре

- •155. Принципы ввода-вывода информации в пэвм. Роль и структура контроллера ввода информации

- •Принцип ввода-вывода информации в пэвм. Роль и структура контроллера ввода информации

- •156. Программная реализация ввода чисел с клавиатуры. Привести алгоритм ввода двухразрядного числа с клавиатуры для его суммирования с другими числами

- •157. Вывод и.На дисплей.Принципы отображения информации на экране дисплея. Lcd-дисплеи

- •158. Процедура вывода символьной информации на дискретные индикаторы.

- •159. Загрузчики. Процедура загрузки. Статистические и динамические загрузки.

- •160. Управление реальной памятью. Виртуальная память. Таблица соответствия адресов

118. Сравните структуры двух мпк, имеющих организацию smp и mpp. Приведите их структурные схемы

Вариации в структуре вычислителя возможны в организации ША и ШД. Так, например ША формируется из старших разрядов по ША и младших по ШД. Чтобы адрес сохранялся, цикл процессора введен регистр адреса, содержимое которого фиксируется по сигналу синхронизации. ШД сформирована через буфер данных (ВА) двунаправлена. Управление буфером данных – сигналом запись/чтение процессора. Схема ОЗУ ПЗУ порт I/Out выбираются адресными дешифраторами, поэтому при проектировании структуры все адресное пространство делят на области. Как правило самая большая – ОЗУ. Например: она занимает32К. Это половина. Рекомендуют размещать ее в верхней части ОЗУ – 8К, чтобы разделить дешифратором, необходимо определить число частей. В простейшем варианте всю область памяти делим на 4 равных части: 16К-ПЗУ, 16К- ПОРТ, 32К – ОЗУ. С этой целью используем дешифратор 2 в 4. На вход подаем А15,А14 – два старших разряда.

А14 |

А15 |

|

0 |

0 |

ПЗУ |

0 |

1 |

Порт в/выв |

1 |

0 |

ОЗУ |

1 |

1 |

ОЗУ |

С соответствующих выходов дешифратора согласно таблице подаем сигналы на входы разрешение выборки кристалла. Для ОЗУ необходима схема И объединяющая два вы хода дешифратора. Управляющие сигналы r/w берутся с выхода процессора либо с системного контроллера и подаются на соответствующие входы блоков. Возможна ситуация, когда объем ОЗУ ПЗУ превышает 64К. в этом случае рассматривается два адресных пространства: первое для ОЗУ, второе – ПЗУ, порты и тд. Переключение адресных пространств – сигналами контроллера – фаза выборки, чтение/запись и т.д.

В реальных схемах число порто I/Out может быть значительно, поэтому число областей в адресном пространстве 6-10.поэтому можно применить двойной дешифратор. Первый “грубый”, у которого один выход обращения к ВУ, второй включается этим выходом и обеспечивает разделение с помощью младших разрядов адреса.

Для ОМП с общей шиной (К1801) необходимо сформировать адресные дешифраторы и адресные регистры на каждом функциональном блоке. Каждый блок имеет на входе адресный регистр с дешифрацией. Если адресное пространство его в регистр записывается – адрес и блок становится активными. Все остальные блоки не выбраны. Однокристальные микроЭВМ имеют в своем составе порты и некоторую память, поэтому структура контроллера отличается лишь блоком процессора. Способы подключения ВУ аналогичны. Контроллер на основе ОМП используют в промышленных системах управления, отображения информации ввода вывода. Их относительная черта – невысокая производительность, при несложных аппаратных затратах.

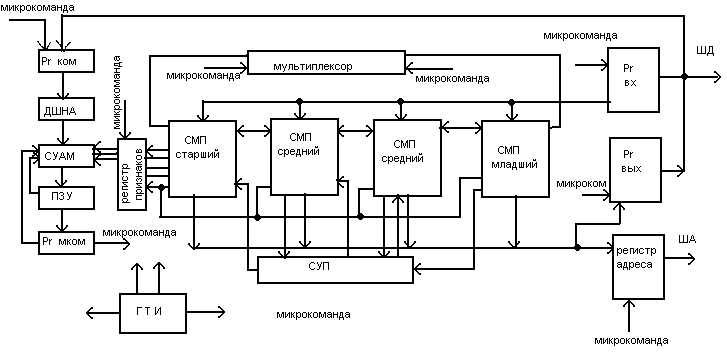

(2) Основное отличие этой структуры в том, что процессор имеет более сложное построение чем, в первом варианте. Это связано с тем, что необходимо обеспечить работоспособность секций и связь их между собой. Кроме этого блок микропрограммного управления также имеет немалые аппаратные средства.

Четыре секции включены параллельно: младшая, старшая – по краям, на входе каждой секции поступает часть разряда, например 4. Выходные разряды секций также компенсируются, обеспечивая выходную разрядность равную входной. ШД образуется двумя регистрами входом и выходом. Причем, регистр входа должен третье состояние. ША формируется отдельным регистром, при разрядность ее зависит от задания. Если разрядность ША<ШД используются младшие выходные разряды секции, если разрядность ША>ШД – он выводится из внутренних регистров секций за два такта, младшие и старшие части. В секциях нет отдельно выделенных регистров адреса, поэтому в качестве него применяют одну из РОН секций. Между собою секции объединяются через выходы сдвиговых разрядов. Краткие выводы этих разрядов коммутируются через мультиплексор. С помощью отдельных разрядов микрокоманды мультиплексора настаиваются на левые или правые сдвиги. Для организации ускоренного переноса используют блок ускоренного переноса (СУП). На ее выходы подключают сигналы распространения и генерации переноса. Выходы СУП – на входной перенос следующей секции. Одна такая схема работает с 4 секциями. Со старшей секцией снимают признаки, причем, признак Z объединяется со всеми секциями. Признаки хранятся в регистре. Блок микропрограммного управления имеет типовую структуру. Управляющая часть – форматы микрокоманд распределяется между регистрами, мультиплексорными ключами, обеспечивая синхронизацию во времени. Непосредственно микрокоманды поступают на каждую секции параллельно. Одни и те же разряды на каждую секцию. Это схема позволяет выполнять операции как над одинарной длины так и над операндами.

Процессорный блок на СМП отличается большей аппаратной сложностью, но позволяет гибко изменять разрядность адреса и данных процессора.