- •Схемотехника

- •Предисловие

- •Часть первая

- •1.2. Классификация первичных преобразователей

- •Фотоэлектрические первичные преобразователи перемещений

- •2.1. Общие сведения

- •2.3.2. Растровые интерполяторы

- •2.3.3. Одноканальные растровые интерполяторы

- •2.4. Фпп считывания

- •2.4.1. Общие принципы построения

- •2.4.2. Фпп на основе многоэлементных фотоприемников

- •2.4.3. Волоконно-оптические функциональные преобразователи

- •Электромагнитные первичные преобразователи перемещений

- •3.1. Принципы построения

- •3.3. Эпп электромашинного типа

- •3.5. Токовихревые эпп

- •Емкостные и магнитострикционные первичные преобразователи перемещении

- •4.1. Емкостные преобразователи перемещении

- •4.2. Магнитострикционные преобразователи перемещения

- •Часть вторая

- •Преобразователи фаза-код прямого измерения

- •5.1. Классификация фазовых цпп

- •5.2.2. Пфк с постоянным временем измерения

- •5.3. Пфк с преобразованием частоты

- •5.4. Пфк с промежуточным преобразованием

- •5.4.1. Пфк с промежуточным преобразованием в напряжение

- •5.4.2. Пфк с промежуточным преобразованием в частоту

- •6.1. Общие сведения

- •6.2. Пфк с электромеханическими фсс

- •6.3. Пфк на основе цифровых фсс

- •6.4. Функциональные фазовые преобразователи

- •7.1. Коммутационные пфк

- •7.2. Многоотсчетные пфк

- •7,2.1. Общие сведения

- •7.2.2. Пфк с использованием датчиков грубого отсчета

- •7.2.3. Пфк с компенсацией погрешностей первичного преобразователя

- •7.2.4. Многоотсчетные пфк накапливающею типа

- •Фазовые преобразователи скорости и ускорения

- •8.1. Способы формирования скоростного сигнала

- •8.3. Многофункциональные фазовые преобразователи

- •8.4. Совмещенный цифровой преобразователь угла, скорости и ускорения

- •Часть третья амплитудные цифровые преобразователи перемещений

- •9.1. Формат сквт

- •9.2. Способы преобразования угла в код, основанные на интегрировании выходных напряжении сквт

- •9.3. Преобразователь на основе генератора гармонических сигналов

- •9.3.1. Особенности построения

- •9.3.2. Способы повышения быстродействия

- •9.3.3. Схемные методы повышения точности

- •9.3.4. Снижение аддитивной составляющей погрешности преобразования

- •Цпп с функциональными генераторами

- •10.2. Сравнительная оценка цпп на основе функциональных генераторов

- •10.3. Устройства выборки и хранения

- •10.4. Функциональные генераторы

- •11.1. Основные структуры построения

- •11.2. Совершенствование схемных построения

- •11.3. Снижение методической погрешности. Введение коррекции

- •11,4. Повышение быстродействия

- •12.1. Преобразователи с синусно-косинусным пзу

- •12.2. Преобразователи с тангенсным пзу

- •12.3. Преобразователи с арктангенсным пзу

- •Следящие цпп

- •13.1. Улучшение динамических показателей и компенсация погрешностей первичного преобразователя

- •13.2. Следящий цпу как замкнутая система автоматического регулирования

- •13.3 Особенности динамики следящих цпп

- •13.4. Выбор основных параметров одноотсчетного следящего преобразователя с сквт

- •14.1. Ограничения по чувствительности и точности

- •14.2. Следящий преобразователь с тангенсным фцап

- •14.3. Амплитудный цпу с переменной структурой

- •15.1. Особенности структур построения

- •15.2. Многоканальные циклические цпу с пзу

- •Часть четвертая пути совершенствования амплитудных цпп

- •Цпп с цифровыми интеграторами

- •16.1. Преобразователи с цифровыми интеграторами

- •18.2. Масштабирующие преобразователи

- •17.1. Преобразователи аргумента, синусной и косинусной функций в коды

- •17.2. Устранение методической ошибки

- •17.3. Реализация специальных преобразования

- •17.4. Функциональный преобразователь угол - код с сельсином

- •Функциональные циклические цпп на бис ацп и пзу

- •18.1. Функциональный цпу последовательного типа

- •18.2. Функциональный цпу с параллельным преобразованием

- •18.3. Функциональный последовательно-параллельный цпу

- •18.4. Совмещенный функциональный цпу

- •19.1. Преобразователь с синусно-косинусным фцап

- •19.3. Высокоточные преобразователи

- •20,1 Оценка уровня повышения разрешающей способности

- •20.2. Цпу с Синусно-косинусными и тангенсным фцап

- •20.5. Классификация амплитудных цпп

- •21.1. Методы цифровой тахометрии

- •21.2. Преобразователи скорости на основе сквт

- •21.3. Цифровой тахометр с сквт

- •22.1. Место и роль цпп в микропроцессорных системах

- •22.2. Особенности взаимодействия различны типов цпп с мп

- •22.3. Организация программной и аппаратной совместимости цпп в микропроцессорной системе

- •22.4. Алгоритмические способы коррекции цпп микроэвм

- •22.4.1. Снижение аддитивной и инструментальной составляющих погрешности

- •22.4.3. Коррекция погрешности цпп с пзу

- •Список литературы

- •Алфавитный указатель

9.3.3. Схемные методы повышения точности

Одним из эффективных путей повышения точности ЦПУ на основе генератора гармонических сигналов является совершенствование схемных построений его отдельных устройств, введение новых устройств и связей между ними. Пример такого подхода представлен в [а.с. 982049 (СССР)], где предложены новые выполнения дифференциатора, определителя квадрантов и формирователя уровня; введены блоки управления и установок. На рис. 9.11 представлена функциональная схема преобразователя.

Преобразователь

содержит СКДУ;

коммутаторы

КР1

и

КР2;

интеграторы

ИР1

и

ИР2;

компараторы

К1 и К2

инвертор

![]() генератор

импульсов ГИ;

генератор

импульсов ГИ;

дифференциатор

ДФ,

состоящий

из Д-триггера, логических элементов

И1,

И2 и

НЕ1;

определитель

квадрантов ОК,

состоящий

из сумматора по модулю 2 и

схемы НЕ2;

формирователь

уровня ФУ,

состоящий

из регистра

![]() селектора-мультиплексора

СМ

и

схем НЕЗ,

НЕ4; блок

управления БУ,

содержащий

нуль-орган

НО,

схемы

ИЗ

и

ИЛИ;

блок

установок БУС;

счетчики

С2

и

С1; регистр

селектора-мультиплексора

СМ

и

схем НЕЗ,

НЕ4; блок

управления БУ,

содержащий

нуль-орган

НО,

схемы

ИЗ

и

ИЛИ;

блок

установок БУС;

счетчики

С2

и

С1; регистр![]() и

источник опорных напряжений ИОН.

и

источник опорных напряжений ИОН.

Определитель

квадрантов ОК,

предназначен

для формирования кода квадранта,

предшествующего реальному нахождению

угла 0. Например, при нахождении

0 во втором квадранте формулируется

код первого квадранта и т. д. Регистр

![]() предназначен

для хранения кода квадранта, необходимого

для выделения

нужного фронта сигнала из выходных

сигналов компараторов K1

и

К2

при

расположении угла в в любом из четырех

квадрантов. Счетчик С1

имеет

входы параллельной записи во все

разряды, он может быть реализован,

например,

на микросхемах К133ИЕ7. Код, хранящийся

в БУС,

совместно

со

сформированным кодом квадранта

представляет собой код начала квадранта

нахождения

угла 0, уменьшенный на величину кода

компенсации задержки

предназначен

для хранения кода квадранта, необходимого

для выделения

нужного фронта сигнала из выходных

сигналов компараторов K1

и

К2

при

расположении угла в в любом из четырех

квадрантов. Счетчик С1

имеет

входы параллельной записи во все

разряды, он может быть реализован,

например,

на микросхемах К133ИЕ7. Код, хранящийся

в БУС,

совместно

со

сформированным кодом квадранта

представляет собой код начала квадранта

нахождения

угла 0, уменьшенный на величину кода

компенсации задержки![]() коммутаторов

и компараторов. Он выбирается равным

коду установки БУС

коммутаторов

и компараторов. Он выбирается равным

коду установки БУС![]()

Например, если 0 соответствует 0,3° и расположен во втором квадранте, то на параллельные входы счетчика С1 поступает код, соответствующий 89,7е.

Одновременно наличие старших разрядов в счетчике С1, куда записывается кол квадранта, предохраняет преобразователь от сбоев, выражающихся а переполнении разрядов этого счетчика, формирующих код угла внутри квадранта.

Нуль-орган НО и элемент ИЗ предназначены для формирования пачки импульсов У1, получаемых от совпадения положительных полуволн опорного напряжения ИОН с состоянием 1 первого выхода счетчика С2. Количество импульсов в пачке задается временным интервалом с помощью счетчика таким, чтобы напряжение на интеграторах в конце первого такта доходило до нужного значения при требуемой чувствительности уровня.

Работа преобразователя происходит в три такта.

В первом такте на втором выходе счетчика С1—1, на первом выходе—0. Импульсы У1 синхронно с положительными полуволнами опорного напряжения ИОН поступают на управляющие входы коммутаторов. При наличии импульса У1 напряжения, с выходов СКДУ через коммутаторы поступают на входы интеграторов и накапливаются там. В паузах между импульсами У1 на входы интеграторов ничего не поступает и они выполняют роль аналоговых запоминающих устройств. При поступлении сигнала на С2 н С/, который находится в режиме постоянного счета, С2 увеличивает свое состояние на единицу, на втором выходе счетчика появляется 0. С помощью коммутаторов прекращается подача напряжений с выходов СКДУ на интеграторы.

При

установке на первом выходе счетчика

С1

1

начинается второй такт. По

фронту сигнала У2

код

квадранта, сформированный на выходах

компаратора

К2

и

элемента НЕ2,

записывается

в

![]() и

совместно с кодом БУС

записывается

в C1.

Код

с выходов

и

совместно с кодом БУС

записывается

в C1.

Код

с выходов

![]() подготавливаетСМ

к

пропусканию положительного

фронта сигнала (при ближайшем переходе

через нуль напряжения одного

из интеграторов) на D-вход

триггера Д, который отсутствием 1 на

первом

выходе счетчика был установлен н

состояние 0. Одновременно при появлении

1 на первом выходе счетчика с помощью

коммутаторов интеграторы и инвертор

образуют замкнутую петлю — осциллятор.

При ближайшем переходе через нуль

напряжения одного из интеграторов

сигнал на выходе мультиплексора

принимает состояние 1 и триггер, который

ранее поддерживался в состоянии 0,

переходит по ближайшему фронту импульса

генератора в состояние I,

тем

самым1

разрешая запись из счетчика в регистр

кода, который накапливается

там в течение интервала осциллирования.

Отрицательный фронт импульса генератора,

пройдя через элементы ИЕ1

и

И2,

устанавливает

в 0 счетчики и тем

самым устанавливает в 0 триггер Д

(по

R-входу).

подготавливаетСМ

к

пропусканию положительного

фронта сигнала (при ближайшем переходе

через нуль напряжения одного

из интеграторов) на D-вход

триггера Д, который отсутствием 1 на

первом

выходе счетчика был установлен н

состояние 0. Одновременно при появлении

1 на первом выходе счетчика с помощью

коммутаторов интеграторы и инвертор

образуют замкнутую петлю — осциллятор.

При ближайшем переходе через нуль

напряжения одного из интеграторов

сигнал на выходе мультиплексора

принимает состояние 1 и триггер, который

ранее поддерживался в состоянии 0,

переходит по ближайшему фронту импульса

генератора в состояние I,

тем

самым1

разрешая запись из счетчика в регистр

кода, который накапливается

там в течение интервала осциллирования.

Отрицательный фронт импульса генератора,

пройдя через элементы ИЕ1

и

И2,

устанавливает

в 0 счетчики и тем

самым устанавливает в 0 триггер Д

(по

R-входу).

Начинается третий такт. На третьем такте на выходе элемента ИЛИ появляется 1 и интеграторы начинают обнуляться. Третий такт продолжается до тех пор, пока сигнал с выхода счетчика не увеличит на единицу состояние второго счетчика, т. е. начнется снова первый такт.

В результате происходит увеличение точности преобразователя за счет компенсации погрешности, вызванной задержкой аналоговых коммутаторов и компараторов, и устранения возможности сбоя при переполнении счетчика при углах, близких к 90, 180, 270, 360°, вследствие изменения постоянных времени интеграторов.

Схемные методы повышения показателей ЦПУ могут предусматривать введение коррекции результатов преобразования от изменения параметров интеграторов. Их применение позволяет автоматизировать и взаимную балан-сировку интеграторов [а. с. 972541 (CCCP)].

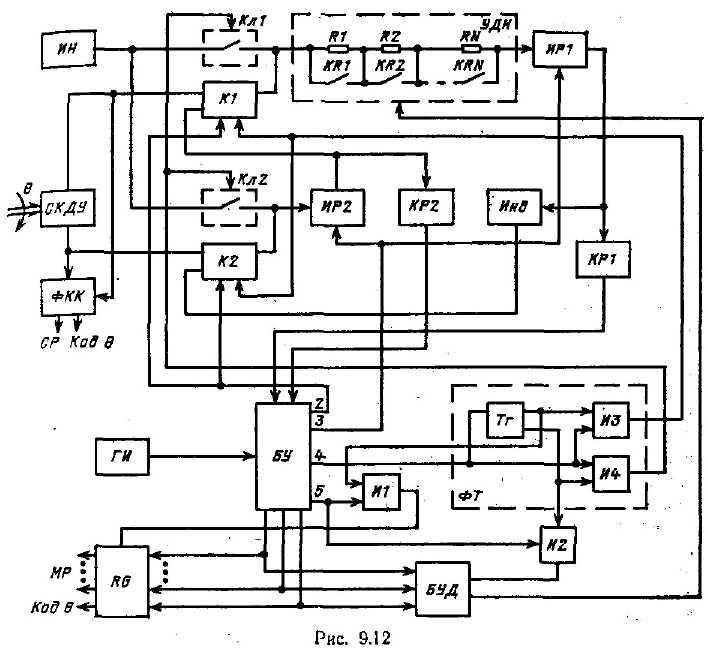

Схема

ЦПУ с автоматической коррекцией

представлена на рис. 9.12. Преобразователь

состоит из СКДУ,

формирователя

кода квадранта ФКК,

компараторов

KP1

и

КР2,

управляемого

делителя напряжения УДН,

интеграторов

ИР1

и

ИР2,

коммутаторов

K1,

К2,

![]() блока

управления

БУ,

генератора

импульсов ГИ,

регистра

блока

управления

БУ,

генератора

импульсов ГИ,

регистра

![]() ,

блока управления делителемБУД,

формирователя

тактов ФТ,

ключей

Кл1

и

Кл2,

источника

напряжения ИН,

логических

схем И1,

И2 и

инвертора Ннв.

,

блока управления делителемБУД,

формирователя

тактов ФТ,

ключей

Кл1

и

Кл2,

источника

напряжения ИН,

логических

схем И1,

И2 и

инвертора Ннв.

Для автоматического поддержания равенства (9.21), при котором Ф эквивалентно 8, в преобразователе на входе одного из интеграторов установлен УДН [59] и введен дополнительный режим — коррекция. В этом режиме на входы отсчетной части подается одно напряжение, что позволяет имитиро-вать задание 0°, 45° или 225°. Полученный после преобразования код корректируют согласно выражению (9.20) и сравнивают с расчетным кодом 45° или 225°. По полученному отклонению корректируют код, хранящийся в УДН До установления равенства (9.21).

Преобразователь работает следующим образом.

Датчик формирует сигналы, пропорциональные синусу и косинусу угла поворота его вала. По сигналу с четвертого выхода БУ триггер устанавливается в 0, на выходе элемента И4 формируется единичный уровень, по кото-

рому замыкаются Кл1 и Кл2. Напряжение ИИ через Кл1 и УДН поступает на вход ИР1, а через Кл2 — на вход ИР2. По прошествии мекоторого времени интегрирования появляется сигнал на втором выходе БУ, а с четвертого выхода снимается. При этом выход ИР2 через К1 подключается к входу делителя, а выход инвертора через К2 подключается к входу ИР2. Начинается процесс взаимного интегрирования напряжений ИР1 и ИР2 до тех hop, пока выходное напряжение одного из интеграторов не станет нулевым, что фиксируется КР1 или КР2.

Временной интервал взаимного интегрирования измеряется путем запол- нення его импульсами генератора и подсчёта в БУ. Сигнал окончания интегри- ррвания с пятого выхода БУ Через открытый элемент Ц2 проходит в БУД я переписывает в этот блок полученный код временного интервала с первых выходов БУ. В зависимости от полученного кода коэффициент передача дели- теля устанавливается таким, чтобы постоянные интегрирования ИР1 и ИР2 с учетом коэффициента передачи инвертора были равны. После сигнала с пятого выхода БУ формируется сигнал с третьего выхода этого блока, по которому ИР1 л ИР2 устанавливаются в 0.

Далее

вновь появляется сигнал на четвертом

выходе БУ,

по

которому![]() устанавливается

в 1, на выходе элемента ИЗ

формируется

единичный уровень, а

выходы датчика подключаются соответственно

к УДН

и

ИР2.

Начинается

интегрирование

выходных напряжений датчика ИР1

и

ИР2.

По

прошествии времени

интегрирования появляется сигнал на

втором выходе БУ,

по

которому входы УДИ

и

ИР2

отключаются

от выходов датчика и подключаются

соответственно

к выходу инвертора. Начивается

вторично-процесс взаимного интегрирования

до момента срабатывания KP1

или

КР2,

Код

временного интервала взаимного

интегрирования переписывается выходным

сигналом элемента И1 в

устанавливается

в 1, на выходе элемента ИЗ

формируется

единичный уровень, а

выходы датчика подключаются соответственно

к УДН

и

ИР2.

Начинается

интегрирование

выходных напряжений датчика ИР1

и

ИР2.

По

прошествии времени

интегрирования появляется сигнал на

втором выходе БУ,

по

которому входы УДИ

и

ИР2

отключаются

от выходов датчика и подключаются

соответственно

к выходу инвертора. Начивается

вторично-процесс взаимного интегрирования

до момента срабатывания KP1

или

КР2,

Код

временного интервала взаимного

интегрирования переписывается выходным

сигналом элемента И1 в

![]() После

этого сигнал с третьего выхода БУ

устанавливает

ИР1

и

ИР2

После

этого сигнал с третьего выхода БУ

устанавливает

ИР1

и

ИР2

в 0. Цикл

преобразования заканчивается. Код угла

поворота находится в![]()

Таким образом, в начале каждого. цикла преобразования производится автоматическое уравнивание постоянных интегрирования, что повышает точность ЦПУ при изменении параметров ИР и инвертора. Выполняя по программе через промежутки времени, определяемые ожидаемой динамикой изменения постоянных времени ИР, цикл коррекции, получаем ЦПУ, выходной код которого не зависит от изменения постоянных интеграторов и который не требует трудоемкой операции настройки.