- •Схемотехника

- •Предисловие

- •Часть первая

- •1.2. Классификация первичных преобразователей

- •Фотоэлектрические первичные преобразователи перемещений

- •2.1. Общие сведения

- •2.3.2. Растровые интерполяторы

- •2.3.3. Одноканальные растровые интерполяторы

- •2.4. Фпп считывания

- •2.4.1. Общие принципы построения

- •2.4.2. Фпп на основе многоэлементных фотоприемников

- •2.4.3. Волоконно-оптические функциональные преобразователи

- •Электромагнитные первичные преобразователи перемещений

- •3.1. Принципы построения

- •3.3. Эпп электромашинного типа

- •3.5. Токовихревые эпп

- •Емкостные и магнитострикционные первичные преобразователи перемещении

- •4.1. Емкостные преобразователи перемещении

- •4.2. Магнитострикционные преобразователи перемещения

- •Часть вторая

- •Преобразователи фаза-код прямого измерения

- •5.1. Классификация фазовых цпп

- •5.2.2. Пфк с постоянным временем измерения

- •5.3. Пфк с преобразованием частоты

- •5.4. Пфк с промежуточным преобразованием

- •5.4.1. Пфк с промежуточным преобразованием в напряжение

- •5.4.2. Пфк с промежуточным преобразованием в частоту

- •6.1. Общие сведения

- •6.2. Пфк с электромеханическими фсс

- •6.3. Пфк на основе цифровых фсс

- •6.4. Функциональные фазовые преобразователи

- •7.1. Коммутационные пфк

- •7.2. Многоотсчетные пфк

- •7,2.1. Общие сведения

- •7.2.2. Пфк с использованием датчиков грубого отсчета

- •7.2.3. Пфк с компенсацией погрешностей первичного преобразователя

- •7.2.4. Многоотсчетные пфк накапливающею типа

- •Фазовые преобразователи скорости и ускорения

- •8.1. Способы формирования скоростного сигнала

- •8.3. Многофункциональные фазовые преобразователи

- •8.4. Совмещенный цифровой преобразователь угла, скорости и ускорения

- •Часть третья амплитудные цифровые преобразователи перемещений

- •9.1. Формат сквт

- •9.2. Способы преобразования угла в код, основанные на интегрировании выходных напряжении сквт

- •9.3. Преобразователь на основе генератора гармонических сигналов

- •9.3.1. Особенности построения

- •9.3.2. Способы повышения быстродействия

- •9.3.3. Схемные методы повышения точности

- •9.3.4. Снижение аддитивной составляющей погрешности преобразования

- •Цпп с функциональными генераторами

- •10.2. Сравнительная оценка цпп на основе функциональных генераторов

- •10.3. Устройства выборки и хранения

- •10.4. Функциональные генераторы

- •11.1. Основные структуры построения

- •11.2. Совершенствование схемных построения

- •11.3. Снижение методической погрешности. Введение коррекции

- •11,4. Повышение быстродействия

- •12.1. Преобразователи с синусно-косинусным пзу

- •12.2. Преобразователи с тангенсным пзу

- •12.3. Преобразователи с арктангенсным пзу

- •Следящие цпп

- •13.1. Улучшение динамических показателей и компенсация погрешностей первичного преобразователя

- •13.2. Следящий цпу как замкнутая система автоматического регулирования

- •13.3 Особенности динамики следящих цпп

- •13.4. Выбор основных параметров одноотсчетного следящего преобразователя с сквт

- •14.1. Ограничения по чувствительности и точности

- •14.2. Следящий преобразователь с тангенсным фцап

- •14.3. Амплитудный цпу с переменной структурой

- •15.1. Особенности структур построения

- •15.2. Многоканальные циклические цпу с пзу

- •Часть четвертая пути совершенствования амплитудных цпп

- •Цпп с цифровыми интеграторами

- •16.1. Преобразователи с цифровыми интеграторами

- •18.2. Масштабирующие преобразователи

- •17.1. Преобразователи аргумента, синусной и косинусной функций в коды

- •17.2. Устранение методической ошибки

- •17.3. Реализация специальных преобразования

- •17.4. Функциональный преобразователь угол - код с сельсином

- •Функциональные циклические цпп на бис ацп и пзу

- •18.1. Функциональный цпу последовательного типа

- •18.2. Функциональный цпу с параллельным преобразованием

- •18.3. Функциональный последовательно-параллельный цпу

- •18.4. Совмещенный функциональный цпу

- •19.1. Преобразователь с синусно-косинусным фцап

- •19.3. Высокоточные преобразователи

- •20,1 Оценка уровня повышения разрешающей способности

- •20.2. Цпу с Синусно-косинусными и тангенсным фцап

- •20.5. Классификация амплитудных цпп

- •21.1. Методы цифровой тахометрии

- •21.2. Преобразователи скорости на основе сквт

- •21.3. Цифровой тахометр с сквт

- •22.1. Место и роль цпп в микропроцессорных системах

- •22.2. Особенности взаимодействия различны типов цпп с мп

- •22.3. Организация программной и аппаратной совместимости цпп в микропроцессорной системе

- •22.4. Алгоритмические способы коррекции цпп микроэвм

- •22.4.1. Снижение аддитивной и инструментальной составляющих погрешности

- •22.4.3. Коррекция погрешности цпп с пзу

- •Список литературы

- •Алфавитный указатель

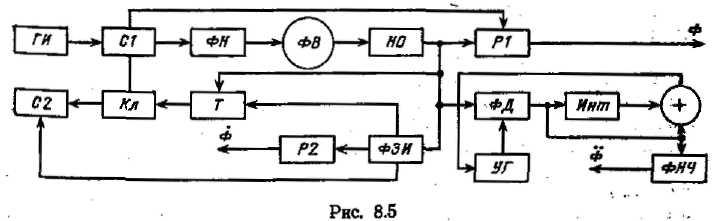

8.3. Многофункциональные фазовые преобразователи

Дальнейшее совершенствование преобразователей угла и скорости предусматривает повышение точности путем автоматизации стабильного выбора диапазона измерения частоты вращения и введения канала измерения ускорения.

Один из вариантов построения преобразователя углового положения, скорости и ускорения вала приведен на рис. 8.5 [а. с 994990 (СССР)]. Преобразователь работает следующим образом.

Первый счетчик С1 выполняет функцию делителя ГИ. Формирователь импульсов ФИ вырабатывает из выходных периодических сигналов счетчика С1

опорные напряжения фазовращателя ФВ. Нуль-орган НО формирует из выходных синусоидальных сигналов ФВ прямоугольные периодические сигналы, по фронту которых осуществляется запись кода С1 в регистр Р1, т. е. фиксируется цифровой эквивалент Ф текущего углового положения вала в.

Второй счетчик С2,

имеющий разрядность,

равную разрядности С1,

плюс дополнительный

знаковый разряд, вместе с ключом Кл,

дополнительным

триггером

Т,

формирователем

задержанных импульсов ФЗИ

и

регистром Р2

образуют

блок вычисления частоты вращения,

причем вычисление кода скорости заменено

вычислением кода приращения

![]() периода

Т

выходного

сигнала фазовращателя

по отношению к периоду

периода

Т

выходного

сигнала фазовращателя

по отношению к периоду![]() опорного

сигналаФВ.

опорного

сигналаФВ.

По

фронту выходного сигнала нуль-органа

НО

переходит

в нулевое состояние

дополнительный триггер Т

и

одновременно запускается ФЗИ.

Сигнал

с выхода

триггера Т,

воздействуя

на управляющий вход ключа К.л,

прекращает

поступление

импульсов от ГИ

на

счетный вход С2.

Через

время, достаточное для

переноса в С2,

на

первом выходе ФЗИ

вырабатывается

импульс, который поступает

на вход разрешения записи регистра Р2

и

осуществляет запись кода ![]() счетчика

С2

в

этот регистр.

счетчика

С2

в

этот регистр.

Импульс

со второго выхода ФЗИ,

воздействуя

на входы предустановки C2,

осуществляет

запись в этот счетчик кода, соответствующего

промежутку времени между появлением

импульсов на первом и третьем выходах

формирователя

ФЗИ.

Импульс

с третьего выхода ФЗИ

переводит

в единичное состояние триггер

Т,

в результате

чего будет открыт ключ Кл

и

сигналы от ГИ

вновь

поступят

на вход С2.

Поскольку

коэффициенты пересчета счетчиков

равны, в конце

каждого периода выходного сигнала НО

в

регистре Р2

будет

фиксирован либо

прямой код

![]() если

если

![]() ,

либо дополнительный код

,

либо дополнительный код

![]() если

если![]()

Цепь

фазовой автоподстройки частоты,

содержащая фазовый детектор ФД,

интегратор![]() суммирующий

элемент и управляемый генератор УГ,

совместно

с

фильтром нижних частот ФНЧ

образуют

блок вычисления ускорения. На первый

вход ФД

поступают

сигналы с выхода HV.,

имеющие

частоту

суммирующий

элемент и управляемый генератор УГ,

совместно

с

фильтром нижних частот ФНЧ

образуют

блок вычисления ускорения. На первый

вход ФД

поступают

сигналы с выхода HV.,

имеющие

частоту![]() где

где

![]() —частота

вращения вала фазовращателя;

—частота

вращения вала фазовращателя;![]() —частота

опорного сигнала

фазовращателя.

—частота

опорного сигнала

фазовращателя.

Второй'

вход- ФД

соединен

с выходом генератора, частота которого

равна

![]() при

нулевом значении напряжения на

управляющем входе, фазовый детектор

ФД

преобразует

разность фаз сигналов на его входах в

пропорциональное этой разности

значение напряжения на его выходе.

Выходной сигнал ФД

после

интегрирования

в

при

нулевом значении напряжения на

управляющем входе, фазовый детектор

ФД

преобразует

разность фаз сигналов на его входах в

пропорциональное этой разности

значение напряжения на его выходе.

Выходной сигнал ФД

после

интегрирования

в

![]() воздействует

на управляющий вход УГ, удерживая

разность

фаз сигналов на входах ФД

на

уровне, близком к нулевому. Следовательно,

и частота генератора УГ

с

некоторым рассогласованием равна

выходной частоте

нуль-органа НО.

воздействует

на управляющий вход УГ, удерживая

разность

фаз сигналов на входах ФД

на

уровне, близком к нулевому. Следовательно,

и частота генератора УГ

с

некоторым рассогласованием равна

выходной частоте

нуль-органа НО.

Экспериментально выяснено, что дополнительная изодромная связь с выхода детектора ФД на вход генератора УГ уменьшает рассогласование частот и увеличивает устойчивость цепи фазовой автоподстройки.

Генератор

УГ

имеет

линейную зависимость выходной частоты

от управляющего

напряжения. При изменении частоты

вращения одновременно пропорционально

изменяются частота УГ а выходное

напряжение

![]() Следовательно,

входное

напряжение интегратора, равное

производной от выходного, равно с

некоторым

коэффициентом пропорциональности

значению углового ускорения. На

вход

Следовательно,

входное

напряжение интегратора, равное

производной от выходного, равно с

некоторым

коэффициентом пропорциональности

значению углового ускорения. На

вход

![]() поступают

сигналы с выходаФД,

в которых

кроме низкочастотной

составляющей, пропорциональной ускорению

вращения, присутствует высокочастотная

составляющая с частотой входного

сигнала. Фильтр нижних частот ФНЧ

выделяет

высокочастотную составляющую входного

сигнала

поступают

сигналы с выходаФД,

в которых

кроме низкочастотной

составляющей, пропорциональной ускорению

вращения, присутствует высокочастотная

составляющая с частотой входного

сигнала. Фильтр нижних частот ФНЧ

выделяет

высокочастотную составляющую входного

сигнала

![]() т.

е. на

его выходе образуется аналоговый

сигнал, пропорциональный ускорению

вращения.

Постоянная интегрирования выбирается

исходя как из диапазона измерения

ускорения вращения вала, так н из

требований к точности измерения.

т.

е. на

его выходе образуется аналоговый

сигнал, пропорциональный ускорению

вращения.

Постоянная интегрирования выбирается

исходя как из диапазона измерения

ускорения вращения вала, так н из

требований к точности измерения.

Недостатком

такого построения преобразователя

является значительная погрешность

измерения низких скоростей и ускорений,

обусловленная малым относительным

изменением частоты выходных сигналов

ФВ,

которое

равно алгебраической

сумме опорной частоты фазовращателя![]() и

частоты вращения вала

и

частоты вращения вала![]()

Погрешность

измерения низких скоростей в ускорений

может быть уменьшена

путем непосредственного использования

в каналах измерения скорости и ускорения

сигналов дополнительного фазовращателя

с большим коэффициентом электронной

редукций

![]() у

которого выходная частотаF

выражается

соотношением

у

которого выходная частотаF

выражается

соотношением

![]()

Однако использование в составе преобразователя двух ФВ существенно усложнит его конструкцию и увеличит стоимость. Это приводит к необходимости дальнейшего совершенствования отсчетной части преобразователя.

На рис. 8.6 представлена функциональная схема усовершенствованного варианта преобразователя углового положения, скорости и ускорения вращения вала в их цифровые эквиваленты соответственно Ф, Ф и Ф [а. с. 1101740 (СССР)]. Схема работает следующим образом.

Счетчик

С1

выполняет

функцию делителя частоты![]() на

коэффициент

на

коэффициент![]() так,

что на выходе старшего, п-го

разряда счетчика С1 образуются

прямоугольные

импульсы с частотой

так,

что на выходе старшего, п-го

разряда счетчика С1 образуются

прямоугольные

импульсы с частотой![]() ФормировательФИ

вырабатывает

из выходных периодических сигналов

С1

опорные

напряжения фазовращателя ФВ.

Нуль-орган

НО1

формирует

из выходных синусоидальных сигналов

ФВ

прямоугольные

периодические сигналы, по фронту которых

осуществляется запись кода С1

а

регистре

Р1,

где

фиксируется код текущего углового

положения вала.

ФормировательФИ

вырабатывает

из выходных периодических сигналов

С1

опорные

напряжения фазовращателя ФВ.

Нуль-орган

НО1

формирует

из выходных синусоидальных сигналов

ФВ

прямоугольные

периодические сигналы, по фронту которых

осуществляется запись кода С1

а

регистре

Р1,

где

фиксируется код текущего углового

положения вала.

Выходные

сигналы ГИ

поступают

также на первый вход схемы запрета СЗ,

на

управляющий вход которой поступают

сигналы с частотой![]() разряда

С1,

которые

запрещают прохождение через СЗ

каждого

импульса с номером

разряда

С1,

которые

запрещают прохождение через СЗ

каждого

импульса с номером![]() Среднее

значение частоты импульсов на выходе

схемы СЗ

равно

Среднее

значение частоты импульсов на выходе

схемы СЗ

равно![]() Де-

Де-

литель

частоты ДЧ

имеет

коэффициент деления, равный![]() где

где![]() —коэффицяент

умножения умножителя частоты УЧ,

так

что выходная частота

—коэффицяент

умножения умножителя частоты УЧ,

так

что выходная частота![]() делителяДТ

делителяДТ

![]()

Умножитель

УЧ

умножает

в![]() раз

выходную частотуФВ,

равную

сумме

раз

выходную частотуФВ,

равную

сумме

![]() так

что его выходная частота будет равна

так

что его выходная частота будет равна

![]()

На

выходе блоха вычитания БВЧ

образуется

частота

![]() равная

разностичастот

умножителя и делителя частоты:

равная

разностичастот

умножителя и делителя частоты:

![]()

При![]() выходная

частотаБВЧ

будет

равна

выходная

частотаБВЧ

будет

равна![]()

Выходной

сигнал БВЧ

аналогичен

выходному сигналу ФВ, имеющему

коэффициент

электрической редукции, равный![]() Второй

нуль-органИО2

формирует

из

выходных синусоидальных сигналов БВЧ

прямоугольные

импульсы, которые поступают

в каналы вычисления частоты вращения

и ускорения.

Второй

нуль-органИО2

формирует

из

выходных синусоидальных сигналов БВЧ

прямоугольные

импульсы, которые поступают

в каналы вычисления частоты вращения

и ускорения.

Счётчик

С2,

имеющий

разрядность, большую разрядности С1

на

дополнительный

знаковый разряд, вместе с ключом Кл,

дополнительным

триггером Т,

формирователем

задержанных импульсов ФЗИ

и

регистром Р2

образуют

канал вычисления

частоты вращения, причем вычисление

кода скорости заменено вычислением

кода приращения

![]() периодаТ

выходного

сигнала БВЧ

по

отношению

к периоду

периодаТ

выходного

сигнала БВЧ

по

отношению

к периоду![]() опорного

сигнала фазовращателя.

опорного

сигнала фазовращателя.

По

фронту выходного сигнала НО2

переходит

в нулевое состояние триггер Т

и

одновременно запускается ФЗИ.

Сигнал

с выхода триггера Т,

воздействуя

на

управляющий вход ключа Кл,

прекращает

поступление импульсов ГИ

на

счетный

вход С2.

Через

время, достаточное для переноса в этом

счетчике, на первом

выходе ФЗИ

вырабатывается

импульс, который поступает на вход

разрешения

записи Р2,

и

осуществляется в него запись кода![]() изС2.

изС2.

ИмПульс

со второго выхода ФЗИ,

воздействуя

на входы предустановки С2,

осуществляет

запись в него кода, соответствующего

промежутку времени между появлением

импульсов на первом и третьем выходах

ФЗИ.

Импульс

с третьего выхода

ФЗИ

переводит

в единичное состояние триггер Т,

в

результате чего открывается

ключ Кл

и

сигналы ГИ

вновь

поступают на вход С2.

Поскольку

коэффициенты

пересчета С/ и С2

равны,

в конце каждого периода выходного

сигнала

НО2

в

регистре Р2

будет

зафиксирован либо прямой код![]() если

если![]() либо

дополнительный код

либо

дополнительный код![]() если

если![]()

Фазовый

детектор ФД,

фильтр

ФР,

интегратор

![]() суммирующий

элемент и управляемый генератор УГ

образуют

канал вычисления ускорения. Выходное

напряжение

суммирующий

элемент и управляемый генератор УГ

образуют

канал вычисления ускорения. Выходное

напряжение

![]() детектораФД

пропорционально

разности фаз сигналов на его входах

или, иначе,

детектораФД

пропорционально

разности фаз сигналов на его входах

или, иначе,

![]() пропорционально

интегралу от разности между выходной

частотой

пропорционально

интегралу от разности между выходной

частотой![]() нуль-органаИО2

и

частотой генератора УГ.

В

операторной форме выходное

напряжение ФД

нуль-органаИО2

и

частотой генератора УГ.

В

операторной форме выходное

напряжение ФД

![]()

где![]() —постоянный

коэффициент; р—оператор Лапласа.

—постоянный

коэффициент; р—оператор Лапласа.

Выходной

сигнал ФД

непосредственно

подан на первый вход сумматора и

через интегратор

![]() с

передаточной функцией—

с

передаточной функцией—

![]() на

его второй вход.

на

его второй вход.

Следовательно, напряжение на выходе сумматора

![]()

Частота

генератора

![]() пропорциональна

с учетом коэффициента

пропорциональна

с учетом коэффициента![]() входному

управляющему напряжению

входному

управляющему напряжению![]()

Следовательно,

Рассмотреннаясхема

(рис. 8.6) обладает возможностью измерения

значительно

более низких скоростей и ускорении

вращения. Однако сам принцип построения

такого типа преобразователей имеет

методическую погрешность, влияние

которой на линейность его характеристики

выявляется из выражения; для

информационной емкости преобразователя![]() равной

равной

![]()

Как

следует из приведенного выражения, эта

погрешность определяется соотношением

![]() Устройства,

обеспечивающие оптимизацию соотношения

Устройства,

обеспечивающие оптимизацию соотношения![]() приводят

к усложнению цифрового блока умножения

при измерении низких

скоростей, поскольку при этом требуется

большое число разрядов выходных

кодов реверсивного счетчика и блока

измерения периодов.

приводят

к усложнению цифрового блока умножения

при измерении низких

скоростей, поскольку при этом требуется

большое число разрядов выходных

кодов реверсивного счетчика и блока

измерения периодов.

К

недостаткам такого построения

преобразователей относятся также и

ограничения

применения, поскольку не все СКВТ

допускают

работу в режиме вращающегося

поля. Так, например, СКВТ

типа

5 БВТ, 2,5 БВТ, СКТ 6465 Д. ДСПУ-128

и другие не имеют квадратурной обмотки

[48]. Не все СКВТ допускают

изменение частоты запитки в широком

диапазоне с целью уменьшения методической

погрешности преобразования скорости,

т. е. оптимизацию соотношения![]() Кроме

того, изменение

Кроме

того, изменение![]() сопровождается

переходными процессами

в формирователе синусоидальных

напряжений и в ФВ,

что

ограничивает

быстродействие преобразователя.

сопровождается

переходными процессами

в формирователе синусоидальных

напряжений и в ФВ,

что

ограничивает

быстродействие преобразователя.

Дрейф нуля и выходные токи интегратора в системе ФАПЧ обусловливают «паразитный» сдвиг фазы, что вносит дополнительную погрешность в изменение ускорения, а это особенно существенно при его малом значении.

Все вышеизложенное приводит к необходимости исследования иных путей построения совмещенного преобразователя угла, скорости и ускорения в код.