- •Державний комітет зв’язку та інформатизації

- •Перелік умовних позначень

- •Розділ 1 аналіз закономірностей побудовИk-значних статичних мікроелектронних структур

- •1.1. Термінологічний аналіз та обґрунтування принципу симбіозу

- •1.2. Архітектурно-логічні побудови цифрових іk-значних структур

- •1.3. Дослідження архітектур просторових цифрових комутаторів

- •1.4. Завдання аналiзу та оцiнки надiйностik-значних структур

- •1.5. Математичні моделіk-значного кодування

- •1.6. Методи і засобиk-значного кодування з надлишком

- •1.7. Дослідження метричних властивостейk-значних кодів

- •1.8. Вибір перспективних шляхів побудови просторовихk-значних структур

- •Висновки до першого розділу

- •Розділ 2 узагальнена теорія побудови високоефективних просторових статичниХk-значних структур

- •2.1. Структураk-значної площинно-просторової комірки

- •2.2. Формалізація принципу симбіозу багатовходовихk-значних структур

- •2.3. Метричні властивостіk-значних комутацiйних структур

- •2.4. Аналіз узагальнених статистичних параметрівk-значних структур

- •2.5. Аналiз точності дії статичнихk-значних структур

- •Висновки до другого розділу

- •Розділ 3 методи оцінки параметрів каналів іЗk-значним кодуванням

- •3.1. Ентропійні параметри k-значних каналів без завад

- •3.2. Властивості симетричних каналів ізk-значним кодуванням

- •3.3. Імовiрнiсть помилки пiд час декодуванняk-значних систематичних кодiв

- •3.4. Необхідна вносима надлишковість статичних просторовихk-значних структур

- •Висновки до третього розділу

- •Розділ 4 моделі, алгоритми та структурИk-значного кодування систематичними кодами

- •4.1. Математичні моделі кодування кодами Ріда – Соломона з крос-перемежуванням (circ-кодами)

- •4.2. Математичні моделі декодуванняCirc-кодів

- •4.3. Синтез алгоритмівk-значного кодування/декодування

- •4.4. Способи організації обчислень та синтезу структур операційних засобівCirc-кодера/декодера

- •4.5. Аналіз принципів побудови та дії двокаскадногоCirc-декодера

- •4.6. Порівняльний аналіз cтратегій декодуванняCirc-декодерів

- •Висновки до четвертого розділу

- •Розділ 5 принципи побудовИk-значних просторових пристроїв зовнішнього обміну (пзо)

- •5.1. Класифікації просторовихk-значних структур

- •5.2. Узагальнений рекурсивний структурний та формальний синтез пзо

- •5.3. Методи побудови рекурсивних струмових та потенційних пзо

- •5.4. Синтез просторових комутаторівk-значних сигналів

- •Висновки до п’ятого розділу

- •Розділ 6 математичні моделі, методи і структурні побудови універсальних функціональних перетворювачів (уфп) просторового типу

- •6.1. Моделі та методи структурного синтезу просторових уфп

- •6.2. Математичні моделі комбінаційного синтезу проміжних дешифраторів уфп

- •6.3. Моделі та методи структурного синтезу в асп просторових уфп

- •6.4. Моделі та методи синтезу в асп проміжних дешифраторів уфп

- •6.5. Моделі та методи синтезу в асп багатовходових уфп

- •Висновки до шостого розділу

- •Розділ 7 синтез та реалiзацiя k-значних операцiйних пристроїв новітніх обчислювальних систем

- •7.1. Класифікація операційних пристроїв

- •7.3. Чотиризначний матричний множник елементів поляґалуаGf(28)

- •7.4. Побудова паралельного конвеєрного арифметичного пристрою

- •7.5. Метод та засоби регенеруванняk-значних цифрових послiдовностей

- •Далі, оскільки сигнал має цифрову форму, то

- •Висновки до сьомого розділу

- •Основнi результати роботи та висновки

- •Список використаних джерел

Розділ 7 синтез та реалiзацiя k-значних операцiйних пристроїв новітніх обчислювальних систем

7.1. Класифікація операційних пристроїв

Практичне значення виконаних теоретичних досліджень із побудови k-значних структур визначається їх обчислювальною реалізованістю. Під час застосування в новітніх обчислювальних системах це найбільше залежить від можливості паралельної обробки даних: від швидкості та обсягу інформації, що підлягає опрацюванню. Поява високошвидкісних надвеликих інтегральних схем (ВІС/НВІС) прискорила кардинальні зміни в проектуванні архітектур обчислювальних структур і високошвидкісних обчислювальних систем [47, 181-185, 197 - 199]. Для збільшення потенційних можливостей НВІС у галузі ШІ системне проектування повинно охоплювати широкий спектр дисциплін, зокрема розроблення відповідної елементної бази, що моделює властивості природного інтелекту, архітектури обчислювача та його практичного застосування в задачах розпізнавання образів та обробки природної мови [200-203] і зорових образів, створення ефективних засобів завадостійкого кодування, а також оцінки надійності й оптимізації структур за надійнісними критеріями [186 - 193].

До недавна рішення більшості задач ШІ здійснювалось високошвидкісними багатопроцесорними обчислювальними системами (БОС) (суперкомп’ютерами), що включають до свого складу конвеєрні комп’ютери, матричні процесори та багатопроцесорні системи [47]. Проте БОС лише частково придатні для реалізації високошвидкісних обчислювальних систем, оскільки їх універсальне призначення призводить до ускладнення організації на системному рівні та непридатності для обробки в реальному масштабі часу.

Задовольнити вимоги щодо високошвидкісного оброблення сигналів можуть спеціалізовані обчислювачі [93], що бувають двох типів: із жорсткою та гнучкою архітектурою [47, 181]. Процесори зі жорсткою архітектурою, завдяки їх високій швидкості дії, можна використовувати в новітніх обчислювальних системах, проте спеціалізація веде до тривалих циклів проектування та високої вартості. Гнучкі (реконфігуровані з допомогою перепрограмування) паралельні процесори оброблення сигналів із розвитком НВІС стали не тільки практично здійсненими, а й у багатьох випадках дешевшими, ніж жорсткі процесори.

Програмовані засоби в надвисокошвидкісних новітніх обчислювальних системах (ОС) використовують традиційні принципи обчислення арифметичних функцій, що ґрунтуються на розкладі функції на елементарні операції. Принцип «максимум програми – мінімум затрат обладнання» не дозволяє досягти високої швидкодії і мікропрограмними засобами не користуються з огляду на необхідність вибірки та реалізації великої кількості мікрокоманд [47, 93, 181, 182].

У надвисокошвидкісних ОС із апаратною реалізацією засобів обчислення елементарних функцій тісно пов’язане поняття укрупненого оператора, яке класифікує множину операторів на основні і неосновні [181]. До основних – належать арифметичні і логічні оператори над скалярними аргументами, представленими у формі з фіксованою та плаваючою комою (ФК та ПК). Далі укрупнені оператори можна класифікувати за призначенням, типом та структурою.

Типи операторів – окремі біти, числа з ПК та ФК (дійсні і комплексні, одно- та багатовимірні масиви).

Структура укрупнених операторів передбачає такі основні варіанти: S–S – одномісна скалярна операція; V–S – перетворення вектора з одержанням скалярного результату; VS–V – векторно-скалярна операція з отриманням векторного результату; VV – векторно-векторна операція; VV–S – векторно-скалярна операція з одержанням скалярного результату.

За призначенням укрупнені оператори можна поділити на оператори загального і спеціального призначення.

Оператори загального призначення: найпростіші операції над векторами; операції редукції, обчислення елементарних функцій тощо. Найпростіші векторні операції виконуються над однойменними елементами векторів. Це операції додавання, віднімання, множення, ділення, звертання тощо.

До операцій векторної редукції належать такі операції, як знаходження суми елементів вектора, множення елементів вектора та суми добутків елементів двох векторів. Очевидно, що остання операція еквівалентна послідовності операцій поелементного перемноження двох векторів із наступним підсумовуванням елементів вектора [47, 182].

До елементарних відносять функції sin (cos), ln, exp, arctg тощо.

Прикладами операторів спеціального призначення можуть бути оператори оброблення сигналів (швидке перетворення Фур’є, згортання, кореляція, рекурсивна фільтрація тощо) та оператори, орієнтовані на вирішення задач моделювання і керування в реальному масштабі часу (числове диференціювання та інтегрування) [90, 93, 94, 183].

Одним із найчастіше

вживаних типів укрупнених операторів

є оператори обчислення елементарних

функцій (ЕФ), їх загальна частка серед

інших операторів може бути 3–5%, а час,

який необхідний для їх реалізації з

використанням програмних методів, може

становити більше ніж 50% часу рішення

всієї задачі, тому розглянемо апаратні

методи обчислення ЕФ, враховуючи, що в

ОС обумовлено необхідність обчислення

ЕФ виду cos x, sin x,

![]() ,

ах,

ln x, lg x.

,

ах,

ln x, lg x.

Серед апаратних методів обчислення ЕФ найбільшого поширення набули ітераційні і поліномні методи [47, 90, 93, 94, 172, 182, 183]. Ітераційні методи малопридатні для використання в багаторозрядних високопродуктивних ОС, оскільки вони передбачають послідовний процес обчислень. Окрім того, найбільш швидкодіючі з них або орієнтовані на застосування спеціальних ВІС (алгоритми Волдера і Меджіта), або базуються на виконанні порівняно довгої операції ділення (метод Ньютона) [183].

Використання при цьому поліномних обчислень дозволяє розпаралелювати процес обчислень під час апаратного обчислення елементарних функцій. Так, наприклад, при апроксимації довільної функції вона може бути зображена степеневим поліномом п’ятої степені [182], який, у свою чергу, може бути подано як

(7.1)

(7.1)

![]() ;

(7.2)

;

(7.2)

![]() ;

(7.3)

;

(7.3)

![]() ,

(7.4)

,

(7.4)

де Аi – коефіцієнти полінома; Хi – біжуче значення змінної.

Звідси видно, що паралельні обчислення ЕФ у задачах ШІ потребують різноманітних за складністю укрупнених операторів, що виконують операції множення, додавання, підняття до степеня, операторів виду Ах + В [47, 63, 90, 91, 94, 182, 184, 185] і, нарешті, підсумовування з нагромадженням [186, 187], розгляд побудови яких є одним із завдань цього розділу.

Подальшим кроком у розвитку поліномних методів є таблично-поліномні [113, 181], що дозволяють скоротити час обчислень, використовуючи таблицю коефіцієнтів, постійно розташованих у пам’яті ОС. Із методів поліномної апроксимації можна виділити три найпоширеніші: степеневі ряди, поліноми найкращого рівномірного наближення та розклад із використанням ортогональних поліномів.

Для прискорення процесів обчислення значень ЕФ на основі поліномної апроксимації застосовуються такі підходи: зменшення інтервалу апроксимації функції; переведення процесу обчислення ЕФ із формату подання з ПК у формат із ФК; розпаралелювання процесу обчислення; вибір схеми визначення значення апроксимуючого полінома [181]. Розпаралелювання процесу обчислення ЕФ може скоротити час реалізації, але для цього потрібні: засоби для програмування паралельних алгоритмів, кілька паралельно діючих операційних блоків та наявність можливості синхронізації їх роботи, і є одним із найчастіше застосовуваних підходів у надвисокошвидкісних сучасних обчислювальних структурах та системах ШІ.

Отже, як підсумок наведеної описової класифікації зазначимо, що в надвисокошвидкісних новітніх обчислювальних системах з апаратною реалізацією засобів обчислення для процесів самоорганізації необхідні, як показав ще Н. Вінер [188], операції підсумовування, множення та усереднення за часом (інтегрування), інакше кажучи підсумовування з накопиченням. А основне завдання моделювання природного інтелекту в штучному, зокрема на тактичному рівні обробки природної мови [53, 195], полягає в проблемах лінгвістичного аналізу, аналізу морфології, синтаксису та семантичних відмінностей. Стратегічний, вищий рівень зачіпає організацію метапроцедури розуміння, тобто співвіднесення даних, тексту з фактами та ситуаціями, що зберігаються в моделі світу (базі знань). Структура контексту – ось центральна проблема дослідження смислу, вона породжує структуру алгоритму, основою якого є вмонтовування слів і понять у певний набір універсальних пояснювальних схем [99, 100].

7.2. Паралельний нагромаджувальний підсумовувачk-значнихAN + B-кодів

Нині відоме значне число можливих варіантів побудови двійкових нагромаджувальних підсумовувачів [47], що відрізняються за функціональними можливостями, складністю апаратних рішень та швидкодією, причому зі взаємооберненою залежністю останніх двох показників якості. Але тенденції розвитку та вдосконалення технічних засобів опрацювання даних у новітніх обчислювальних системах в режимі реального часу з реалізацією їх у мікроелектронному виконанні приводять до пошуку шляхів удосконалення базисних схем, необхідних для процесів організації нагромаджувального підсумовування [186, 187].

Нижче розглядається алгоритм та пристрій [186], що має розширені функціональні можливості, оскільки реалізує нагромаджуюче додавання як додатних, так і від’ємних (r+1)-розрядних двійкових чисел у прямому, доповнюючому й оберненому кодах і характеризується малими апаратними затратами порівняно з відомими схемними рiшеннями.

Таке комплексне вдосконалення забезпечується використанням властивостей k-значних зображень чисел, зокрема арифметичних AN+B-кодів [189], у яких константа B уводиться для отримання простого переходу від прямого коду до оберненого при роботі з від’ємними числами. Простоти переходу досягається тим, що на вході пристрою до старшого (знакового) розряду операнда додається ціле число 2r, а від старшого розряду нагромадженої суми на його виході віднімається ціле число 2r+n, що еквівалентне зсуву операнда в область додатних чисел шляхом додавання до нього числа 2r та зворотного зміщення результату додавання в область фактичних значень шляхом віднімання від отриманого числа 2r+n.

Сутність алгоритму

[186] полягає в тому, що перед операцією

нагромаджувального додавання кожне

число Аі,

де і = 1, 2, ..., к перетворюється відповідно

до виразу:

![]()

![]() , (7.5)

, (7.5)

оскільки Аi + 2r та Аi – завжди додатне число.

При нагромаджувальному підсумовуванні накопичуються к = 2n (r + 1)-розрядних додатних чисел Аі шляхом нагромаджувального (r + 1)-розрядного додавання та n-розрядного послідовного підсумовування перенесень. Результат нагромадження можна зобразити так:

![]() ,

,

або, враховуючи, що к = 2:

![]() (7.6)

(7.6)

Після нагромаджувального підсумовування для одержання очікуваного результату з нагромадженої суми (7.6) віднімається число 2n+ r:

![]() . (7.7)

. (7.7)

Операції (7.5) та (7.7) для вхідних і вихідних чисел, зображених у доповнюючому коді, здійснюються шляхом інвертування старшого (r+1)-го знакового розряду вхідних чисел – для виконання операції (7.5) і старшого (n+r+1)-го інформаційного розряду вихідної суми (7.6) – для здійснення операції (7.7).

Доведення. Візьмемо (r+1)-розрядне двійкове число А, зображене в доповнюючому коді:

![]() ,

,

де Х – знаковий розряд, умовно відокремлений комою. Число А можна зобразити (r+1) іформаційними і одним знаковим розрядами:

![]() .

.

Після підсумовування А з додатним числом 2r отримаємо:

.

.

Тут

![]() – інвертоване значеннях,

що й потрібно було довести.

– інвертоване значеннях,

що й потрібно було довести.

Нехай тепер А –

додатне m-розрядне число (двійкове і

ціле);

![]() .

Віднявши від А двійкове число

.

Віднявши від А двійкове число![]() ,

отримуємо:

,

отримуємо:

.

.

Якщо

![]() ,

то х = 0 і

,

то х = 0 і![]() ;

;

якщо

![]() ,

х = 1 і

,

х = 1 і![]() .

.

Таким чином, після інвертування (n + r + 1)-го розряду числа, поданого як вираз (7.6), отримується сума (7.7) 2n вхідних чисел у доповнюючому коді. Вхідні числа, подані в оберненому коді, перетворюються в поповняльний код додаванням одиниці молодшого розряду до результату нагромаджувального підсумовування і далі продовжується процедура нагромаджувального підсумовування, згідно з виразом (7.6), причому кінцевий результат також поданий у доповнюючому коді.

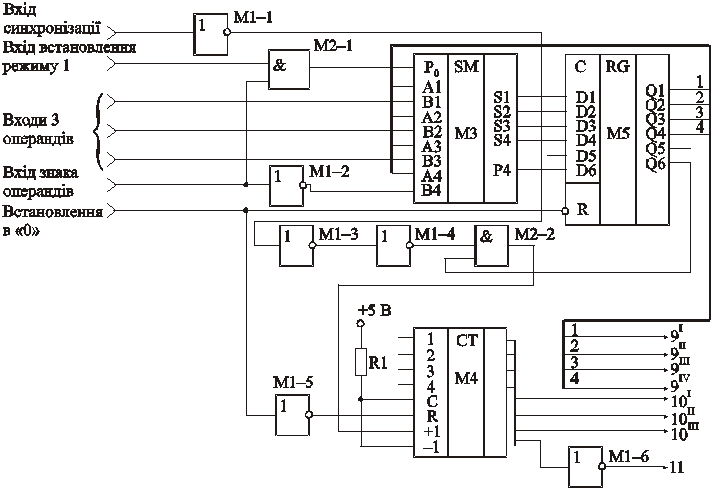

Алгоритм обчислень здійснюється пристроєм, функціональну схему якого подано на рис. 7.1. Цей пристрій містить вхід 1 керування, вхід 2 знака, вхідну шину 3 доданка, логічну схему 4І, нагромаджувальний підсумовувач 5, двійковий послідовний лічильник 6, перший 7 та другий 8 елементи НЕ, шини 9 виходу молодших розрядів нагромадженої суми, шини 10 старших розрядів остаточно нагромадженої суми, вихід 11 знака пристрою, а також вхід 12 перенесення –р, вхід 13 (r+1)-го розряду нагромаджувального підсумовувача 5 та вихід 14 перенесення +р підсумовувача 5.

Рис. 7.1. Функціональна схема паралельного нагромаджувального підсумовувача

Кожне число, що надходить на входи 2, 3 пристрою, зображене значущими і знаковим розрядами, а результат підсумовування – (n + r) значущими і одним знаковим розрядами, де r+1 і n – числа розрядів підсумовувача 5 і послідовного лічильника 6, відповідно. Як зазначалося, у реалізованому алгоритмі нагромадженого додавання вхідні позитивні числа зображаються прямими, а від’ємні – доповнюючими (оберненими) кодами залежно від сигналу на вході керування.

Результат нагромадженого додавання, що формується на шинах 9, 10 молодших і старших розрядів, відповідно, і виході знака 11, поданий у доповнюючому коді, то на вихід 1 керування надходить сигнал логічного нуля, у результаті на вході перенесення –р підсумовувача 5 – завжди 0. Знаковий розряд кожного числа, що приходить на вхід 2 знака, попередньо інвертується першим інвертором 7 НЕ і, разом зі значущою частиною числа надходить шиною 3 вхідного числа на вхід підсумовувача 5. Таким чином, кожне число, що надходить на входи 2, 3 пристрою, підсумовується з і-тою проміжною сумою підсумовувача 5. Результати перенесення +р підсумовувача 5 нагромаджуються лічильником 6, причому результат, одержаний на n-му розряді лічильника, інвертується другим інвертором 8 НЕ, утворюючи знаковий розряд результату нагромадженого додавання після виконання к (к = 2n) операцій.

Якщо від’ємні числа подані в оберненому коді, то на вхід 1 керування надходить сигнал логічної одиниці, у результаті чого на вході –р підсумовувача 5 із виходу елемента 4 І надходить логічна одиниця, а це, у свою чергу, забезпечує перетворення оберненого коду в поповняльний.

Принципову схему нагромаджувального підсумовувача, реалізованого на мікросхемах серії К533, показано на рис. 7.2. Вона складається зі шести інверторів (мікросхема М1), елементів І (мікросхема М2), чотирирозрядного підсумовувача (мікросхема М3), паралельного лічильника (мікросхема М4) і шестирозрядного паралельного регістра (М5).

Рис. 7.2. Структурно-логічна схема нагромаджувального підсумовувача з k-значним зображенням даних

Мікросхеми М3, М5 утворюють традиційну схему нагромаджувального підсумовувача, а елементи М1-3, М1-4 і М2-2 стробіюють вхід перенесення підсумовувача, причому елементи М1-3, М1-4 служать для усунення можливості виникнення гонів на виході М2-2 шляхом компенсації затримки спрацювання регістра М5. Результати перенесення підсумовувача М3 накопичуються лічильником М4, причому результат, отриманий на n-му розряді лічильника, інвертується елементом М1-6, утворюючи знаковий розряд результатів додавання після виконання R = 2n операцій нагромаджувального підсумовування.

Швикодійність пристрою визначається загальною затримкою на мікросхемах М4 – М6:

![]()

Для мікросхем серії К533 величина цієї затримки дорівнює 100 нс на один елемент. Отже, нагромаджувальне підсумовування за допомогою такого пристрою може бути надійно виконане з тактовими частотами порядку 9 ... 10 МГц.

Якщо потрібно збільшити розрядність операндів, підсумовувач М3 нарощується з одночасним збільшенням числа розрядів регістра М5. Число нагромаджуваних операндів збільшується за рахунок нарощування лічильника М4 із підключенням елемента М1-6 до старшого розряду максимально можливої суми на лічильнику М4.

Таким чином, завдяки використанню властивостей k-значних зображень чисел, шляхом використання операцій інвертування на вході нагромаджувального підсумовувача старшого (знакового) розряду операнда і старшого розряду нагромадженої суми на вході підсумовувача (нагромаджуючого лічильника) вдалося реалізувати нагромаджуюче додавання як від’ємних, так і додатних (r + 1)-розрядних двійкових чисел у прямому, доповнюючому й оберненому кодах та забезпечити широкі функціональні можливості пристрою нагромаджувального підсумовувача на основі серійно виготовлених ІС серії К533 без істотних додаткових апаратурних затрат. Порівняно з відомими методами нагромаджуючого підсумовування запропонований і розглянутий вище забезпечує також суттєве збільшення швидкодії, оскільки до його складу не входять складні схеми аналізу переповнення знакових розрядів у процесі обчислення та формування остаточного результату.