- •Державний комітет зв’язку та інформатизації

- •Перелік умовних позначень

- •Розділ 1 аналіз закономірностей побудовИk-значних статичних мікроелектронних структур

- •1.1. Термінологічний аналіз та обґрунтування принципу симбіозу

- •1.2. Архітектурно-логічні побудови цифрових іk-значних структур

- •1.3. Дослідження архітектур просторових цифрових комутаторів

- •1.4. Завдання аналiзу та оцiнки надiйностik-значних структур

- •1.5. Математичні моделіk-значного кодування

- •1.6. Методи і засобиk-значного кодування з надлишком

- •1.7. Дослідження метричних властивостейk-значних кодів

- •1.8. Вибір перспективних шляхів побудови просторовихk-значних структур

- •Висновки до першого розділу

- •Розділ 2 узагальнена теорія побудови високоефективних просторових статичниХk-значних структур

- •2.1. Структураk-значної площинно-просторової комірки

- •2.2. Формалізація принципу симбіозу багатовходовихk-значних структур

- •2.3. Метричні властивостіk-значних комутацiйних структур

- •2.4. Аналіз узагальнених статистичних параметрівk-значних структур

- •2.5. Аналiз точності дії статичнихk-значних структур

- •Висновки до другого розділу

- •Розділ 3 методи оцінки параметрів каналів іЗk-значним кодуванням

- •3.1. Ентропійні параметри k-значних каналів без завад

- •3.2. Властивості симетричних каналів ізk-значним кодуванням

- •3.3. Імовiрнiсть помилки пiд час декодуванняk-значних систематичних кодiв

- •3.4. Необхідна вносима надлишковість статичних просторовихk-значних структур

- •Висновки до третього розділу

- •Розділ 4 моделі, алгоритми та структурИk-значного кодування систематичними кодами

- •4.1. Математичні моделі кодування кодами Ріда – Соломона з крос-перемежуванням (circ-кодами)

- •4.2. Математичні моделі декодуванняCirc-кодів

- •4.3. Синтез алгоритмівk-значного кодування/декодування

- •4.4. Способи організації обчислень та синтезу структур операційних засобівCirc-кодера/декодера

- •4.5. Аналіз принципів побудови та дії двокаскадногоCirc-декодера

- •4.6. Порівняльний аналіз cтратегій декодуванняCirc-декодерів

- •Висновки до четвертого розділу

- •Розділ 5 принципи побудовИk-значних просторових пристроїв зовнішнього обміну (пзо)

- •5.1. Класифікації просторовихk-значних структур

- •5.2. Узагальнений рекурсивний структурний та формальний синтез пзо

- •5.3. Методи побудови рекурсивних струмових та потенційних пзо

- •5.4. Синтез просторових комутаторівk-значних сигналів

- •Висновки до п’ятого розділу

- •Розділ 6 математичні моделі, методи і структурні побудови універсальних функціональних перетворювачів (уфп) просторового типу

- •6.1. Моделі та методи структурного синтезу просторових уфп

- •6.2. Математичні моделі комбінаційного синтезу проміжних дешифраторів уфп

- •6.3. Моделі та методи структурного синтезу в асп просторових уфп

- •6.4. Моделі та методи синтезу в асп проміжних дешифраторів уфп

- •6.5. Моделі та методи синтезу в асп багатовходових уфп

- •Висновки до шостого розділу

- •Розділ 7 синтез та реалiзацiя k-значних операцiйних пристроїв новітніх обчислювальних систем

- •7.1. Класифікація операційних пристроїв

- •7.3. Чотиризначний матричний множник елементів поляґалуаGf(28)

- •7.4. Побудова паралельного конвеєрного арифметичного пристрою

- •7.5. Метод та засоби регенеруванняk-значних цифрових послiдовностей

- •Далі, оскільки сигнал має цифрову форму, то

- •Висновки до сьомого розділу

- •Основнi результати роботи та висновки

- •Список використаних джерел

4.4. Способи організації обчислень та синтезу структур операційних засобівCirc-кодера/декодера

Шляхом моделювання в попередньому підрозділі ми прийшли до аналізу та висвітлення етапів і процедур завадостійкого кодування, їх змісту, структури та особливостей, що надає в майбутньому можливості вдосконалення як алгоритмів, так і структур, застосування різних підходів до їх реалізації. Для створення захисту від несанкціонованого доступу, захищених і надійних високошвидкісних обчислювальних систем необхідно використовувати мінімум двокаскадне СIRC-кодування та обчислювачі й обчислення над k-значними символами, застосовувати суміщені чи рознесені в часі та просторі структури як кодування, так і декодування, змінювати вид породжуючого многочлена, довжини блоків та вид перемежування даних.

CIRC-декодер

складається (див. рис. 4.1) із п’яти блокiв:

блока деперемежування (ДП1) парних і

непарних символiв послiдовностi даних,

декодера С1

РС-коду (32, 28), блока деперемежування на

основi затримок неоднакової тривалості

(псевдовипадкове перемежування) (ДП2),

декодера С2

коду РС (28, 24) над

![]() та блока деперемежування на два кадри

(ДП3).

та блока деперемежування на два кадри

(ДП3).

Блоки деперемежування (ДП1 ... ДП3) дозволяють без збiльшення вартостi декодерiв знизити ймовiрнiсть помилки на входi чи всерединi системи та забезпечити виправлення як поодиноких, так i пачок помилок за рахунок декореляцiї помилок, що групуються шляхом їх розкиду. Для декодера (див. рис. 4.1) таку операцiю здiйснює в основному блок ДП2, для якого величина величина затримки блокiв символiв D = 4. Блок деперемежування ДП1 пiдвищує ефективнiсть роботи декодера С1, здiйснюючи затримку парних символiв на один такт послiдовностi, оскільки випадковi помилки двох сусiднiх символiв найлегше рознести в рiзнi кодовi слова.

Блок ДП3 забезпечує розширення меж корекцiї помилок серед непарних символiв, якi маскуються з допомогою лiнiйної iнтерполяцiї (обчисленням середнього вiд двох сусiднiх достовiрних символiв).

Під час створення різноманітних варіантів процесорів двоетапних CIRC-декодерів функціонально найжорсткішою ланкою є структура та алгоритм роботи деперемежувачів ДП1 ... ДП3. Характерною особливістю розглянутих процесів опрацювання інформації є їх своєрідна просторова хаотизація, що значною мірою перегукується з принципами дії та структурою персептрона [10]. Процедури впорядкованої хаотизації взагалі властиві cистемам ШІ, зокрема для багатопроцесорних обчислювальних систем [73, 47 - 49], мереж зв’язку при створенні систем комутації [69, 108, 121], систем бортових комутаторів у телеметрії [105] та універсальних k-значних функціональних перетворювачів просторового типу [83, 85, 86], систем перемежування для двокаскадного CIRC-кодування [134]. На множині цих фактів можна зробити узагальнюючий висновок, висунути гіпотезу про те, що будь-яка система штучного інтелекту за своєю структурою обов’язково містить етап просторової хаотизації каналів і зв’язків передавання та опрацювання даних.

Звертаючись до принципів дії нервової системи [9], процитуємо дослівно: «Нервові волокна, звичайно розгалужені, з’єднуються між собою в різних комбінаціях» – з одного боку, а з іншого – «У термінах квантової теорії це (в молекулі рецептора) відповідає твердженню про наявність дискретних рівнів енергії постсинаптичного рецептора та зв’язаних із ними можливих частот випромінювання і поглинання». У термінах теорії k-значних структур вказані концепції говорять про k-значний характер кодування сигналів та про наявність комбінаторного перемежування сигналів у живому організмі в процесі роботи нервової системи природного інтелекту. Приховані надії знайти базу для k-значних елементів та структур у методах формального синтезу у функціонально повних базисах і методах мінімізації розбилися об мізерні досягнення останніх літ та ентропійні дослідження каналів із надлишковим кодуванням.

Ентропійні дослідження розширюють детермінізм логічного синтезу до ймовірнісних випадкових процесів і моделей, відходять від лінійного детермінізму та однозначності причинно-наслідкових зв’язків, що веде до утворення нової, розширеної аксіоматики і нової теорії k-значних структур ШІ.

Методика оцінки ймовірності помилки та хибної тривоги (див. підрозділ 3.3) може бути застосована в автоматичному режимі для підвищення якості відтворення переданих даних. Описані алгоритми обчислень дозволяють здійснити синтез граничних структур процесорів паралельного, послідовного та паралельно-послідовного типу дії й оцінити їх щодо складності та швидкодії.

Каскади С1-

та С2-декодерів

можна реалізувати згідно з різними

архітектурними композиціями залежно,

по-перше, від стратегії дій під час

виправлення помилок та, по-друге, від

способів організації обчислень.

Аналізуючи структуру алгоритму обчислень,

можна вказати, що розглянутий раніше

спосіб організації обчислень передбачає

наявність у структурі процесора

CIRC-декодера

операційного блока – додавання за

модулем 2

![]() який виконує операцію додавання елементів

поляґалуа

який виконує операцію додавання елементів

поляґалуа

![]() за модулем 255

за модулем 255![]() ,

реалізуючий таким чином множення/ділення

елементів поляґалуа

,

реалізуючий таким чином множення/ділення

елементів поляґалуа

![]() шляхом додавання/віднімання показників

степенів примітивного елемента

= 00000010.

шляхом додавання/віднімання показників

степенів примітивного елемента

= 00000010.

На вхід блока mod

2 надходять два байтних символи, що

зображають два довільні 255-значні числа

з поля ґалуа,

із виходу теж отримуємо байтний символ

результату додавання, оскільки додавання

відбувається за mod2. Робота блока

![]() у режимі додавання описується такою ж

таблицею істинності, що й підсумовувач

за модулем 2, але з використанням переносу

всередині результуючого байта, за

винятком старшого восьмого розряду.

Оскільки підсумовувач

у режимі додавання описується такою ж

таблицею істинності, що й підсумовувач

за модулем 2, але з використанням переносу

всередині результуючого байта, за

винятком старшого восьмого розряду.

Оскільки підсумовувач![]() обробляє двозначні зображення показників

степеня від 0 до 255, то всі операнди на

його входах та виході також за розміром

дорівнюють байту. Зміна режиму на

віднімання здійснюється за рахунок

надходження на додатковий вхід

підсумовувачаmod255

однорозрядної ознаки віднімання.

обробляє двозначні зображення показників

степеня від 0 до 255, то всі операнди на

його входах та виході також за розміром

дорівнюють байту. Зміна режиму на

віднімання здійснюється за рахунок

надходження на додатковий вхід

підсумовувачаmod255

однорозрядної ознаки віднімання.

Таким чином, під

час реалізації CIRC-декодера

необхідні два операційні блоки, з яких

один виконує додавання елементів поля

ґалуа

![]() ,

а інший – додавання за

,

а інший – додавання за![]() показників, що відповідають певним

елементам поляґалуа,

степенів примітивного елемента .

Тому виникає задача оперативного

переходу від одного до іншого зображення

інформаційних символів. Здійснити

арифметичні операції над показниками

можна також із допомогою постійного

запам’ятовуючого пристрою (ПЗП),

приймаючи, що звертання до ПЗП еквівалентне

звертанню за адресою та її вмістом. У

подальшому цей операційний блок

позначається як М. Для вирівнювання

затримок у реальних цифрових схемах і

розпаралелювання процесів обчислень

застосовуються пристрої пам’яті

(регістри) RG. Під час розгляду методів

синтезу структур CIRC-декодерів

можлива неоднозначність у розумінні

терміна «блок». Тому для операційних

блоків вживається поняття «блок», а для

символів – «інформаційний блок».

показників, що відповідають певним

елементам поляґалуа,

степенів примітивного елемента .

Тому виникає задача оперативного

переходу від одного до іншого зображення

інформаційних символів. Здійснити

арифметичні операції над показниками

можна також із допомогою постійного

запам’ятовуючого пристрою (ПЗП),

приймаючи, що звертання до ПЗП еквівалентне

звертанню за адресою та її вмістом. У

подальшому цей операційний блок

позначається як М. Для вирівнювання

затримок у реальних цифрових схемах і

розпаралелювання процесів обчислень

застосовуються пристрої пам’яті

(регістри) RG. Під час розгляду методів

синтезу структур CIRC-декодерів

можлива неоднозначність у розумінні

терміна «блок». Тому для операційних

блоків вживається поняття «блок», а для

символів – «інформаційний блок».

Перший блок ERROR (рис. 4.4) виконує обчислення значень усіх трьох помилок. Другий блок KORR (рис. 4.5) виправляє три байтних помилкових символи. Об’єднання цих блоків (рис. 4.6) утворює блок знаходження та коригування трьох помилкових символів. На блок ERROR надходять три синдроми S0, S1, S2 та три номери i, j, l помилок у блоці даних.

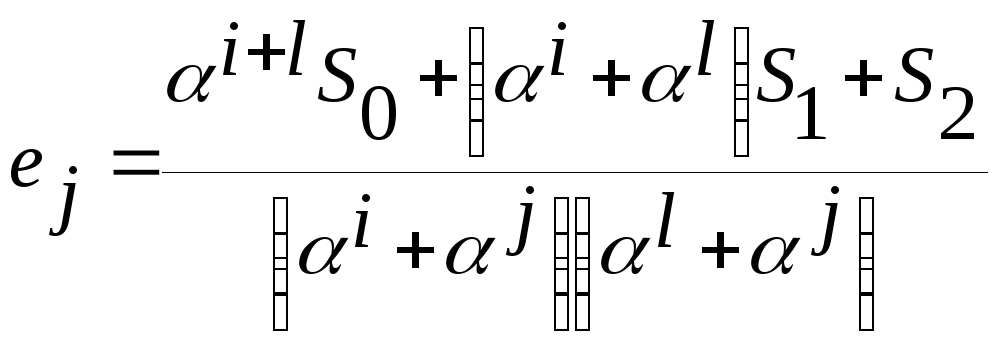

При послідовному алгоритмі обчислень на етапі С2-декодування значення помилки ei обчислюються з допомогою схеми обчислювача (див. рис. 4.4). згідно з виразом:

Рис. 4.4. Функціональна схема блока ERROR обчислювача трьох помилок (на прикладі помилки ei)

Рис. 4.5. Схема блока KORR виправлення трьох помилкових символів декодера С2

Рис. 4.6. Схема блока KORR3 коригування трьох помилок у декодері С2

Під час реалізації структури декодера С2 із паралельним алгоритмом обчислень значення всіх трьох помилок визначаються впаралель відповідно до таких виразів:

;

;

;

;

.

.

Відповідну структурну схему паралельного обчислювача для такого алгоритму зображено на рис. 4.7.

Рис.

4.7. Функціональна схема паралельного

обчислювача трьох помилок

Рис.

4.7. Функціональна схема паралельного

обчислювача трьох помилок

Під час реалізації послідовно-паралельної структури алгоритму обчислення здійснюються згідно з такими виразами:

![]()

![]()

![]()

Cтруктуру послідовно-паралельного обчислювача, що діє відповідно до вказаного способу, наведено на рис. 4.8.

Рис. 4.8. Структурна схема паралельно-послідовного обчислювача трьох помилок С2-декодера