- •В.Ф. Гузик проектирование проблемно - ориентированных вычислительных систем

- •Часть 1

- •Предисловие

- •Производительность суперкомпьютеров

- •Глава первая. Концепция построения многопроцессорных вычислительных систем с программируемой архитектурой (мвс па)

- •Глава вторая. Организация математического обеспечения мвс с программируемой архитектурой

- •2.1. Основы математического обеспечения многопроцессорных вычислительных систем с программируемой архитектурой

- •2.2. Организация машинных языков высокого уровня и технология программирования мвс с программируемой архитектурой

- •2.3. Организация параллельных вычислительных процессов в мвс с программируемой архитектурой

- •Глава третья. Проблемно-ориентированные мвс па

- •3.1.Методика перехода от систем дифференциальных и алгебраических уравнений к системе уравнений Шеннона

- •3.1.1.Представление исходной задачи в форме, удобной для реализации на цифровых интегрирующих машинах (цим)

- •3.1.2. Методика перехода от заданных функций к системе уравнений Шеннона

- •3.1.3. Методика перехода от заданных дифференциальных уравнений к системе уравнений Шеннона

- •3.1.4.Методика перехода от систем линейных алгебраических уравнений к системе уравнений Шеннона

- •3.1.5.Получение программных матриц соединений цифровых решающих модулей

- •3.1.6.Методика перехода от программных матриц к схеме соединения цифровых решающих модулей (црм) в цим с жесткими связями

- •3.2.Примеры структурной организации вычислительного процесса в цим.

- •3.2.1.Задача №1

- •3.2.2.Задача №2

- •3.2.3.Задача №3

- •Приложение 3.2

- •3.2.4.Задача №4

- •3.2.5.Задача №5

- •Глава четвёртая. Теоретические основы построения интегрируЮщих вычислительных структур модульного типа

- •4.1. Общая структурно-логическая схема проектирования (анализа и синтеза) модульных ивс

- •4.2. Представление задач для модульных ивс в операторном пространстве

- •4.3. Построение базиса в операторном -пространстве для ивс модульного типа

- •4.4. Разработка эффективного машинного алгоритма выбора базиса в операторном -пространстве

- •4.5. Математическая модель ивс модульного типа на основе t -алгоритмов

- •4.6. Примеры, иллюстрирующие работу базовой машины ивс

- •Глава пятая. Анализ и синтез универсальных решающих блоков интегрирующих вычислительных структур (ивс)

- •5.1. Синтез алгоритма универсального решающего блока интегрирующих вычислительных структур

- •5.2. Разработка алгоритма автоматического масштабирования переменных и приращений в универсальном решающем блока ивс

- •5.3. Построение структурных схем универсальных решающих блоков ивс с автоматическим масштабированием переменных

- •5.4 Разработка алгоритма универсального решающего блока, основанного на принципе цифрового слежения и синтез его структурной схемы

- •5.5.Проектирование решающей части интегрирующих вычислительных структур

- •Глава шестая. Проектирование функциональных модулей интегрирующих вычислительных структур

- •6.1. Исследование принципов построения коммутационных систем модульных интегрирующих вычислительных структур

- •6.2. Разработка волновых каскадных коммутирующих сред для интегрирующих вычислительных структур

- •6.3. Принципы построения цифровых решающих и функциональных модулей ивс

- •6.4.Определение параметров функциональных модулей интегрирующих вычислительных структур

- •6.5.Матричное представление функциональных модулей интегрирующих вычислительных структур

- •6.6. Построение специализированного микропроцессора интегрирующей вычислительной структуры

- •Глава седьмая. Система математического обеспечения модульных интегрирующих вычислительных структур

- •7.1. Структура системы математического обеспечения модульных ивс

- •7.2. Разработка языка структурного программирования высокого уровня для модульных ивс

- •7.3.Разработка транслятора, загрузчика и диспетчера системы программного обеспечения модульных ивс

- •7.4. Построение пакета системных программ для программного обеспечения ивс

- •7.5. Организация вычислительных процессов в модульных ивс

- •Глава восьмая. Однородные цифровые интегрирующие структуры

- •8.1. Цифровые интеграторы для оцис

- •8.2. Интерполяционные и экстраполяционные, одноразрядные и многоразрядные однородные цифровые интегрирующие структуры

- •Глава девятая. Примеры проектирования проблемно- ориентированных мвс на интегрирующих структурах

- •9.1. Моделирующий вычислительный комплекс для исследования систем инерциальной навигации на основе модульных ивс

- •9.2. Применение интегрирующих вычислительных структур для реализации систем управления манипуляционными устройствами автономных роботов

- •9.3. Специализированная вычислительная система для решения задач управления с прогнозированием

- •9.4. Логико-интегрирующие вычислительные структуры

- •Приложение 1 Примерный перечень

- •Министерство образования и науки российской федерации

- •Курс «Технология программирования»

- •Практические задания

- •Курс «Интерфейсы периферийных устройств»

- •Курс «Конструкторско-технологическое обеспечение производства эвм»

- •Библиографический список

- •Оглавление

2.3. Организация параллельных вычислительных процессов в мвс с программируемой архитектурой

Для

организации параллельных вычислительных

процессов разработан алгоритмический

язык «Ритм», позволяющий проводить

формальные преобразования

алгоритмов. Отличительной особенностью

данного языка является возможность

описания обобщенных процессов

функционирования МВС

с ПА, для чего введены такие понятия,

как выбор реализуемого в данный момент

подмножества из общего множества

операторов (обозначается символом

![]() ),

рассылка операторов и информации по

устройствам (символ

),

рассылка операторов и информации по

устройствам (символ![]() ),

организация каналов одновременного

обмена информацией между различными

процессорами и устройствами (символ

),

организация каналов одновременного

обмена информацией между различными

процессорами и устройствами (символ

![]() ),

исполнение выбранного подмножества

операторов (символом -О),

а также передача управления (символ

Е).

),

исполнение выбранного подмножества

операторов (символом -О),

а также передача управления (символ

Е).

Основной единицей функционирования системы выбран блок, в соответствии с которым осуществляется исполнение выбранного подмножества операторов. Вычислительный процесс описывается суперпозицией простых и составных блоков. Структурность процесса описания функционирования системы обеспечивает простоту и наглядность выполняемых преобразований.

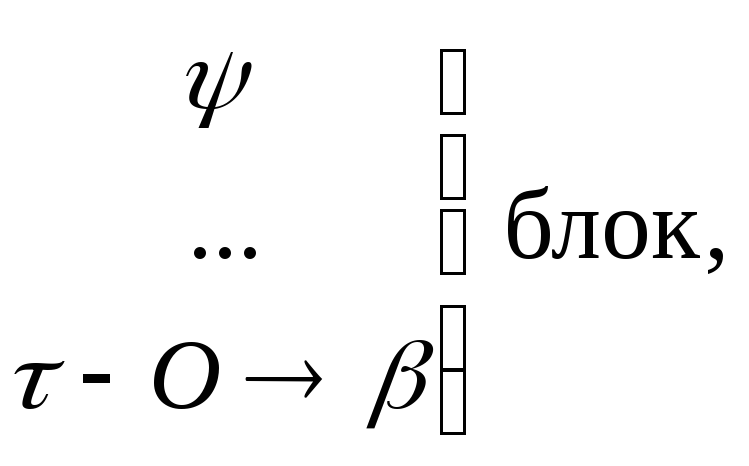

При описании алгоритмов каждый блок начинается идентификатором блока и завершается оператором исполнения данного блока

где – идентификатор блока; – идентификатор оператора или группы операторов, написанных перед последним оператором; – условие, определяющее продолжительность реализации алгоритмического блока.

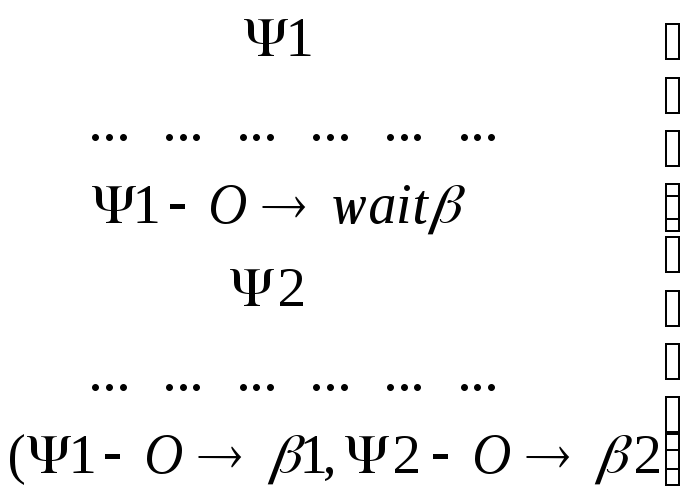

Если исполнение блока должно быть задержано до исполнения некоторого условия, то в конце блока ставится оператор ожидания wait, а оператор исполнения данного блока размещается в необходимом месте алгоритма

В приведенном алгоритме блоки, помеченные метками 1 и 2, исполняются на разных комплектах устройств одновременно.

Для описания обобщенных алгоритмов функционирования МВС с ПА используются алгоритмические операторы, описывающие действия. Алгоритмический оператор содержит указатель действия и два операнда. В качестве последних могут использоваться списки указателей.

Ниже

приведены основные операторы описания

алгоритма функционирования

МВС с ПА. Оператор сортировки имеет вид

FOq,

где F

–множество

операторов или элементов, из которых

производится выбор; q

–подмножество выбранных элементов.

Следующим оператором является оператор

рассылки по устройствам q

![]() p,

где q

– подмножество рассылаемых элементов;

р – подмножество устройств, воспринимающих

рассылаемые элементы.

Для описания процесса настройки каналов

связи используется оператор

Y

p,

где q

– подмножество рассылаемых элементов;

р – подмножество устройств, воспринимающих

рассылаемые элементы.

Для описания процесса настройки каналов

связи используется оператор

Y

![]() X,

где Y

–

множество выходов устройств; X

– множество входов устройств,

воспринимающих информацию. В случае

необходимости директивного

или условного изменения порядка

исполнения блоков алгоритма или

программы используется оператор передачи

управления ЕМ,

где

–

список

операторов, после которых осуществляется

переход; М – множество меток

точек перехода.

X,

где Y

–

множество выходов устройств; X

– множество входов устройств,

воспринимающих информацию. В случае

необходимости директивного

или условного изменения порядка

исполнения блоков алгоритма или

программы используется оператор передачи

управления ЕМ,

где

–

список

операторов, после которых осуществляется

переход; М – множество меток

точек перехода.

С помощью приведенных операторов достаточно наглядно описываются параллельные процессы функционирования МВС с ПА.

Организацию эффективных вычислительных процессов в МВС с ПА можно проводить с централизованным и децентрализованным управлением. Каждый из указанных способов управления реализуется с детерминированным и ассоциативным принципами распределения операторов по устройствам. Выбор того или иного способа реализации процесса управления определяется принятой конфигурацией, а также требованиями к быстродействию системы.

Многопроцессорная вычислительная система с ПА с централизованным управлением вычислительным процессом должна содержать, кроме основных устройств, специальную память команд (ОЗУК), предназначенную для хранения команд всех устройств, принимающих участие в выполнении преобразования информации, и программы, определяющей строгую последовательность функционирования системы. Программа состоит из отдельных блоков, каждый из которых содержит набор команд обрабатывающих устройств и устройств памяти, операторы выбора команд из ОЗУК, операторы рассылки их по соответствующим устройствам, а также операторы пуска и останова МВС с ПА.

При детерминированном принципе рассылки команд все устройства с помощью пространственного коммутатора соединяются с центральным устройством управления в каждом программном блоке поочередно, который выбирает команду и отсылает в регистр команд устройства, соединенного в данный момент времени с ЦУУ пространственным коммутатором. По окончании рассылки команд всем устройствам ЦУУ выбирает команду для коммутатора и устанавливает соединения между отдельными устройствами, участвующими в реализации данного блока. Далее выбираются команды пуска и завершения работы блока, по которым запускаются необходимые устройства, и ЦУУ переходит в режим ожидания окончания работы каждого запущенного устройства.

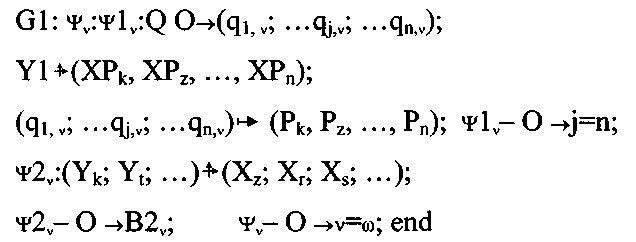

Формальная запись алгоритма функционирования МВС с ПА в этом случае выглядит следующим образом:

![]()

![]()

где

G1

–

начальный символ

алгоритма;

![]() метки блоков;Q

–

множество операторов

функционирования системы; Р

–

идентификатор

устройства.

метки блоков;Q

–

множество операторов

функционирования системы; Р

–

идентификатор

устройства.

В соответствии с данным алгоритмом из множества операторов Q выбирается пара операторов q j,v и q j+1,v первый из которых определяет адрес передачи второго оператора и устанавливает в пространственном коммутаторе связь между выходом ЦУУ Y1 и входом одного из устройств ХР. Второй оператор qj+1,v передается в регистр команд устройства Р. Далее указанная процедура повторяется до выполнения условия j = nv. После этого из множества операторов Q выбирается оператор qn+1,v, который регламентирует связь между входами и выходами устройств, участвующих в реализации программного блока v. По окончании установления связей между устройствами система запускается на реализацию операторов обработки информации и осуществляет их исполнение до удовлетворения условия B2v. Описанный процесс повторяется до удовлетворения условия v = .

Рассмотренный алгоритм обеспечивает наглядность описания функционирования системы и простоту его модификации. Основным недостатком данного способа организации вычислительного процесса является некоторая громоздкость в описании и реализации рассылки операторов по устройствам. Данную процедуру можно упростить, используя ассоциативный принцип рассылки операторов, в соответствии с которым каждый оператор снабжается признаком принадлежности тому или иному устройству. В этом случае при распределении операторов программного блока между устройствами устанавливается одновременная связь между ЦУУ и всеми участвующими в реализации данного блока устройствами. Каждый оператор, считываемый из ОЗУК, поступает сразу на все устройства, а воспринимается только тем устройством, которому он принадлежит. Это существенно сокращает объем программ и время их реализации.

Алгоритм функционирования МВС с ПА с централизованным управлением и ассоциативным принципом рассылки операторов по устройствам записывается следующим образом:

.

С целью дальнейшего сокращения затрат времени на подготовку отдельных устройств к выполнению операторов обработки информации целесообразно проводить предварительную рассылку их по устройствам. Для этого каждое устройство системы снабжается запоминающим устройством для хранения команд. Все устройства в очередном программном блоке сами выбирают для себя команду из собственного запоминающего устройства команд. В запоминающем устройстве ЦУУ в этом случае хранятся только операторы пуска и завершения каждого программного блока. Указанный способ управления вычислительным процессом МВС с ПА будем называть децентрализованным.

Как и в предыдущем случае, рассылка команд по ОЗУК всех устройств может осуществляться по детерминированному или ассоциативному принципу. Ниже представлен алгоритм функционирования МВС с ПА с децентрализованным управлением и детерминированным принципом рассылки команд:

где N – число устройств в МВС с ПА; Т – число блоков в программе.

При данном способе управления необходимо проводить предварительную сортировку операторов по признаку принадлежности к тому или иному устройству. Это, в свою очередь, требует специальных устройств подготовки загрузочных модулей или соответствующих программ в устройствах подготовки. В качестве таких устройств могут выступать универсальные мини-ЭВМ, скомплексированные с МВС ПА, или реализованные на отдельных мини-ЭВМ кросс-системы подготовки загрузочных модулей.

Избежать указанного недостатка можно при использовании ассоциативного принципа рассылки команд по устройствам в соответствии со следующим алгоритмом:

Описанные алгоритмы организации вычислительных процессов в МВС с ПА обеспечивают достижение максимальной производительности в условиях конкретных ограничений.

Дальнейшее совершенствование алгоритма реализации вычислительных процессов основывается на выборе конкретных способов реализации отдельных этапов. Общая классификация методов реализации вычислительных процессов в МВС с ПА приведена на рис. 2.4.

Рис. 2.4 Классификация методов реализации вычислительных процессов

Исходя из общей концепции построения МВС ПА и организации математического обеспечения в них, будем рассматривать при использовании методики проектирования и создания ПОВС интегрирующего типа в начале, а потом ПОВС потокового типа.

Для построения структурно-логической схемы проектирования (анализа и синтеза) модульных интегрирующих вычислительных систем (ИВС) приведём методику перехода от исходных систем уравнений к порождающей системе уравнений Шеннона, которую мы рассматривали в учебном пособии по подготовке бакалавров в восьмом семестре, и примеры решения ряда задач по этой методике.