- •В.Ф. Гузик проектирование проблемно - ориентированных вычислительных систем

- •Часть 1

- •Предисловие

- •Производительность суперкомпьютеров

- •Глава первая. Концепция построения многопроцессорных вычислительных систем с программируемой архитектурой (мвс па)

- •Глава вторая. Организация математического обеспечения мвс с программируемой архитектурой

- •2.1. Основы математического обеспечения многопроцессорных вычислительных систем с программируемой архитектурой

- •2.2. Организация машинных языков высокого уровня и технология программирования мвс с программируемой архитектурой

- •2.3. Организация параллельных вычислительных процессов в мвс с программируемой архитектурой

- •Глава третья. Проблемно-ориентированные мвс па

- •3.1.Методика перехода от систем дифференциальных и алгебраических уравнений к системе уравнений Шеннона

- •3.1.1.Представление исходной задачи в форме, удобной для реализации на цифровых интегрирующих машинах (цим)

- •3.1.2. Методика перехода от заданных функций к системе уравнений Шеннона

- •3.1.3. Методика перехода от заданных дифференциальных уравнений к системе уравнений Шеннона

- •3.1.4.Методика перехода от систем линейных алгебраических уравнений к системе уравнений Шеннона

- •3.1.5.Получение программных матриц соединений цифровых решающих модулей

- •3.1.6.Методика перехода от программных матриц к схеме соединения цифровых решающих модулей (црм) в цим с жесткими связями

- •3.2.Примеры структурной организации вычислительного процесса в цим.

- •3.2.1.Задача №1

- •3.2.2.Задача №2

- •3.2.3.Задача №3

- •Приложение 3.2

- •3.2.4.Задача №4

- •3.2.5.Задача №5

- •Глава четвёртая. Теоретические основы построения интегрируЮщих вычислительных структур модульного типа

- •4.1. Общая структурно-логическая схема проектирования (анализа и синтеза) модульных ивс

- •4.2. Представление задач для модульных ивс в операторном пространстве

- •4.3. Построение базиса в операторном -пространстве для ивс модульного типа

- •4.4. Разработка эффективного машинного алгоритма выбора базиса в операторном -пространстве

- •4.5. Математическая модель ивс модульного типа на основе t -алгоритмов

- •4.6. Примеры, иллюстрирующие работу базовой машины ивс

- •Глава пятая. Анализ и синтез универсальных решающих блоков интегрирующих вычислительных структур (ивс)

- •5.1. Синтез алгоритма универсального решающего блока интегрирующих вычислительных структур

- •5.2. Разработка алгоритма автоматического масштабирования переменных и приращений в универсальном решающем блока ивс

- •5.3. Построение структурных схем универсальных решающих блоков ивс с автоматическим масштабированием переменных

- •5.4 Разработка алгоритма универсального решающего блока, основанного на принципе цифрового слежения и синтез его структурной схемы

- •5.5.Проектирование решающей части интегрирующих вычислительных структур

- •Глава шестая. Проектирование функциональных модулей интегрирующих вычислительных структур

- •6.1. Исследование принципов построения коммутационных систем модульных интегрирующих вычислительных структур

- •6.2. Разработка волновых каскадных коммутирующих сред для интегрирующих вычислительных структур

- •6.3. Принципы построения цифровых решающих и функциональных модулей ивс

- •6.4.Определение параметров функциональных модулей интегрирующих вычислительных структур

- •6.5.Матричное представление функциональных модулей интегрирующих вычислительных структур

- •6.6. Построение специализированного микропроцессора интегрирующей вычислительной структуры

- •Глава седьмая. Система математического обеспечения модульных интегрирующих вычислительных структур

- •7.1. Структура системы математического обеспечения модульных ивс

- •7.2. Разработка языка структурного программирования высокого уровня для модульных ивс

- •7.3.Разработка транслятора, загрузчика и диспетчера системы программного обеспечения модульных ивс

- •7.4. Построение пакета системных программ для программного обеспечения ивс

- •7.5. Организация вычислительных процессов в модульных ивс

- •Глава восьмая. Однородные цифровые интегрирующие структуры

- •8.1. Цифровые интеграторы для оцис

- •8.2. Интерполяционные и экстраполяционные, одноразрядные и многоразрядные однородные цифровые интегрирующие структуры

- •Глава девятая. Примеры проектирования проблемно- ориентированных мвс на интегрирующих структурах

- •9.1. Моделирующий вычислительный комплекс для исследования систем инерциальной навигации на основе модульных ивс

- •9.2. Применение интегрирующих вычислительных структур для реализации систем управления манипуляционными устройствами автономных роботов

- •9.3. Специализированная вычислительная система для решения задач управления с прогнозированием

- •9.4. Логико-интегрирующие вычислительные структуры

- •Приложение 1 Примерный перечень

- •Министерство образования и науки российской федерации

- •Курс «Технология программирования»

- •Практические задания

- •Курс «Интерфейсы периферийных устройств»

- •Курс «Конструкторско-технологическое обеспечение производства эвм»

- •Библиографический список

- •Оглавление

9.4. Логико-интегрирующие вычислительные структуры

Часто при решении конкретных задач управления и моделирования требуется расширить логические возможности однородных цифровых интегрирующих структур.

При решении задач управления сложными динамический системами и моделировании поведения различных объектов в реальном масштабе времени часто необходимо учитывать различного рода возмущающие воздействия, которые существенно влияют на процесс решения поставленной задачи. При этом, в зависимости от полученного результата решения и (или) от воздействия внешней среды на объект, может измениться алгоритм решения задачи, или ход вычислительного процесса в однородных цифровых интегрирующих структурах, что вызывает в конечном счете изменение коммутации специализированных процессоров (Пк), которые назовем универсальными решающими блоками (УРБ), или активизацию той или иной ветви программы вычислений, которая структурным образом реализована в УРБ ОЦИС.

Для решения такого рода задач ОЦИС должка обладать возможностью перестройки своей внутренней структуры в зависимости от сложившейся программной (по результатам решения) или внешней ситуации. Такую возможность имеют ОЦИС с расширенными логическими возможностями, в которых логическим путём изменяются программные матрицы Аp и Аq. Эти однородные цифровые интегрирующие структуры названы логико-интегрирующими вычислительными структурами (ЛИВС) [18, 21, 20].

Идея построения логических вычислительных структур на основе цифровых интегрирующих машин высказана в paботах[76, 77], где показаны пути расширения логических возможностей ЦИМ без значительного усложнения их внутренней структуры. Принцип построения заключается в расширении логических возможностей ЦИМ последовательного и параллельного типа за счет включения в состав аппаратуры ЦИМ запоминающего устройства (ЗУ), хранящего программу коммутации УРБ, а также числовую информацию.

Вычислительные

машины, построенные на основе ЛИВС с

УРБ, изменяют программы

коммутации

УРБ в зависимости от результата анализа

внешней (Q)

и

внутренней

![]() информации, описывающей внешние и

программные ситуации. В состав такой

ЛИВС должен входить

логический

преобразователь (ЛП). Для синтеза такого

ЛП нужно детально изучить изменения

программных матриц коммутации

информации, описывающей внешние и

программные ситуации. В состав такой

ЛИВС должен входить

логический

преобразователь (ЛП). Для синтеза такого

ЛП нужно детально изучить изменения

программных матриц коммутации

![]() УРБ в ЛИВС в зависимости от типа решаемых

задач,

внешних и внутренних условий (ситуаций).

Структура ЛП базируется на алгоритмах

коррекции программных матриц при

переходе от задачи к другой или к

различным ветвям вычислительного

процесса при реализации на ЛИВС одной

задачи. Коррекция программных матриц

заключается в замене элементов матриц

УРБ в ЛИВС в зависимости от типа решаемых

задач,

внешних и внутренних условий (ситуаций).

Структура ЛП базируется на алгоритмах

коррекции программных матриц при

переходе от задачи к другой или к

различным ветвям вычислительного

процесса при реализации на ЛИВС одной

задачи. Коррекция программных матриц

заключается в замене элементов матриц

![]() равных "0" на

равных "0" на ![]() ,

равных "1" и

наоборот.

,

равных "1" и

наоборот.

Структурная схема ЛИВС приведена на рис. 9.15. В состав ЛИВС входят решающие блоки - УРБ, строительство ввода исходной информации - УВ, логический преобразователь - ЛП, дополнительный внешний вход - Q, запоминающее устройство - ЗУ, устройство вывода результатов - Увыв.

Принцип

построения и закон функционирования

ЛП логико-интегрирующей вычислительной

структуры

заключается

в следующем. Программирование ЛИВС

производится путём вычисления элементов

матрицы коммутации входов подынтегральной

функции Ap,

матрицы Aq

коммутации входов переменной

интегрирования, вектора начальных

условий УРБ

-![]() ,

причем элементы матриц

,

причем элементы матриц

![]() .

Далее производится настройка КС ЛИВС

в соответствии с программой

.

Далее производится настройка КС ЛИВС

в соответствии с программой

![]() отображениеАp,

Аq

в

КС

и ввод в УРБ компонент вектора

отображениеАp,

Аq

в

КС

и ввод в УРБ компонент вектора

![]() .

.

Puc. 9.15. Структурная схема ЛИВС

Рис 9.16. Расширенная структурная схема ЛИВС

Работа

ЛП заключается в переключении КС на

решение той или иной задачи из заданного

множества задач. Пусть имеется набор

![]() алгоритмов решения задачи, причем

порядок выполнения алгоритмов

произвольный, зависящий как от внешних

условий, так и от программных ситуаций.

Каждому алгоритму множестваА

можно

поставить в соответствие программу

алгоритмов решения задачи, причем

порядок выполнения алгоритмов

произвольный, зависящий как от внешних

условий, так и от программных ситуаций.

Каждому алгоритму множестваА

можно

поставить в соответствие программу

![]() при условии

реализуемости

задачи на ЛИВС, предварительно вычислив

элементы

при условии

реализуемости

задачи на ЛИВС, предварительно вычислив

элементы

![]() матриц коммутации Аp,

Аq.

Закодировав различные ситуации с помощью

n-разрядных

двоичных переменных

матриц коммутации Аp,

Аq.

Закодировав различные ситуации с помощью

n-разрядных

двоичных переменных

![]() можно каждойi-й

ситуации

сопоставить свою конъюнкцию

можно каждойi-й

ситуации

сопоставить свою конъюнкцию

![]() .

Тогда

для каждого алгоритма из А

можно

записать все конъюнкции, равенство

которых единице вызывает переход ЛП на

выполнение данного алгоритма, т.е.

.

Тогда

для каждого алгоритма из А

можно

записать все конъюнкции, равенство

которых единице вызывает переход ЛП на

выполнение данного алгоритма, т.е.

![]()

а элементы матриц коммутации Аp, Аq соответствующих Аm, можно вычислять по формуле

![]() .

.

Обобщая

по всем возможным алгоритмам

![]() ,

получаем:

,

получаем:

![]() .

.

Приведем

пример, поясняющий принцип работы ЛП,

получающего элементы матриц коммутации

Apq.

Пусть для решения некоторой задачи на

ЛИВС требуется выполнить два алгоритма

![]() ,

причем последовательность их выполнения

зависит от внешних ситуаций следующим

образом:

,

причем последовательность их выполнения

зависит от внешних ситуаций следующим

образом:

|

x1 |

x2 |

A |

|

0 0 1 1 |

0 1 0 1 |

A1 A2 A2 A1 |

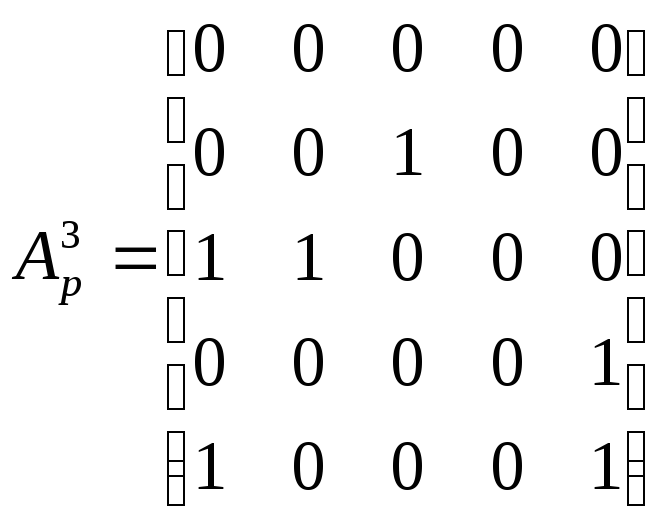

Пусть также матрица Ар при выполнении алгоритма A1 имеет вид

а при выполнении алгоритма А2 вид

ЛП будет вычислять элементы по следующим формулам:

Таким образом, логический преобразователь в соответствии с внешними ситуациями, характеризуемыми наборами внешних логических переменных, поступающих на его входы, производит вычисление в процессе решения задачи элементов матриц Ар, Аq и перестраивает КС ЛИВС согласно вычисленным матрицам, Ар, Аq что в принципе является управлением, адаптивным к изменяющимся внешним условиям.

Рассмотрим методику синтеза логического преобразователя логико-интегрирующей вычислительной структуры.

Логический преобразователь, как отмечалось выше, на основе результатов выполнения предыдущих алгоритмов и в соответствии с внешними условиями, характеризуемыми внешними логическими переменными, поступающими на внешние входы логического преобразователя, вычисляя в хода решения задачи элементы матриц Ар и Аq, и производя последующую коммутацию УРБ согласно вычисленным матрицам Ар и Аq, может управлять ходом решения задачи в зависимости от складывающейся ситуации [21, 22].

Введём

понятие

обобщенных

программных матриц Ap

и Aq,

состоящих из элементов

![]() .

Если ЛИВС

находится

в некотором состоянии al

,

то будем считать, что

.

Если ЛИВС

находится

в некотором состоянии al

,

то будем считать, что

![]() .

.

Для

каждого из

элементов

![]() матриц Ap

и Aq

образуем группы

матриц Ap

и Aq

образуем группы

![]() ,

состоящие из

некоторых

элементов

,

состоящие из

некоторых

элементов

![]() соответственно. Элемент

соответственно. Элемент

![]() входит в

группу

входит в

группу

![]() ,

если существует хотя бы один входной

логический набор

,

если существует хотя бы один входной

логический набор![]() для которого

для которого![]() .

.

Тогда

элементы

![]() обобщенных

программных матриц ЛИВС можно представить

в следующем виде

обобщенных

программных матриц ЛИВС можно представить

в следующем виде

![]() (9.17)

(9.17)

Логический преобразователь ЛИВС реализует данные переключательные функции, которые являются входными управляющими сигналами коммутаторов.

Логико-интегрирующую вычислительную структуру можно представлять как композицию двух автоматов [70] настроечного H и функционального Ф, в которых:

![]() - входной рабочий

алфавит;

- входной рабочий

алфавит;

![]() - входной настроечный

алфавит;

- входной настроечный

алфавит;

![]() - выходной алфавит;

- выходной алфавит;

![]() - множество функций

переходов;

- множество функций

переходов;

![]() - множество функций

выходов.

- множество функций

выходов.

Под

настроечным автоматом Н

следует

понимать автомат, с помощью которого

задаются все возможные функции переходов

и выхoдов

функционального автомата Ф.

Функциональный автомат Ф

перерабатывает

входные слова в алфавите Х

в

выходные

слова в алфавите Y

в соответствии с заданными функциями

выходов и переходов.

В

работе ЛИВС следует различать фазы

настройки и фазы функционирования.

Под фазой настройки будем понимать

процесс

задания

фикций

переходов и выходов для автомата Ф

путем

передачи на входы автомата Н

определенной

последовательности входных сигналов

в алфавитах

V

и

![]() - множеств обратных настроечных сигналов,

- множеств обратных настроечных сигналов,

![]() .

Под фазой функционирования будем

понимать процесс переработки входных

слов в алфавите X

в выходные слова в алфавите Y

при заданных с помощью автомата функциях

переходов

и

выходов.

.

Под фазой функционирования будем

понимать процесс переработки входных

слов в алфавите X

в выходные слова в алфавите Y

при заданных с помощью автомата функциях

переходов

и

выходов.

Логико-интегрирующая

вычислительная структура (рис. 9.16)

работает

следующим образом: по буквам v![]() и

и![]() выбираются функции переходовi

и выходов

выбираются функции переходовi

и выходов

![]() ,

,

где f

-

настроечная функция; затем ЛИВС работает

в

соответствии

с функциями i

и j.

Так как в ЛИВС воспроизводится система

уравнений

Шеннона,

то процесс перестройки заключается в

изменении коммутации между УРБ и введении

в них соответствующих начальных условий.

Процесс перестройки КС сводится к

изменению программных матриц Ap

и Aq,

составленных из коэффициентов

![]() и

и![]() в

зависимости от внешних воздействий и

логических условий, выработанных ЛИВС.

Блок логических условий (БЛУ) служит

для выработки настроечных сигналов

в

зависимости от внешних воздействий и

логических условий, выработанных ЛИВС.

Блок логических условий (БЛУ) служит

для выработки настроечных сигналов![]() в зависимости от

хода

вычислительного процесса.

в зависимости от

хода

вычислительного процесса.

Блок

настройки (БН) управляет настройкой КС

ЛИВС

по

управляющим сигналам

![]() и

и![]()

Рассмотрим

ЛИВС, состоящую из N

УРБ

и 2N2

коммутирующих

элементов

![]() и

и![]() (рис. 9.17). Так как матрицыAp

и

Aq

имеют одинаковый физический смысл, то

в дальнейшем рассуждения, проведенные

для одной из матриц, будут справедливы

и для другой. Настройка КС сводится к

получению управляющих сигналов

(рис. 9.17). Так как матрицыAp

и

Aq

имеют одинаковый физический смысл, то

в дальнейшем рассуждения, проведенные

для одной из матриц, будут справедливы

и для другой. Настройка КС сводится к

получению управляющих сигналов

![]() по матрицеА.

Максимальное

количество матриц, которое можно получить

из исходной, равно

по матрицеА.

Максимальное

количество матриц, которое можно получить

из исходной, равно

![]() .

.

Рис. 9.17. Структурная схема ЛИВС, состоящей из N УРБ

Рис. 9.18. Функциональная схема блока настройки ЛИВС

В ЛИВС изменения программной матрицы будут зависеть от входных двоичных сигналов Y и V:

![]()

![]() V

= {0, 1}

V

= {0, 1}

Пусть

имеется множество программируемых

матриц,

![]() ,

,![]() ,

отражающих коммутацию УРБ по входамyp,

или yq.

Представим функцию

,

отражающих коммутацию УРБ по входамyp,

или yq.

Представим функцию

![]() в

табличной форме (табл.

9.1).

в

табличной форме (табл.

9.1).

Таблица 9.1

|

|

|

…

|

|

|

|

… |

|

F |

|

0 |

0 |

... |

0 |

0 |

0 |

... |

0 |

F1 |

|

1 |

0 |

... |

0 |

0 |

0 |

... |

0 |

F2 |

|

... |

... |

... |

... |

... |

... |

... |

... |

... |

|

1 |

1 |

... |

1 |

1 |

1 |

... |

1 |

|

Множество

всех наборов образует конечное множество

![]()

![]() .

Поставим соответствие каждой пpoгpaммой

матрице

.

Поставим соответствие каждой пpoгpaммой

матрице

![]() вполне

определённый и единичный набор

вполне

определённый и единичный набор

![]() настроечных

сигналов Y

и

V.

Так как отображение А

= f(F)

однозначно, то при выборе количества

настроечных сигналов необходимо

соблюдать следующее условие:

настроечных

сигналов Y

и

V.

Так как отображение А

= f(F)

однозначно, то при выборе количества

настроечных сигналов необходимо

соблюдать следующее условие:

![]() ,

откуда

,

откуда

![]() . (9.18)

. (9.18)

Н![]() азовем

функции

азовем

функции![]() настроечными. Рассмотрим матрицу

настроечными. Рассмотрим матрицу![]() .

Пусть прообразом этой матрицы будет

настроечная функция.

.

Пусть прообразом этой матрицы будет

настроечная функция.

. Будем задавать единичные элементы матрицы соответствующим ей наборам F из табл. 9.1.

![]() . (9.19)

. (9.19)

Возможен случай,

когда один и тот же единичный элемент

встречается в нескольких программных

матрицах. Номера этих матриц образуют

конечное

множество

![]() и этим матрицам соответствуют настроечные

функции

и этим матрицам соответствуют настроечные

функции![]() .

Тогда этот единичный элемент с учетом

выражения [9.19]

можно

определить в

таком

виде:

.

Тогда этот единичный элемент с учетом

выражения [9.19]

можно

определить в

таком

виде:

(9.20)

(9.20)

Определив

каждый элемент матриц по выражению

(9.20), можно записать новую матрицу

![]() , которая задает настройку КС ЛИBC

для всех программ. Назовем матрицу R

обобщенной.

, которая задает настройку КС ЛИBC

для всех программ. Назовем матрицу R

обобщенной.

Теперь

рассмотрим общий случай, когда одна

программная матрица имеет прообразом

несколько настроечных функций. Пусть

номера этих функций образуют конечное

множество

![]() .

.

В этом случае любой единичный элемент матрицы A по аналогии с выражением (9.20) можно записать так:

(9.21)

(9.21)

Исходя из тех же соображений, что и при выводе формулы (9.20), единичные элементы сообщённой матрицы R будут иметь вид

(9.22)

(9.22)

В последнем рассмотренном случае условие (9.18) несколько изменит свой вид:

![]() . (9.23)

. (9.23)

Легко

заметить, что если множества G,

определенные для каждой матрицы, содержат

только по одному элементу, то условие

(9.23)

переходит

в условие (9.18). Если некоторый элемент

во всех матрицах является нулевым, то

множество

![]()

и вместо этого элемента в обобщенной

матрице записывается 0.

и вместо этого элемента в обобщенной

матрице записывается 0.

Обобщенная матрица R полностью определит настройку КС по выбранному алгоритму работы ЛИВС. По уравнениям (9.19) и (9.20) легко синтезировать функциональную схему блока настройки. Функции могут быть минимизированы обычными методами.

Алгоритм настройки запишется в следующем виде:

1°. Определить программные матрицы A. Перейти к 2°.

2°. Определить базовые наборы F . Перейти к 3°.

3°. Определить множества G базовых наборов для каждой программной матрицы. Перейти к 4°.

4°. Определить множества Kij номеров тех матриц, у которых одноименные элементы aij = 1. Перейти к 5°.

5°. Определить функции S для каждой матрицы по формуле. (19.20). Перейти к 6°.

6°. Минимизировать функции S . Перейти к 7°.

7°. На основании уравнений, полученных в 6°, записать элементы обобщенной матрицы согласно уравнению (9.21). Перейти к 8°.

8°. Конец.

Рассмотрим пример реализации блока настройки для ЛИВС, состоящей из четырех УPБ. Пусть нам даны три матрицы;

.

.

В

каждый из определенных моментов времени

КС адекватна

одной

из

матриц, которые определяются

последовательностью входных кодов в

алфавите

![]() .

Составим таблицу наборов настроечныхvi

сигналов

и настроечных функций F

,

cчитая,

что множества G

для

примера равны:

.

Составим таблицу наборов настроечныхvi

сигналов

и настроечных функций F

,

cчитая,

что множества G

для

примера равны:

![]()

![]()

![]()

|

|

|

|

F |

|

0 |

0 |

0 |

F1 |

|

1 |

0 |

0 |

F2 |

|

0 |

1 |

0 |

F3 |

|

1 |

1 |

0 |

F4 |

|

0 |

0 |

1 |

F5 |

|

1 |

0 |

1 |

F6 |

|

0 |

1 |

1 |

F7 |

|

1 |

1 |

1 |

F8 |

Определим

функции

![]() :

:

![]()

![]()

![]()

Определим множества Kij для каждого элемента обобщенной матрицы:

K11 = ; K12 = {1}; K13 = {2,3}; K14 = {2}; K21 = {1};

K22 = ; K23 = {1,2,3}; K24 = {1,3}; K31 = {1,2,3}; K32 = ; K33 = {3};

![]() ;

;

![]()

![]()

![]() ;

;

![]() {1}.

{1}.

Минимизируем функции S1, S1, и S3:

![]()

![]()

![]() .

.

Определим значения элементов

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Обобщенная матрица имеет вид:

По полученной обобщенной матрице R и функциям S строим функциональную схему БН ЛИВС (рис. 9.18). Единичные элементы rij матрицы R, зависящие от настроечного алфавита V, поступают на управляющие входы коммутирующих элементов, которые производят необходимое соединение УРБ по заданной программе.

Одним из возможных способов реализации логического преобразователя является его синтез на основе матричных однородных сред (МОС) [93].

Матричная однородная среда представляет из себя систему вертикальных и горизонтальных информационно-настроечных шин, в местах пересечения которых расположены ячейки среды. Внешними настроечными сигналами ячейки могут быть настроены на одну из следующих пяти операций:

- передача сигнала

с горизонтальной шины на вертикальную

шину без инверсии;

- передача сигнала

с горизонтальной шины на вертикальную

шину без инверсии;

- передача сигнала

с горизонтальной шины на вертикальную

шину с инверсией;

- передача сигнала

с горизонтальной шины на вертикальную

шину с инверсией;

-

передача сигнала с вертикальной шины

на горизонтальную шину без инверсии;

-

передача сигнала с вертикальной шины

на горизонтальную шину без инверсии;

-

передача сигнала с вертикальной шины

на горизонтальную шину с инверсией;

-

передача сигнала с вертикальной шины

на горизонтальную шину с инверсией;

-

отсутствие передачи сигналов между

шинами.

-

отсутствие передачи сигналов между

шинами.

На всех горизонтальных и вертикальных информационных шинах осуществляется операция дизъюнкции сигналов с выходов ячеек среды.

С

(9.24)

![]() .

.

Пусть

LM

- число

функций, которые, необходимо реализовать

в ЛП для вычисления всех текущих значений

элементов обобщенных матриц Аp

и

Аq.

Тогда для

синтеза

ЛП в МОС

потребуется

участок размерами k

вертикальных

и (LM

+

r)

горизонтальных шин. На первые r

горизонтальных

шин подаются

логические

переменные

![]() ,

наk

вертикальных шинах реализуются дизюнкции

,

наk

вертикальных шинах реализуются дизюнкции

![]() на остальных горизонтальных шинах

реализуются функции (9.24).

на остальных горизонтальных шинах

реализуются функции (9.24).

В общем

случае для вычисления

текущих

значений всех элементов матрицы А

в

ЛП

необходимо реализовать N2

функций от переменных

![]() гдеN

- размерность матрицы А.

При

больших N

и

r

сложность

L1

такого ЛП становится весьма значительной.

Рассмотрим возможные методы снижения

сложности ЛП.

гдеN

- размерность матрицы А.

При

больших N

и

r

сложность

L1

такого ЛП становится весьма значительной.

Рассмотрим возможные методы снижения

сложности ЛП.

Так

как не все элементы матрицы А

равны

1, то для вычислений всех текущих значений

элементов матрицы А

ЛП

необходимо

реализовать не N2,

а L(a)

= k,

SN

функций от переменных

![]() ,

гдеS

- число входов УРБ. Если вернуться к

рассмотрению матриц Аp

и

Аq,

то оценка увеличится до

,

гдеS

- число входов УРБ. Если вернуться к

рассмотрению матриц Аp

и

Аq,

то оценка увеличится до

![]() .

.

Интерес представляет оценка числа L* различных задач, на решение которых может быть настроена ЛИВС. Считая, что каждой матрице Аp и Аq соответствует только одна решаемая задача, а разным матрицам соответствуют различные решаемые задачи, число различных задач будет не больше чем

по

числу различных размещений не более

![]() единиц

в

каждой

из N

строк матрицы

единиц

в

каждой

из N

строк матрицы

![]() .

.

Приведем простой пример, поясняющий принцип получения элементов матриц коммутации Аp и Аq.

Пусть ЛИВС предназначена для решения задач a1, a2, a3, a4 и состоит из пяти УРБ. Матрицы коммутации имеют вид

для

всех l

= 1, 2, 3, 4,

для

всех l

= 1, 2, 3, 4,

ЛИВС является комбинационной [22] с алгоритмом функционирования

|

x1 |

x1 |

a |

|

0 0 1 1 |

0 1 0 1 |

a1 a2 a3 A4 |

Тогда в ЛП ЛИВС необходимо реализовать следующие системы переключательных функций (для матрицы Ар):

![]()

![]()

![]()

(9.25)![]()

![]()

![]()

![]()

![]()

Все

остальные элементы матрицы Ap

тождественно равны 0. Для

матрицы Aq

![]() все

остальные элементы равны 0. Систему

функции (9.25) можно реализовать в МОС

размерами 104

ячеек.

все

остальные элементы равны 0. Систему

функции (9.25) можно реализовать в МОС

размерами 104

ячеек.

В

подобном ЛП можно выделить два блока -

синтеза набора конъюнкций

и

синтеза выходных функций .

Сложность первого блока определяется

только значениями r

и

k

и

зависит от набора задач

![]() Уменьшить

размеры участка МОС, отведенного для

реализации этого блока, невозможно

(рис. 9.19).

Уменьшить

размеры участка МОС, отведенного для

реализации этого блока, невозможно

(рис. 9.19).

Сложность

второго блока определяется в

основном

набором решаемых ЛИВС

задач

![]() и

в некоторых случаях размеры участка

МОС, отведенного для реализации этого

блока, могут быть уменьшены.

и

в некоторых случаях размеры участка

МОС, отведенного для реализации этого

блока, могут быть уменьшены.

Так,

если синтезировать систему функции

![]() в

модифицированной

МОС (МОС-М) [22], число необходимых

горизонтальных

шин можно уменьшить почти вдвое, а в

остальных случаях и больше (рис.

9.20).

в

модифицированной

МОС (МОС-М) [22], число необходимых

горизонтальных

шин можно уменьшить почти вдвое, а в

остальных случаях и больше (рис.

9.20).

Puc. 9.19

Рис. 9.20

Для проверки степени усвоения обучающимися материала данной монографии приводим примерный перечень контрольных вопросов (Приложения 1). А для систематической подготовки студентов к междисциплинарному государственному экзамену по специальности 230101 приведена программа указанного экзамена (Приложения 2).