- •В.Ф. Гузик проектирование проблемно - ориентированных вычислительных систем

- •Часть 1

- •Предисловие

- •Производительность суперкомпьютеров

- •Глава первая. Концепция построения многопроцессорных вычислительных систем с программируемой архитектурой (мвс па)

- •Глава вторая. Организация математического обеспечения мвс с программируемой архитектурой

- •2.1. Основы математического обеспечения многопроцессорных вычислительных систем с программируемой архитектурой

- •2.2. Организация машинных языков высокого уровня и технология программирования мвс с программируемой архитектурой

- •2.3. Организация параллельных вычислительных процессов в мвс с программируемой архитектурой

- •Глава третья. Проблемно-ориентированные мвс па

- •3.1.Методика перехода от систем дифференциальных и алгебраических уравнений к системе уравнений Шеннона

- •3.1.1.Представление исходной задачи в форме, удобной для реализации на цифровых интегрирующих машинах (цим)

- •3.1.2. Методика перехода от заданных функций к системе уравнений Шеннона

- •3.1.3. Методика перехода от заданных дифференциальных уравнений к системе уравнений Шеннона

- •3.1.4.Методика перехода от систем линейных алгебраических уравнений к системе уравнений Шеннона

- •3.1.5.Получение программных матриц соединений цифровых решающих модулей

- •3.1.6.Методика перехода от программных матриц к схеме соединения цифровых решающих модулей (црм) в цим с жесткими связями

- •3.2.Примеры структурной организации вычислительного процесса в цим.

- •3.2.1.Задача №1

- •3.2.2.Задача №2

- •3.2.3.Задача №3

- •Приложение 3.2

- •3.2.4.Задача №4

- •3.2.5.Задача №5

- •Глава четвёртая. Теоретические основы построения интегрируЮщих вычислительных структур модульного типа

- •4.1. Общая структурно-логическая схема проектирования (анализа и синтеза) модульных ивс

- •4.2. Представление задач для модульных ивс в операторном пространстве

- •4.3. Построение базиса в операторном -пространстве для ивс модульного типа

- •4.4. Разработка эффективного машинного алгоритма выбора базиса в операторном -пространстве

- •4.5. Математическая модель ивс модульного типа на основе t -алгоритмов

- •4.6. Примеры, иллюстрирующие работу базовой машины ивс

- •Глава пятая. Анализ и синтез универсальных решающих блоков интегрирующих вычислительных структур (ивс)

- •5.1. Синтез алгоритма универсального решающего блока интегрирующих вычислительных структур

- •5.2. Разработка алгоритма автоматического масштабирования переменных и приращений в универсальном решающем блока ивс

- •5.3. Построение структурных схем универсальных решающих блоков ивс с автоматическим масштабированием переменных

- •5.4 Разработка алгоритма универсального решающего блока, основанного на принципе цифрового слежения и синтез его структурной схемы

- •5.5.Проектирование решающей части интегрирующих вычислительных структур

- •Глава шестая. Проектирование функциональных модулей интегрирующих вычислительных структур

- •6.1. Исследование принципов построения коммутационных систем модульных интегрирующих вычислительных структур

- •6.2. Разработка волновых каскадных коммутирующих сред для интегрирующих вычислительных структур

- •6.3. Принципы построения цифровых решающих и функциональных модулей ивс

- •6.4.Определение параметров функциональных модулей интегрирующих вычислительных структур

- •6.5.Матричное представление функциональных модулей интегрирующих вычислительных структур

- •6.6. Построение специализированного микропроцессора интегрирующей вычислительной структуры

- •Глава седьмая. Система математического обеспечения модульных интегрирующих вычислительных структур

- •7.1. Структура системы математического обеспечения модульных ивс

- •7.2. Разработка языка структурного программирования высокого уровня для модульных ивс

- •7.3.Разработка транслятора, загрузчика и диспетчера системы программного обеспечения модульных ивс

- •7.4. Построение пакета системных программ для программного обеспечения ивс

- •7.5. Организация вычислительных процессов в модульных ивс

- •Глава восьмая. Однородные цифровые интегрирующие структуры

- •8.1. Цифровые интеграторы для оцис

- •8.2. Интерполяционные и экстраполяционные, одноразрядные и многоразрядные однородные цифровые интегрирующие структуры

- •Глава девятая. Примеры проектирования проблемно- ориентированных мвс на интегрирующих структурах

- •9.1. Моделирующий вычислительный комплекс для исследования систем инерциальной навигации на основе модульных ивс

- •9.2. Применение интегрирующих вычислительных структур для реализации систем управления манипуляционными устройствами автономных роботов

- •9.3. Специализированная вычислительная система для решения задач управления с прогнозированием

- •9.4. Логико-интегрирующие вычислительные структуры

- •Приложение 1 Примерный перечень

- •Министерство образования и науки российской федерации

- •Курс «Технология программирования»

- •Практические задания

- •Курс «Интерфейсы периферийных устройств»

- •Курс «Конструкторско-технологическое обеспечение производства эвм»

- •Библиографический список

- •Оглавление

6.3. Принципы построения цифровых решающих и функциональных модулей ивс

Основной архитектурной единицей интегрирующих вычислительных структур являются функциональные модули, представляющие собой определенное количество универсальных решающих блоков [36] и объединенные между собой коммутирующей средой различной степени универсальности, которые предназначены для реализации базисных T-операторов ИВС [31]. Функциональные модули должны обладать такой структурой, которая была бы способна к реализации либо любого базисного оператора ИВС, либо к реализации некоторой последовательности операторов. Следовательно, базис операторов определяет как структуру ФМ, так и структуру его автомата управления, обеспечивающего переходы при настройке ФМ при реализации последовательности операторов.

С другой стороны, при анализе класса решаемых задач на ИВС можно методами, приведенными в работе [31] , рассчитать основные параметры ФМ, к которым относятся:

1) сложность модуля N - число УРБ в модуле;

2) количество побочных T-операторов m, которые реализуются на данном ФМ одновременно с реализацией основного Т-оператора от одного и того же аргумента. Параметры ФМ также определяют его структуру, но с точки зрения класса решаемых задач.

Так как процедура выбора базиса Т-операторов и методика расчета основных параметров ФМ непосредственно вытекают из анализа класса решаемых на ИВС задач, то оба приведенных выше критерия взаимно влияют на структуру функциональных модулей.

Исходя из понятий "жесткой" и "гибкой" модели Т-операторов, введенных в разделе 4.2, можно представить три вида функциональных модулей:

1) модули, функционирующие в относительном времени;

![]() ,...,

где

,...,

где

![]() ,

такие

ФМ не меняют своей внутренней структуры,

т.е. это неперестраиваемые ФМ;

,

такие

ФМ не меняют своей внутренней структуры,

т.е. это неперестраиваемые ФМ;

![]() означает тот факт, что ни за какой

конечный промежуток времени

означает тот факт, что ни за какой

конечный промежуток времени

![]() ФМ

не изменит внутренней структуры, т.е. в

ФМ нет управления настройкой, отсутствует

внутренняя память, логическая часть

обладает полнотой связей;

ФМ

не изменит внутренней структуры, т.е. в

ФМ нет управления настройкой, отсутствует

внутренняя память, логическая часть

обладает полнотой связей;

2) модули, функционирующие в дискретном автоматном времени:

![]() ,

т.е. такие ФМ, которые обладают способностью

к перестройке внутренней структуры, но

они не имеют внутренней памяти; ФМ

может

менять внутреннюю структуру в дискретные

моменты времени tj

= k,

если при этом образование конфигурации

окончено и от базовой машины

,

т.е. такие ФМ, которые обладают способностью

к перестройке внутренней структуры, но

они не имеют внутренней памяти; ФМ

может

менять внутреннюю структуру в дискретные

моменты времени tj

= k,

если при этом образование конфигурации

окончено и от базовой машины

![]() [32]

не

получены запрещающие сигналы;

[32]

не

получены запрещающие сигналы;

3) модули,

функционирующие в непрерывном времени

![]() ,

в частности, если

,

в частности, если![]() ,

то модульное время представляется

последовательностью нулей и единиц,

т.е. двоичными кодами, которые могут

быть определенным образом связаны с

состояниями ФМ; ФМ обладают способностью

к внутренней перестройке и имеют память

состояний. Здесь возможна различного

рода адаптация к различным внешним

воздействиям, образование макромодулей

и относительно простое самовоспроизведение

в смысле [36] , которое, например, выразится

как передача информации из памяти одного

ФМ в память другого и обмен информацией

между рабочими регистрами модулей. На

основе проведенных рассуждений можно

представить укрупненную

структурную схему функционального

модуля.

,

то модульное время представляется

последовательностью нулей и единиц,

т.е. двоичными кодами, которые могут

быть определенным образом связаны с

состояниями ФМ; ФМ обладают способностью

к внутренней перестройке и имеют память

состояний. Здесь возможна различного

рода адаптация к различным внешним

воздействиям, образование макромодулей

и относительно простое самовоспроизведение

в смысле [36] , которое, например, выразится

как передача информации из памяти одного

ФМ в память другого и обмен информацией

между рабочими регистрами модулей. На

основе проведенных рассуждений можно

представить укрупненную

структурную схему функционального

модуля.

На основе общей теории цифровых интегрирующих машин и структур [76], используя универсальные цифровые интеграторы, строятся универсальные решающие блоки [36] и цифровые решающие модули (ЦРМ), в состав которых включается один УЦИ и коммутатор. В УРБ коммутатор вырождается в систему клапанов, обеспечивающих соединение операционных устройств УЦИ для выполнения заданного набора операций; в ЦРМ, состоящем из УРБ и коммутатора, имеется возможность производить настройку УРБ на заданные операции и обеспечивать коммутацию ЦРМ между собой при решении конкретной задачи.

Структурная схема ЦРМ, представляющего собой "вырожденный" функциональный модуль, изображена на рис. 6.9.

Недостатком таких функциональных модулей является то, что они допускают настройку только на элементарные структурные операции и коммутацию. Так, например, ЦРМ настраивается только на операции суммирования приращений, цифрового интегрирования, слежения, логических функций ограничения и знака и функциональные зависимости – возведения в квадрат и экспоненциальную зависимость.

Для построения модульных интегрирующих вычислительных структур необходимо синтезировать "универсальный" функциональный модуль, который мог бы настраиваться на сложные операции и функции из выбранного базиса T-операторов операторного -пространства. Здесь слово «универсальный» взято в кавычки, так как универсальность понимается в смысле класса решаемых на ИВС задач.

На рис. 6.10 представлена структурная схема "универсального" ФМ (структура ФМ), удовлетворяющая перечисленным выше требованиям и описанию математической модели функционального модуля, приведённого в разделе модуля 4.5 (4.21).

Рис. 6.9 Структурная схема "вырожденного" функционального модуля ИВС

Рис. 6.10 Структурная схема „универсального" функционального модуля ИВС

Наиболее простым, как отмечено выше, является функциональный модуль, процессорная часть которого содержит один универсальный решающий блок ЦИС. Такой ФМ назван цифровым решающим модулем или по аналогии с понятием "универсальный" ФМ – "вырожденным" ФМ.

Цифровые решающие модули нашли широкое применение при построении однородных цифровых интегрирующих структур [12,36], а также при создании специализированных модульных ИВС [37, 40, 49, 51, 55, 62, 71, 72, 73, 74].

Если взять коммутирующие элементы, разработанные выше для плоских структур, то, исходя из структурной схемы УРБ (рис. 5.1, 5.8), можно представить структурную схему цифрового решающего модуля ОЦИС, оперирующего с одноразрядными приращениями так, как это показано на рис. 6.11. Причем для простоты УРБ на этом рисунке окружен одним слоем коммутирующих элементов.

По аналогии с цифровым решающим модулем, построенным на основе структурной схемы УРБ, можно строить ЦРМ, включающий в свой состав УРБ, реализующие любые наборы математических операций и оперирующие как с одноразрядными, так и многоразрядными приращениями.

На основе обобщенной структурной схемы (рис. 6.11) разработан цифровой решающий модуль (рис. 6.12) для специализированной ИВС, в основу которого положен универсальный решающий блок.

Входной

коммутатор

![]() задает

соединения входов подынтегральных

функцийРi

и входа переменной интегрирования q

решающего блока П

с любым из каналов связи а1...

a8.

Выходной

коммутатор

задает

соединения входов подынтегральных

функцийРi

и входа переменной интегрирования q

решающего блока П

с любым из каналов связи а1...

a8.

Выходной

коммутатор

![]() определяет любые соединения входных

полюсова1...

a4

с

выходными полюсами b1...

b4

и

путь дальнейшей передачи настроечного

кода. Местное

устройство управления (МУУ) синхронизирует

во времени работу всех узлов ЦРМ в

соответствии с сигналами, поступающими

с центрального устройства управления

ИВС, а также устанавливает режим настройки

(РН) ЦРМ.

определяет любые соединения входных

полюсова1...

a4

с

выходными полюсами b1...

b4

и

путь дальнейшей передачи настроечного

кода. Местное

устройство управления (МУУ) синхронизирует

во времени работу всех узлов ЦРМ в

соответствии с сигналами, поступающими

с центрального устройства управления

ИВС, а также устанавливает режим настройки

(РН) ЦРМ.

С помощью узла выбора режима настройки (УРН) устанавливаются следующие режимы настройки ЦРМ:

PH1 – упорядоченная выборка – настроечный код поступает на выбранный ЦРМ по информационным каналам модуля а1...а4;

РН2 – произвольная выборка – настроечный код поступает на выбранный ЦРМ по шине "Код Н", а номер модуля задается сигналом "Адрес ЦРМ";

РН3 – смешанный режим настройки – настроечный код поступает на выбранный ЦРМ по шине "Код Н", а далее следует по одной из информационных шин b1... b4 в зависимости от программы настройки.

Рис. 6.11. Структурная

схема цифрового решающего модуля

Рис. 6.12. Структурная схема цифрового решающего модуля

В ЦРМ имеются три регистра для приема и хранения настроечной информации.

Регистр RG1 служит для приема настроечной информации, определяющей соединения входов решающего блока П с соответствующими информационными каналами a1... a8 (т.е. управляет входным коммутатором).

Регистр

RG2

содержит

информацию, определяющую настройку УРБ

на выполнение определенной операции,

путь передачи приращений

![]() (по

каналам b1...

b4)

и признаки инверсии, указывающие на

необходимость инвертирования приращений,

поступающих на входы q

и pi.

(по

каналам b1...

b4)

и признаки инверсии, указывающие на

необходимость инвертирования приращений,

поступающих на входы q

и pi.

Регистр RG3 служит для приема информации, определяющей состояние выходного коммутатора.

Узел контроля (УК) предназначен для проверки правильности кодов настройки, поступающих в регистры RG1, RG2, RG3, и выдачи сигнала "Ошибка" в случае отклонения кодов от нормы или сбоев в регистрах. С помощью узлов У1, У2, УЗ осуществляется автоматическое поочередное подключение входов регистров RG1, RG2, RG3 к каналу связи.

На основании структурной схемы ФМ (рис. 6.10) разработаны функциональная и принципиальная схемы универсального функционального модуля.

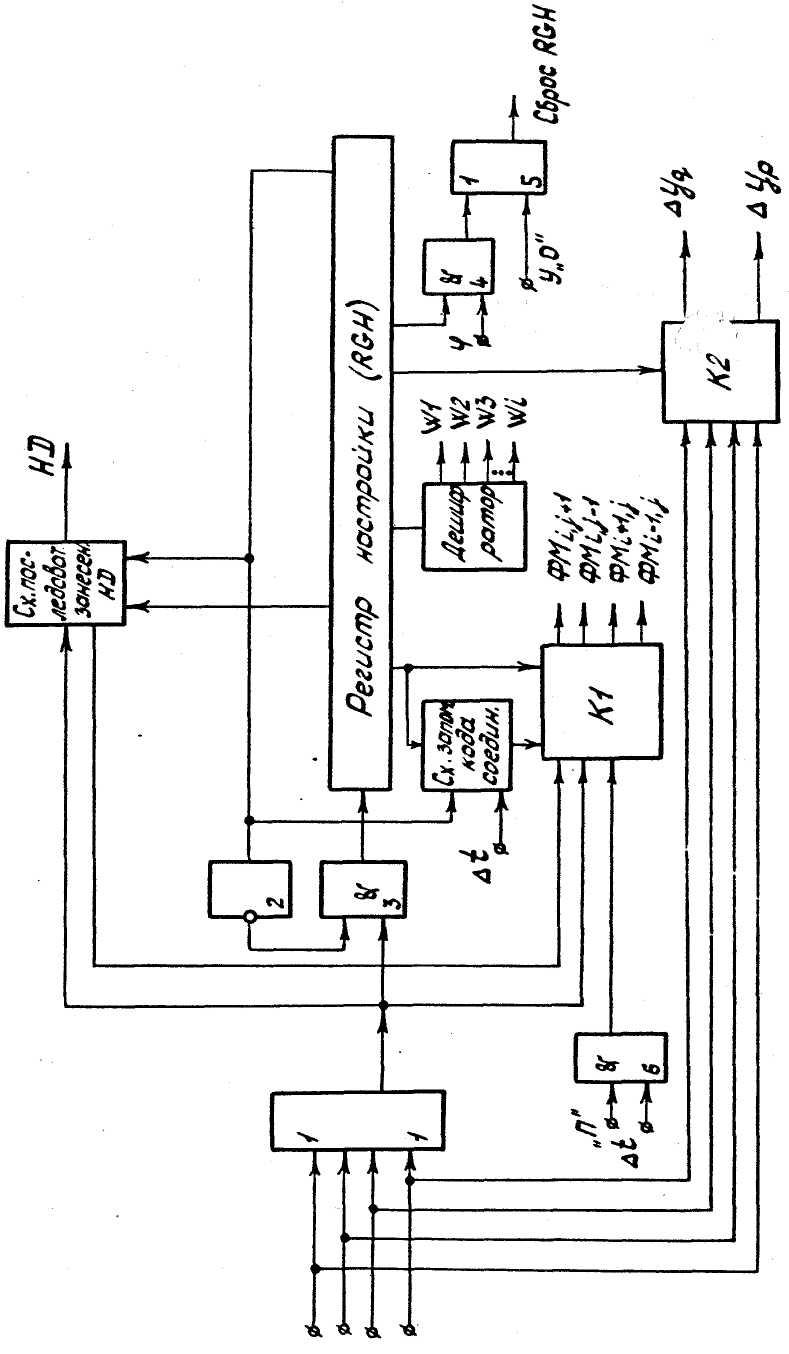

Работой ФМ управляет местное устройство управления, состоящее из блока настройки (БН) и коммутатора (К). Если представить формат команды настройки ФМ в виде, изображенном на рис. 6.13, то структурная схема местного устройства управления примет вид, приведенный на рис. 6.15.

Рассмотрим работу МУУ ФМ, пользуясь приведенным форматом команды настройки. В начальный момент производится занесение настроечной информации в регистр настройки модуля (RGH). Момент окончания занесения фиксируется появлением "I" в служебном разрядe RGH. В этот момент, в соответствии с кодом соединения настраиваемого ФМ с другими модулями, осуществляется подготовка коммутатора K1 и передача настроечной информации в следующее ФМ. Дешифратором, в соответствии с кодом настройки на реализацию функции fi(x), вырабатывается сигнал Wi, который посылается в процессор ФM. Коммутатор К2 подготавливается к передаче сигналов с выходов других ФM на входы yq, yp в процессор настраиваемого модуля.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Код ком-мутации с другими ФМ |

Код

функции

|

Код

подачи входных сигналов на шину

|

Код необхо-димого количества ФМ |

Признак разветв-ления |

Служеб-ный разряд |

Рис. 6.13. Формат команды настройки ФМ

Служебный разряд RGH используется для сброса регистра настройки в "О", когда от настраиваемого ФM имеется разветвление. В этом случае последовательно настраиваются все ветвящиеся пути. Перед началом настройки очередного ветвления регистр настройки сбрасывается в нуль, чтобы иметь возможность записать в него новый код коммутации с другими ФM. Каждый раз с появлением единицы в служебном разряде регистра код коммутации записывается в схему запоминания, где хранится в процессе решения задачи. В режиме решения (при t = 1) вся хранящаяся в этой схеме информация поступает на коммутатор K1 и тем самым обеспечивается соединение настроенного ФМ по всем направлениям. В режиме решения схема сборки 1 отсоединяется от коммутатора K1 и к нему подключается выход процессора ФM.

После занесения настроечной информации в RGH будут последовательно поступать начальные данные (НД). Схема последовательного занесения НД обеспечивает поочередное поступление НД в регистры Y УРБ ФМ. После занесения всех начальных данных схема занесения НД открывает коммутатор K1, а сама отключается. На этом заканчивается настройка данного ФМ и информация через коммутатор K1 поступает в другие ФМ.

Рис. 6.14. Структурная схема процессора ФМ

Пользуясь общей структурной схемой ФM (рис. 6.10), приведем пример построения ФМ с N = Nmax = 5 , где N – количество УРБ в функциональном модуле, структурная схема для которого представлена на рис. 6.16. Входная логика обеспечивает связь ФМ с другими модулями и с управляющим автоматом ИВС для настройки модуля. На вход управляющего автомата ФМ подаются сигналы, соответствующие реализациям базисных операторов ИВС.

Рис. 6.15. Структурная

схема процессора МУУ ФМ

Например, для

заданной S

R

(табл. C,

раздел 4.1) на вход УА подаются слова вида

![]() ,

,

![]() ,

где

,

где

![]()

{0,1}

так как modS

= 28. Исходя

из этого, функциональную схему УА можно

представить так, как это показано на

рис. 6.17. Выходы дешифратора (ДШ) 1, 2

возбуждаются при реализации оператора

с Ni

= 1, выходы

ДШ (3-8) – при реализации оператора с Ni

= 2 ; выходы ДШ (9-17) – при реализации

оператора c

Ni

= 3; выходы ДШ (18-25) – при реализации

оператора с Ni

= 4; выходы ДШ (26-27) – при реализации

оператора с Ni

= 5. Триггер

T1

устанавливает исходное состояние ФМ и

режим его работы.

{0,1}

так как modS

= 28. Исходя

из этого, функциональную схему УА можно

представить так, как это показано на

рис. 6.17. Выходы дешифратора (ДШ) 1, 2

возбуждаются при реализации оператора

с Ni

= 1, выходы

ДШ (3-8) – при реализации оператора с Ni

= 2 ; выходы ДШ (9-17) – при реализации

оператора c

Ni

= 3; выходы ДШ (18-25) – при реализации

оператора с Ni

= 4; выходы ДШ (26-27) – при реализации

оператора с Ni

= 5. Триггер

T1

устанавливает исходное состояние ФМ и

режим его работы.

Блок настройки производит коммутацию УРБ в модуле на основании микропрограммы реализации базисных операторов. Если коммутацию строить по полному графу, то необходимо иметь КС из К = 2N2 + 3N коммутирующих элементов. При реализации операторов используются не все КЭ КС, следовательно, необходимо произвести минимизацию КЭ. Это делается на основе анализа матриц коммутации Ар и Аq базисных операторов ИВС.

Пусть заданы матрицы коммутации операторов:

где столбец с номером m = 0 указывает на связь данного ФМ с выходами других ФМ; столбец с m = j учитывает связь выхода данного ФМ со входами других ФМ.

Тогда для определения количества коммутирующих элементов, необходимых для реализации коммутации только базисных операторов, производим дизъюнкцию i-го столбца матрицы Rp (или Rq) одного из множества операторов с i-столбцом других матриц базисных операторов,

Рис. 6.16. Структурная схема ФМ ИВС

Рис. 6.17. Функциональная схема управляющего автомата

т.е.

![]() где

где

![]() (дляRp)

и

(дляRp)

и

![]() (для Rq),

m

– число

матриц базисных операторов. Для системы

(для Rq),

m

– число

матриц базисных операторов. Для системы

![]() определяем

определяем

![]() и число k

коммутирующих элементов.

и число k

коммутирующих элементов.

Тогда структурная схема процессора ФМ (при N = 3) будет иметь вид, приведенный на рис. 6.14, а полная структурная схема функционального модуля для рассматриваемого примера (N = Nmax = 5) дана на рис. 6.18.

Рис. 6.18. Структурная схема функционального модуля

Рассмотрим

методику настройки процессора ФМ

на

выполнение любой из обобщенных

прямоугольных матриц

![]() ,

реализующих базисные Тi

-операторы,

где

,

реализующих базисные Тi

-операторы,

где

![]() –

входы по подынтегральной функции

–

входы по подынтегральной функции

![]() –

входы по переменной интегрирования уq

УРБ.

–

входы по переменной интегрирования уq

УРБ.

Обозначим

единичные элементы матриц

![]() ,

стоящие на пересечении строк

,

стоящие на пересечении строк

![]() и

и

![]() и столбцов

и столбцов![]() через

через

![]() и

и

![]() .

Наличие единичного элемента в той или

иной строке соответствует появлению

выходных приращений

.

Наличие единичного элемента в той или

иной строке соответствует появлению

выходных приращений![]() -го

УРБ на входах

-го

УРБ на входах![]() или

или![]() Так как приращения на входахj-го

УРБ появляются только в том случае,

когда выполняется оператор Ti,

то можно сказать, что единичный

элемент матрицы

Так как приращения на входахj-го

УРБ появляются только в том случае,

когда выполняется оператор Ti,

то можно сказать, что единичный

элемент матрицы

![]() определяется совпадением двух событий:

входным приращением

Z

и сигналом Wi,

определяющим необходимость решения

базисной функции Тi

в данный момент времени (рис. 6.15):

определяется совпадением двух событий:

входным приращением

Z

и сигналом Wi,

определяющим необходимость решения

базисной функции Тi

в данный момент времени (рис. 6.15):

(6.1)

Согласно выражению

(6.1) при образовании обобщенной матрицы

R

каждый ее единичный элемент

![]() и

и![]() ,

стоящий на пересечении

,

стоящий на пересечении![]() строки и-го

столбца, равен логической сумме единичных

элементов матриц

строки и-го

столбца, равен логической сумме единичных

элементов матриц

![]() ,

стоящих на пересечении тех же строк и

столбцов:

,

стоящих на пересечении тех же строк и

столбцов:

(6.2)

Поскольку значение приращения Z не зависит от значения i, то его можно вынести за знак логической суммы:

(6.3)

В общем случае в

каждой строке матрицы R

может стоять не более Вimax

единичных элементов. Поэтому система

коммутации процессора ФМ по входам

![]() и

и![]() j-х

с УРБ описывается следующими

уравнениями:

j-х

с УРБ описывается следующими

уравнениями:

(6.4)

Подставляя вместо

![]() и

и![]() их значение из (6.3), в окончательном виде

получим

их значение из (6.3), в окончательном виде

получим

(6.5)

Макетирование предложенных ФМ и имитация режима настройки с упорядоченной выборкой элементов подтвердили целесообразность построения ИВС на основе функциональных модулей как с точки зрения уменьшения затрат оборудования, повышения надежности ИВС, так и с точки зрения упрощения процесса программирования и настройки.