- •В.Ф. Гузик проектирование проблемно - ориентированных вычислительных систем

- •Часть 1

- •Предисловие

- •Производительность суперкомпьютеров

- •Глава первая. Концепция построения многопроцессорных вычислительных систем с программируемой архитектурой (мвс па)

- •Глава вторая. Организация математического обеспечения мвс с программируемой архитектурой

- •2.1. Основы математического обеспечения многопроцессорных вычислительных систем с программируемой архитектурой

- •2.2. Организация машинных языков высокого уровня и технология программирования мвс с программируемой архитектурой

- •2.3. Организация параллельных вычислительных процессов в мвс с программируемой архитектурой

- •Глава третья. Проблемно-ориентированные мвс па

- •3.1.Методика перехода от систем дифференциальных и алгебраических уравнений к системе уравнений Шеннона

- •3.1.1.Представление исходной задачи в форме, удобной для реализации на цифровых интегрирующих машинах (цим)

- •3.1.2. Методика перехода от заданных функций к системе уравнений Шеннона

- •3.1.3. Методика перехода от заданных дифференциальных уравнений к системе уравнений Шеннона

- •3.1.4.Методика перехода от систем линейных алгебраических уравнений к системе уравнений Шеннона

- •3.1.5.Получение программных матриц соединений цифровых решающих модулей

- •3.1.6.Методика перехода от программных матриц к схеме соединения цифровых решающих модулей (црм) в цим с жесткими связями

- •3.2.Примеры структурной организации вычислительного процесса в цим.

- •3.2.1.Задача №1

- •3.2.2.Задача №2

- •3.2.3.Задача №3

- •Приложение 3.2

- •3.2.4.Задача №4

- •3.2.5.Задача №5

- •Глава четвёртая. Теоретические основы построения интегрируЮщих вычислительных структур модульного типа

- •4.1. Общая структурно-логическая схема проектирования (анализа и синтеза) модульных ивс

- •4.2. Представление задач для модульных ивс в операторном пространстве

- •4.3. Построение базиса в операторном -пространстве для ивс модульного типа

- •4.4. Разработка эффективного машинного алгоритма выбора базиса в операторном -пространстве

- •4.5. Математическая модель ивс модульного типа на основе t -алгоритмов

- •4.6. Примеры, иллюстрирующие работу базовой машины ивс

- •Глава пятая. Анализ и синтез универсальных решающих блоков интегрирующих вычислительных структур (ивс)

- •5.1. Синтез алгоритма универсального решающего блока интегрирующих вычислительных структур

- •5.2. Разработка алгоритма автоматического масштабирования переменных и приращений в универсальном решающем блока ивс

- •5.3. Построение структурных схем универсальных решающих блоков ивс с автоматическим масштабированием переменных

- •5.4 Разработка алгоритма универсального решающего блока, основанного на принципе цифрового слежения и синтез его структурной схемы

- •5.5.Проектирование решающей части интегрирующих вычислительных структур

- •Глава шестая. Проектирование функциональных модулей интегрирующих вычислительных структур

- •6.1. Исследование принципов построения коммутационных систем модульных интегрирующих вычислительных структур

- •6.2. Разработка волновых каскадных коммутирующих сред для интегрирующих вычислительных структур

- •6.3. Принципы построения цифровых решающих и функциональных модулей ивс

- •6.4.Определение параметров функциональных модулей интегрирующих вычислительных структур

- •6.5.Матричное представление функциональных модулей интегрирующих вычислительных структур

- •6.6. Построение специализированного микропроцессора интегрирующей вычислительной структуры

- •Глава седьмая. Система математического обеспечения модульных интегрирующих вычислительных структур

- •7.1. Структура системы математического обеспечения модульных ивс

- •7.2. Разработка языка структурного программирования высокого уровня для модульных ивс

- •7.3.Разработка транслятора, загрузчика и диспетчера системы программного обеспечения модульных ивс

- •7.4. Построение пакета системных программ для программного обеспечения ивс

- •7.5. Организация вычислительных процессов в модульных ивс

- •Глава восьмая. Однородные цифровые интегрирующие структуры

- •8.1. Цифровые интеграторы для оцис

- •8.2. Интерполяционные и экстраполяционные, одноразрядные и многоразрядные однородные цифровые интегрирующие структуры

- •Глава девятая. Примеры проектирования проблемно- ориентированных мвс на интегрирующих структурах

- •9.1. Моделирующий вычислительный комплекс для исследования систем инерциальной навигации на основе модульных ивс

- •9.2. Применение интегрирующих вычислительных структур для реализации систем управления манипуляционными устройствами автономных роботов

- •9.3. Специализированная вычислительная система для решения задач управления с прогнозированием

- •9.4. Логико-интегрирующие вычислительные структуры

- •Приложение 1 Примерный перечень

- •Министерство образования и науки российской федерации

- •Курс «Технология программирования»

- •Практические задания

- •Курс «Интерфейсы периферийных устройств»

- •Курс «Конструкторско-технологическое обеспечение производства эвм»

- •Библиографический список

- •Оглавление

7.5. Организация вычислительных процессов в модульных ивс

Рассмотрим вначале общую процедуру организации вычислительных процессов в модульных ИВС. Под организацией вычислительных процессов в модульных ИВС будет пониматься процесс настройки системы ПО ИВС на определенный круг задач, подготовка задачи к решению на ИВС (трансляция и загрузка модулей ИВС), а также управление ходом вычислительного процесса при решении исходной задачи. Настройка системы ПО и подготовка задачи к решению выполняются с помощью блока специальных системных программ, который различным образом коммутируется с помощью диспетчера с остальными программами системы ПО ИВС. Управление вычислительным процессом в ИВС строится на основе сетей Петри, которые используются в модифицированном виде, учитывая специфический способ представления задач в ИВС [34, 118].

Таблица 7.3

|

IP |

KР |

MV |

|

|

4 5 7 6 11 41 32 42 34 39 33 28 22 29 24 38 37 36 8

501 502 503 504 505 506 507 |

M1 M2 M3 M4 M5 М6 M7 M8 M9 M10 M11 M12 M13 M14 M15 M16 M17 M18 M19

M20 M21 M22 M23 M24 M25 M26 |

Настройка системы ПО ИВС при подготовке задачи к решению сводится к следующим этапам:

1) произвести декомпозицию задачи с целью получения исходных данных для программ символьного дифференцирования;

выработать с помощью программы символьного дифференцирования системную библиотеку схем Шеннона для реализации операторов, которая является основной частью формирования команд УРБ при настройке ФМ ИВС, и подготовить исходные данные для программ определения операторного базиса и подготовки данных для расчета начальных значений переменных, используемых в задаче;

определить операторный базис на основе информации, поступающей с выхода программы символьного дифференцирования в форме, представленной на рис. 7.13, где

–

основное значение операции или функции;

ФВi

– вспомогательное

значение операции или функция для

данной задачи (или круга задач), представив

его в виде набора функций и операций,

и передать его в компилятор ИВС в виде

таблицы используемых символов.

–

основное значение операции или функции;

ФВi

– вспомогательное

значение операции или функция для

данной задачи (или круга задач), представив

его в виде набора функций и операций,

и передать его в компилятор ИВС в виде

таблицы используемых символов.

При непосредственной подготовке исходной задачи к решению на ИВС система ПО работает следующим образом. На вход компилятора поступает задача, записанная на ЯП ИВС, после чего она проходит этапы лексического, синтаксического и семантического анализа. На выходе компилятора генерируется объектный код в виде тетрад (рис. 7.14), которые представлены в ИВС как

![]() ,

,

где

![]() –

имя функции/операции, содержащейся в

i-й

тетраде;

–

имя функции/операции, содержащейся в

i-й

тетраде;

![]() – адрес

микропрограммы (схемы Шеннона в

библиотеке) для реализации функции/операции

в i-ой

тетраде;

– адрес

микропрограммы (схемы Шеннона в

библиотеке) для реализации функции/операции

в i-ой

тетраде;

![]() –

номер тетрады, на которую переключается

ход вычислений при выполнении заданного

условия (ТЕТ

= 0,

если тетрада имеет код, соответствующий

функции/операции);

–

номер тетрады, на которую переключается

ход вычислений при выполнении заданного

условия (ТЕТ

= 0,

если тетрада имеет код, соответствующий

функции/операции);

![]() –

адрес первого операнда в таблице символов

компилятора (таблица TS

);

–

адрес первого операнда в таблице символов

компилятора (таблица TS

);

![]() –

адрес второго операнда тетрады в таблице

символов; МI(i,

3)

–

адрес

результата в таблице символов (ТS).

Адреса

микропрограмм указываются с учетом

выбранного операторного базиса.

–

адрес второго операнда тетрады в таблице

символов; МI(i,

3)

–

адрес

результата в таблице символов (ТS).

Адреса

микропрограмм указываются с учетом

выбранного операторного базиса.

Объектный

код на выходе компилятора разделяется

на три части. Функциональная часть кода

–

![]() и

и

![]() поступает

на вход генератора команд УРБ, где при

взаимодействии с библиотекой схем

Шеннона формируется набор команд для

коммутации УРБ в ФМ с целью реализации

данного оператора (задаваемого

поступает

на вход генератора команд УРБ, где при

взаимодействии с библиотекой схем

Шеннона формируется набор команд для

коммутации УРБ в ФМ с целью реализации

данного оператора (задаваемого![]() ).

Выходом генератора является список

соединения УРБ в ФМ или матрица коммутации

УРБ, соответствующая данной,

).

Выходом генератора является список

соединения УРБ в ФМ или матрица коммутации

УРБ, соответствующая данной,![]() ,

функциональной части кода.

,

функциональной части кода.

Рис. 7.13. Вид информации для программы базиса

Рис. 7.14. Формат объектного кода ИВС

Элементы

объектного кода

![]() ,

,

![]() ,

,![]() поступают также на вход программы

подготовки данных для расчета начальных

значений как для всех используемых ФМ,

так и для всех УРБ в ФМ, с помощью таблицы,

передаваемой из программы аналитического

дифференцирования на этапе настройки

ПО ИВС. Расчет может проводиться как в

автономном

режиме,

так и в режиме сопряжения с ЦВМ. Во втором

случае рассчитанные начальные значения

передаются в диспетчер для последующего

формирования загрузочного модуля.

поступают также на вход программы

подготовки данных для расчета начальных

значений как для всех используемых ФМ,

так и для всех УРБ в ФМ, с помощью таблицы,

передаваемой из программы аналитического

дифференцирования на этапе настройки

ПО ИВС. Расчет может проводиться как в

автономном

режиме,

так и в режиме сопряжения с ЦВМ. Во втором

случае рассчитанные начальные значения

передаются в диспетчер для последующего

формирования загрузочного модуля.

Передача информации из программы символьного дифференцирования в программу выбора базиса и программу расчета начальных значений происходит через диспетчер в следующем виде (рис. 7.14):

![]() .

.

При формировании библиотеки схем Шеннона с помощью программы дифференцирования матрица коммутации УРБ имеет строки вида (рис. 7.15)

![]() ,

,

где

![]() -

код операции, выполняемой данным УРБ;

-

код операции, выполняемой данным УРБ;![]()

номер УРБ, выход которого подается на

1-й вход i-го

УРБ;

номер УРБ, выход которого подается на

1-й вход i-го

УРБ;

![]()

номер УРБ, выход которого подается на

2-й вход i-го

УРБ;

номер УРБ, выход которого подается на

2-й вход i-го

УРБ;

![]()

номер УРБ, являющегося 1-м входом

данного ФМ;

номер УРБ, являющегося 1-м входом

данного ФМ;

![]()

номер УРБ, являющегося 2-м входом данного

ФМ;

номер УРБ, являющегося 2-м входом данного

ФМ;

![]() -

номер УРБ, являющегося выходом данного

ФМ.

-

номер УРБ, являющегося выходом данного

ФМ.

Адресная

часть тетрады, определяющая коммутацию

ФМ, подается через диспетчер на вход

загрузчика, который осуществляет

программирование структуры ФМ

на

реализацию заданного оператора –

![]() и коммутацию ФМ. Совместно с диспетчером

формируется загрузочный модуль из

функциональной части тетрады,

преобразованной генератором команд

УРБ и коммутационной информации (рис.

7.16), представленной в виде

и коммутацию ФМ. Совместно с диспетчером

формируется загрузочный модуль из

функциональной части тетрады,

преобразованной генератором команд

УРБ и коммутационной информации (рис.

7.16), представленной в виде![]() ,

где

,

где

![]()

порядковый номер ФМ, выход которого

подается на 1-й вход i-гo

ΦМ,:

порядковый номер ФМ, выход которого

подается на 1-й вход i-гo

ΦМ,:

![]()

порядковый номер ФМ, выход которого

подается на 2-й вход i-го

ФМ. После чего происходит загрузка

модуля в

ИВС

и

решение

задачи.

порядковый номер ФМ, выход которого

подается на 2-й вход i-го

ФМ. После чего происходит загрузка

модуля в

ИВС

и

решение

задачи.

Puc. 7.15. Представление матрицы коммутации РБ в ФМ ИВС

Рис. 7.16. Вид информации для соединений ФМ ИВС

при загрузке

В диспетчере информация, поступающая от отдельных подпрограмм, формируется в загрузочный модуль (рис. 7.17, 7.18), который затем настра-ивается на ФМ ИВС и далее происходит решение исходной задачи. Диспетчер производит управление работой программ ПО ИВС и используется для сбора информации о времени обработки задач всей системой и каждым блоком в отдельности.

Рис. 7.17. Загрузочный

модуль ИВС

Рис. 7.18. Часть загрузочного модуля (для одного ФМ ИВС)

Рис. 7.19. Взаимодействие модулей ПО ИВС

Если в качестве УРБ в ФМ ИВС используются блоки с автоматическим масштабированием [26], то в системе ПО ИВС не используется блок масштабирования. При применении в ИВС УРБ с фиксированной запятой необходимо включить в общую структуру системы ПО ИВС блок масштабирования, который функционирует и коммутируется с другими блоками ПО.

Схема взаимодействия блоков системы ПО ИВС представлена на рис. 7.19, где заштрихованными стрелками обозначено взаимодействие при подготовке задачи к решению на ИВС, не заштрихованными – процесс настройки системы.

Представление и описание вычислительного процесса в модульных ИВС в формальном виде можно произвести различными способами с использованием различных математических аппаратов в зависимости от способов синхронизации параллельных вычислений в ИВС. Рассмотрим формальные модели представления и организации параллельных вычислительных процессов при синхронном и асинхронном принципах управления параллельными процессами.

Для формального описания вычислительного процесса в ИВС введем следующие определения [35, 84].

О п р е д е л е н и е 1. Под вычислительным процессом в ИВС понимается структурная реализация заданного множества алгоритмов решения задач, развернутая в пространстве и во времени.

При

использовании операторной схемы

представления задач в ИВС, которая

получается на выходе транслирующего

алгоритма

![]() и

интерпретируется как объектная программа

ИВС, вычислительный процесс рассматривается

как выражение вида

и

интерпретируется как объектная программа

ИВС, вычислительный процесс рассматривается

как выражение вида

![]() ,

,

где

![]()

последовательность Τ-операторов

на выходе

последовательность Τ-операторов

на выходе

![]() ;

;

![]()

граф коммутации

микропроцессоров, полученный в результате

трансляции задачи;

граф коммутации

микропроцессоров, полученный в результате

трансляции задачи;

![]() -

вектор управляющих сигналов, обеспечивающих

перестройку микропроцессоров во времени

;

-

вектор управляющих сигналов, обеспечивающих

перестройку микропроцессоров во времени

;

![]() -абстрактное

автоматное время [29, 30, 32].

-абстрактное

автоматное время [29, 30, 32].

Теоретико-множественный подход позволяет получать операторное представление исходной задачи без учета взаимосвязей между Τ-операторами, то есть без учета микропроцессорной конфигурации ИВС при заданном алгоритме решения задач.

Микропроцессор в виде, в котором он здесь рассматривается, является абстракцией как аппаратных, так и программных средств. Линии, соединяющие микропроцессоры в определенную конфигурацию, интерпретируются как каналы данных и управления [4].

Для

описания объектных программ, получаемых

с выхода транслирующего

алгоритма

![]() ,

анализа синтаксических и семантических

связей

в них, а также для исследования организации

вычислительного процесса

в пространстве, как показали исследования,

удобно использовать

гиперграфы. В этом аспекте такими

моделями микропроцессоров являются

различные гиперграфы.

,

анализа синтаксических и семантических

связей

в них, а также для исследования организации

вычислительного процесса

в пространстве, как показали исследования,

удобно использовать

гиперграфы. В этом аспекте такими

моделями микропроцессоров являются

различные гиперграфы.

О п р

е д е л е н и е 2. Гиперграфом L

для

представления Т-оператора

для функции

![]() на

множестве вершин Еf

называется

всякое подмножество множества

на

множестве вершин Еf

называется

всякое подмножество множества

![]() ,

причемЕf

- множество

решений системы уравнений Шеннона для

функций f.

,

причемЕf

- множество

решений системы уравнений Шеннона для

функций f.

Тогда

моделью перестраиваемого микропроцессора

является гиперграф с числом гиперребер

![]() .

.

О п р

е д е л е н и е 3. Гиперграф L

называется

максимальным представлением Т-оператора

для функции f,

если он имеет в точности

![]() элементов.

элементов.

Если

интерпретировать каждую вершину графа

коммутации микропроцессоров Gk

как

некоторый автомат, на вход которого

поступает вектор

![]() ,

а с выхода снимаются функции из множестваЕf,

то получается автоматная модель

вычислительного процесса, которая

позволяет представлять вычислительный

процесс, как в пространстве, так и во

времени.

,

а с выхода снимаются функции из множестваЕf,

то получается автоматная модель

вычислительного процесса, которая

позволяет представлять вычислительный

процесс, как в пространстве, так и во

времени.

Рассмотрим процедуру организации вычислительного процесса в ИВС при синхронном принципе управления параллельными процессами [34]. При использовании в микропроцессорах регистровых коммутирующих элементов или элементов (РКЭ) другого типа, в которых передача информации жестко синхронизирована, появляется особенность в передаче информации между СМП и выполнении операций в ОА, т.е. в реализации Τ -операторов [34].

Поскольку

двоичная информация передается от

одного РКЭ к другому по тактам, считается,

что РКЭ дает задержку по цепи вход-выход

на один такт, а ОА реализует функции с

помощью оператора

![]() заm

тактов.

заm

тактов.

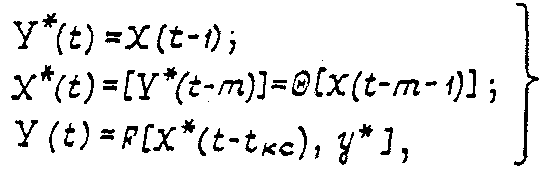

Тогда временные соотношения между входом и выходом СМП имеют вид:

(7.1)

(7.1)

где

![]()

структурный оператор, реализуемый ОА

СМП, выдающим значения функции f(z)

в

двоичной

форме;

структурный оператор, реализуемый ОА

СМП, выдающим значения функции f(z)

в

двоичной

форме;

![]() -

структурный оператор коммутации,

реализуемый РКЭ, соответствующий

функциям коммутации F1

и

F2;

-

структурный оператор коммутации,

реализуемый РКЭ, соответствующий

функциям коммутации F1

и

F2;

![]()

управляющий вектор СМП; tKC

–

задержка

комбинационной схемы РКЭ.

управляющий вектор СМП; tKC

–

задержка

комбинационной схемы РКЭ.

Из (7.1) следует, что

![]() .

.

Следовательно,

на выходе микропроцессора информация

появится через (m+1)

тактов при условии, что

![]() ,

то

есть один такт в СМП требуется на передачу

информации с ячеек сдвигающего регистра

РКЭ и m

тактов

для преобразования информации на ОА

СМП.

,

то

есть один такт в СМП требуется на передачу

информации с ячеек сдвигающего регистра

РКЭ и m

тактов

для преобразования информации на ОА

СМП.

Если на вход микропроцессора с номером N приходит информация с выхода СМП с номером k, то временная связь между ними, при условии, что информация проходит через канал связи с (N-K) СМП, выразится как

![]()

при

условии, что

![]() mj

– время выполнения операции ОА j-го

микропроцессора.

mj

– время выполнения операции ОА j-го

микропроцессора.

Рассматривая

данный процесс на уровне решающих

блоков, входящих в ОА, можно заметить

следующее. Пусть имеется канал связи

между K-м

и

N-м

и

СМП; mN

тактов

необходимо для реализации СУШ или

оператора в ОА N-го

СМП; mj

тактов

необходимо для реализации СМП в j-х

СМП;

![]() .

Тогда, выделяя в

ОА

K-го

СМП выходной УРБ, генерирующий приращение

некоторой функции

.

Тогда, выделяя в

ОА

K-го

СМП выходной УРБ, генерирующий приращение

некоторой функции

![]() и выделяя в ОАN-го

микропроцессора входной УРБ, в котором

из приращений

и выделяя в ОАN-го

микропроцессора входной УРБ, в котором

из приращений

![]() нормируется

приращение подынтегральной функции

нормируется

приращение подынтегральной функции

где b

- число

входов УРБ по переменной

где b

- число

входов УРБ по переменной

![]() ,

можно

написать,

полагая b

= 1, что

,

можно

написать,

полагая b

= 1, что

(7.2)

(7.2)

где j = k+1 берется без учета времени тк K-го СМП.

Данный процесс иллюстрируется рис. 7.20.

Если

передача информации происходит от k-го

СМП к N-му

через канал РКЭ с неподключенными ОА

![]() то

выражение (7.2.)

преобразуется

к виду

то

выражение (7.2.)

преобразуется

к виду

(7.3)

(7.3)

Тогда задержка

канала связи между ОА СМП, выдающим

![]() ,

и входной

последовательностью k-го

СМП

,

и входной

последовательностью k-го

СМП

![]() имеет

величину (N-1)

тактов без

учета времени выполнения операций mk,

mN

в ОА микропроцессоров.

имеет

величину (N-1)

тактов без

учета времени выполнения операций mk,

mN

в ОА микропроцессоров.

Таким образом, при решении задач на интегрирующей вычислительной структуре, состоящей из CМП, необходимо вводить управляющий цепи выравнивания задержек. На рис. 7.21 представлен граф соединений СМП, в котором вершины 7' и 10' являются управляющими, синхронизирующими выполнение процессов с различным числом СМП, находящихся на путях от входных вершин (1-4) графа до выходной вершины 11.

Другим эффективным способом, позволяющим учесть временные задержки в микропроцессорах, представляется асинхронное выполнение операций в СМП. Покажем возможность представления (описания) и организации вычислительного процесса в ИВС с помощью аппарата сетей Петри [5, 96, 118], которые позволяют представлять вычислительный процесс, как при синхронном, так и при асинхронном управлении параллельными процессами.

Рис. 7.20. Процесс передачи информации между РБ СМП

Любая программа может быть представлена в виде двух частей, или структур: информационной и управляющей. Информационная структура определяет взаимосвязь и её характер между информационными операторами в программе. Управляющая структура задает организацию вычислительного процесса в ИВС или, другими словами, определяет функционирование информационной структуры во времени и в пространстве в зависимости от внешних условий и программных ситуаций.

Рис. 7.21. Граф соединений СМП с синхронизирующими вершинами

Как отмечается в [116], средства управления можно классифицировать по способу действия как

- безусловные, не зависящие от текущих значений переменных, вырабатываемых информационными операторами (GO ТО - переходы, семафоры и т.д.);

- условные, зависящие от текущей ситуации (условный оператор, оператор анализа программной ситуации, условный критический интервал и т.д.);

- потоковые (управление типа LIFO - и FIFO - стеками, очередями и т.д.).

Для представления и описания безусловных структур управления используются сети Петри. С целью распространения аппарата сетей на описание организации вычислительного процесса в ИВС кратко сформулируем основные характеристики обыкновенных сетей Петри [118].

Под

сетью Петри

![]() понимается

двудольный граф, имеющий два множества

вершин: места, изображающие информационные

операторы и

переходы, изображающие управляющие

операторы. Отметим, что в частном

случае места могут изображать также и

микропроцессоры ИВС, а

переходы - связь СМП ИВС между собой.

Задается начальная разметка сети -

функция, приписывающая каждому месту

маркер (натуральное число n

0).

понимается

двудольный граф, имеющий два множества

вершин: места, изображающие информационные

операторы и

переходы, изображающие управляющие

операторы. Отметим, что в частном

случае места могут изображать также и

микропроцессоры ИВС, а

переходы - связь СМП ИВС между собой.

Задается начальная разметка сети -

функция, приписывающая каждому месту

маркер (натуральное число n

0).

![]() считается

функционирующей при переходе от одной

разметки к другой. При этом смена разметок

происходит только

при срабатывании переходов, причем

значение маркера входного места

уменьшается», а значение выходного (или

всех выходных)

места

увеличивается на 1.

Сеть

останавливается, если из начальной

разметки она перешла к такой, что ни

один из переходов не срабатывает.

считается

функционирующей при переходе от одной

разметки к другой. При этом смена разметок

происходит только

при срабатывании переходов, причем

значение маркера входного места

уменьшается», а значение выходного (или

всех выходных)

места

увеличивается на 1.

Сеть

останавливается, если из начальной

разметки она перешла к такой, что ни

один из переходов не срабатывает.

Таким

образом, для описания безусловных

структур управления статического типа

формально сеть Петри задается как

![]() ,

гдеI

– множество информационных (операторов)

вершин; u

–

множество управляющих (операторов)

вершин; IUи

– множество

вершин сети;

,

гдеI

– множество информационных (операторов)

вершин; u

–

множество управляющих (операторов)

вершин; IUи

– множество

вершин сети;

![]() или

или

![]()

отображение, определяющее множество

дуг (связей) сети

отображение, определяющее множество

дуг (связей) сети

![]() .

.

Произведем модификацию сети Петри, учитывая специфику ИВС. В основу ЯП ИВС положены следующие типы базовых структур, или конструкций:

предикативная структура типа

;

;итеративная структура типа

;

;итеративная структура типа

;

;распределительная структура типа

;

;простая последовательность типа

.

.

С помощью данных конструкций можно в ИВС реализовать любую программу, если структировать данные конструкции путем присоединения единственного выхода i-й к единственному входу j-й конструкции [115].

Для

формирования структуры управления

некоторой программы для ИВС необходимо

рассмотреть, что представляют собой

сети Петри

![]() для

базовых конструкций ЯП ИВС. Общую

управляющую структуру программы мοжнο

далее

получить структуризацией с использованием

определенных операций над сетями

для

базовых конструкций ЯП ИВС. Общую

управляющую структуру программы мοжнο

далее

получить структуризацией с использованием

определенных операций над сетями

![]() для

базовых конструкций – элементарных

сетей Петри.

для

базовых конструкций – элементарных

сетей Петри.

Для

управления вычислительным процессом

ИВС, т.е. для получения сети

![]() ,

введем следующую модификацию путем

представления сети в виде

,

введем следующую модификацию путем

представления сети в виде![]() ,

где V

= IUи

– множество вершин сети, Г

– отображение множества вершин в себя,

Р(х)

–

некоторый

предикат, могущий принимать истинное

или ложное значение, в результате чего

активизируется одна или другая часть

сети

,

где V

= IUи

– множество вершин сети, Г

– отображение множества вершин в себя,

Р(х)

–

некоторый

предикат, могущий принимать истинное

или ложное значение, в результате чего

активизируется одна или другая часть

сети

![]() .

.

Сеть

![]() для

конструкции

для

конструкции

![]() имеет

вид, представленный диаграммой (рис.

7.22). Реализация вычислительного процесса

в

ИВС

для

данной

конструкции с помощью сети будет иметь

вид:

имеет

вид, представленный диаграммой (рис.

7.22). Реализация вычислительного процесса

в

ИВС

для

данной

конструкции с помощью сети будет иметь

вид:

-

P(x)

= 1;

![]()

активизация сети для программного

участка Q

т.е.

P(x)

= 1;

do

Q

end;

активизация сети для программного

участка Q

т.е.

P(x)

= 1;

do

Q

end;

-

P(x)

= 0;

![]()

активизация сети для программного

участка S

т.е.

P(x)=

0; do

S

end.

активизация сети для программного

участка S

т.е.

P(x)=

0; do

S

end.

Таким

образом, реализация вычислительного

процесса в ИВС для конструкции![]() свелась

к выполнению двух простых последовательностей

DO-END,

активизируемых значением предиката

P(x)

= 0,1.

свелась

к выполнению двух простых последовательностей

DO-END,

активизируемых значением предиката

P(x)

= 0,1.

Реализация вычислительного процесса для конструкции WHILE Р(x) DO Q имеет вид

-

P(x)

= 1,

![]()

активизация сети для программного

участка Q

т.е.

Р(x)

= 1; do

Q

end;

активизация сети для программного

участка Q

т.е.

Р(x)

= 1; do

Q

end;

![]() производится

выход из данной структуры путем передачи

управления дальше по программе, т.е.

производится

выход из данной структуры путем передачи

управления дальше по программе, т.е.

![]() -

выполняется простая последовательность

с пустым оператором.

-

выполняется простая последовательность

с пустым оператором.

Рис. 7.22. Модифицированная сеть

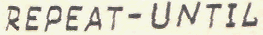

Реализация вычислительного процесса для конструкции REPEAT Q UNTILE Р(х) аналогична предыдущей с той лишь разницей, что здесь сначала вычисляется значение Q, а далее производится анализ условия Р(х):

Реализация вычислительного процесса для конструкции простая последовательность DO-END имеет ту особенность, что здесь под управлением сети включается входное меcто, далее происходит реализация программы Q в теле do-end и включается выходное место. Реализация сетями вычислительных процессов в ИBC приведена в табл. 7.4.

Таблица 7.4.

После

представления вычислительного процесса

в ИВС в виде модифицированной сети Петри

![]() ,

активизируемой

в

зависимости от значений предиката Р(x),

необходимо

рассмотреть принципы построения

управляющей структуры программы из так

называемых базовых сетей для конструкций

ЯП ИВС. Другими словами, необходимо

построить сеть

,

активизируемой

в

зависимости от значений предиката Р(x),

необходимо

рассмотреть принципы построения

управляющей структуры программы из так

называемых базовых сетей для конструкций

ЯП ИВС. Другими словами, необходимо

построить сеть

![]() из

базовых сетей, не рассматривая вопросов

активизации и реализации вычислительных

процессов в ИВС.

из

базовых сетей, не рассматривая вопросов

активизации и реализации вычислительных

процессов в ИВС.

Здесь

возможны два варианта получения

![]() .

Первый из них базируется на подходе,

предложенном в [96]. Суть его заключается

в том, что произвольная сеть получается

из элементарной сети применением

различных операций (слияния, итерации,

замыкания и т.д.). Второй подход основан

на представлении принятых за базовые

фрагменты программы в виде сетей, которые

также в свою очередь принимаются в

качестве того базисного набора, из

которого набирается сеть Петри исходной

программы[5].

.

Первый из них базируется на подходе,

предложенном в [96]. Суть его заключается

в том, что произвольная сеть получается

из элементарной сети применением

различных операций (слияния, итерации,

замыкания и т.д.). Второй подход основан

на представлении принятых за базовые

фрагменты программы в виде сетей, которые

также в свою очередь принимаются в

качестве того базисного набора, из

которого набирается сеть Петри исходной

программы[5].

Для

ИBC

предпочтительнее является 2-й подход,

так как использование первого связано

с трудностями получения базовых сетей

![]() для основных конструкций ЯП ИВС.

для основных конструкций ЯП ИВС.

Рассмотрим

структуризацию сети

![]() по

второму методу. Для этого построим

базовые сети Петри конструкций ЯП ИВС.

по

второму методу. Для этого построим

базовые сети Петри конструкций ЯП ИВС.

Они имеют следующий вид:

- сеть для конструкции do Q end представлена в виде последовательности мест и переходов, как показано на рис. 7.23, где Φi – переход, реализуемый на данной группе СМП ИВС информационный оператор Q; ti – входное, ti+1 – выходное места сети;

сети для конструкции

P(x)

осуществляется

как

сеть, изображенная на рис. 7.24, где

P(x)

осуществляется

как

сеть, изображенная на рис. 7.24, где

переход, представляющий информационный

оператор Q

;

р

– переход,

представляющий условие (предикат Ρ(x))

ветвления вычислительного процесса;

переход, представляющий информационный

оператор Q

;

р

– переход,

представляющий условие (предикат Ρ(x))

ветвления вычислительного процесса;

Рис. 7.24. Сеть для

конструкции типа repeat

until

P(x)

Рис. 7.23. Сеть для

конструкции типа do

end

сеть для конструкции

показана

на рис. 7.25, где

показана

на рис. 7.25, где

переходы, представляющие операторы Q

и

S

соответственно;

Ρ

-

переход,

осуществляющий условие (предикат)

ветвления вычислительного процесса;

переходы, представляющие операторы Q

и

S

соответственно;

Ρ

-

переход,

осуществляющий условие (предикат)

ветвления вычислительного процесса;сеть для конструкции

изображена на рис. 7.26

где

изображена на рис. 7.26

где

–

переход, представляющий оператор Q

;

Р – переход, представляющий условие

(предикат) ветвления процесса.

–

переход, представляющий оператор Q

;

Р – переход, представляющий условие

(предикат) ветвления процесса.

Как

видно, базовые сети

![]() имеют

один вход и один выход, что соответствует

принципам построения ЯП структуризованного

типа. Далее, используя либо методику

построения программ в структурном

программировании, либо методику

построения сети

имеют

один вход и один выход, что соответствует

принципам построения ЯП структуризованного

типа. Далее, используя либо методику

построения программ в структурном

программировании, либо методику

построения сети

![]() программы

с помощью набора операций [96], можно

получать

управляющую структуру программы

в виде сети Петри при асинхронном

принципе управления

системой.

программы

с помощью набора операций [96], можно

получать

управляющую структуру программы

в виде сети Петри при асинхронном

принципе управления

системой.

Рис. 7.25. Сеть для конструкции if P(x) then else

Рис. 7.26. Сеть для конструкции while P(x) do

Для иллюстрации функционирования разработанной системы ПО ИВС приведена программа подготовки вычислительного процесса в ИВС при решении задачи движения i-й ноги шагающего аппарата (робота), которое описывается следующей системой уравнений [23, 36]:

1)

2) базис для этой системы уравнений составляют операторы сложения, умножения, интеграла, синуса с оператором присваивания; базис:= + * INТ S1N

3) программа на входном языке представляется следующим образом: