- •В.Ф. Гузик проектирование проблемно - ориентированных вычислительных систем

- •Часть 1

- •Предисловие

- •Производительность суперкомпьютеров

- •Глава первая. Концепция построения многопроцессорных вычислительных систем с программируемой архитектурой (мвс па)

- •Глава вторая. Организация математического обеспечения мвс с программируемой архитектурой

- •2.1. Основы математического обеспечения многопроцессорных вычислительных систем с программируемой архитектурой

- •2.2. Организация машинных языков высокого уровня и технология программирования мвс с программируемой архитектурой

- •2.3. Организация параллельных вычислительных процессов в мвс с программируемой архитектурой

- •Глава третья. Проблемно-ориентированные мвс па

- •3.1.Методика перехода от систем дифференциальных и алгебраических уравнений к системе уравнений Шеннона

- •3.1.1.Представление исходной задачи в форме, удобной для реализации на цифровых интегрирующих машинах (цим)

- •3.1.2. Методика перехода от заданных функций к системе уравнений Шеннона

- •3.1.3. Методика перехода от заданных дифференциальных уравнений к системе уравнений Шеннона

- •3.1.4.Методика перехода от систем линейных алгебраических уравнений к системе уравнений Шеннона

- •3.1.5.Получение программных матриц соединений цифровых решающих модулей

- •3.1.6.Методика перехода от программных матриц к схеме соединения цифровых решающих модулей (црм) в цим с жесткими связями

- •3.2.Примеры структурной организации вычислительного процесса в цим.

- •3.2.1.Задача №1

- •3.2.2.Задача №2

- •3.2.3.Задача №3

- •Приложение 3.2

- •3.2.4.Задача №4

- •3.2.5.Задача №5

- •Глава четвёртая. Теоретические основы построения интегрируЮщих вычислительных структур модульного типа

- •4.1. Общая структурно-логическая схема проектирования (анализа и синтеза) модульных ивс

- •4.2. Представление задач для модульных ивс в операторном пространстве

- •4.3. Построение базиса в операторном -пространстве для ивс модульного типа

- •4.4. Разработка эффективного машинного алгоритма выбора базиса в операторном -пространстве

- •4.5. Математическая модель ивс модульного типа на основе t -алгоритмов

- •4.6. Примеры, иллюстрирующие работу базовой машины ивс

- •Глава пятая. Анализ и синтез универсальных решающих блоков интегрирующих вычислительных структур (ивс)

- •5.1. Синтез алгоритма универсального решающего блока интегрирующих вычислительных структур

- •5.2. Разработка алгоритма автоматического масштабирования переменных и приращений в универсальном решающем блока ивс

- •5.3. Построение структурных схем универсальных решающих блоков ивс с автоматическим масштабированием переменных

- •5.4 Разработка алгоритма универсального решающего блока, основанного на принципе цифрового слежения и синтез его структурной схемы

- •5.5.Проектирование решающей части интегрирующих вычислительных структур

- •Глава шестая. Проектирование функциональных модулей интегрирующих вычислительных структур

- •6.1. Исследование принципов построения коммутационных систем модульных интегрирующих вычислительных структур

- •6.2. Разработка волновых каскадных коммутирующих сред для интегрирующих вычислительных структур

- •6.3. Принципы построения цифровых решающих и функциональных модулей ивс

- •6.4.Определение параметров функциональных модулей интегрирующих вычислительных структур

- •6.5.Матричное представление функциональных модулей интегрирующих вычислительных структур

- •6.6. Построение специализированного микропроцессора интегрирующей вычислительной структуры

- •Глава седьмая. Система математического обеспечения модульных интегрирующих вычислительных структур

- •7.1. Структура системы математического обеспечения модульных ивс

- •7.2. Разработка языка структурного программирования высокого уровня для модульных ивс

- •7.3.Разработка транслятора, загрузчика и диспетчера системы программного обеспечения модульных ивс

- •7.4. Построение пакета системных программ для программного обеспечения ивс

- •7.5. Организация вычислительных процессов в модульных ивс

- •Глава восьмая. Однородные цифровые интегрирующие структуры

- •8.1. Цифровые интеграторы для оцис

- •8.2. Интерполяционные и экстраполяционные, одноразрядные и многоразрядные однородные цифровые интегрирующие структуры

- •Глава девятая. Примеры проектирования проблемно- ориентированных мвс на интегрирующих структурах

- •9.1. Моделирующий вычислительный комплекс для исследования систем инерциальной навигации на основе модульных ивс

- •9.2. Применение интегрирующих вычислительных структур для реализации систем управления манипуляционными устройствами автономных роботов

- •9.3. Специализированная вычислительная система для решения задач управления с прогнозированием

- •9.4. Логико-интегрирующие вычислительные структуры

- •Приложение 1 Примерный перечень

- •Министерство образования и науки российской федерации

- •Курс «Технология программирования»

- •Практические задания

- •Курс «Интерфейсы периферийных устройств»

- •Курс «Конструкторско-технологическое обеспечение производства эвм»

- •Библиографический список

- •Оглавление

8.2. Интерполяционные и экстраполяционные, одноразрядные и многоразрядные однородные цифровые интегрирующие структуры

Все задачи, решаемые с помощью однородных цифровых интегрирующих структур сводятся к некоторым эквивалентным дифференциальным уравнениям или к системам дифференциальных уравнений Шеннона. Наиболее удобной для синтеза ОЦИС является симметричная форма уравнений Шеннона

;

;

(8.18)

(8.18)

;![]()

![]()

![]()

Здесь величины ![]() и

и ![]() являются постоянными коэффициентами,

задающими фактически программу решения

задачи.

являются постоянными коэффициентами,

задающими фактически программу решения

задачи.

Система уравнений Шеннона может быть записана в матрично-векторной форме:

![]()

![]()

![]() (8.19)

(8.19)

![]()

где Ар и Аq представляют собой бинарные матрицы

(8.20)

(8.20)

а векторы ![]() ,

,

![]() и

и ![]() являются соответственно векторами

интегралов, подынтегральных функций и

переменных интегрирования

являются соответственно векторами

интегралов, подынтегральных функций и

переменных интегрирования

(8.21)

(8.21)

Операция

![]() преобразует вектор

преобразует вектор![]() в диагональную матрицу:

в диагональную матрицу:

(8.22)

(8.22)

Как следует из уравнений Шеннона (8.18) и (8.19), в однородных цифровых интегрирующих структурах необходимы лишь две операции - операция интегрирования и операция суммирования. Таким образом, для построения ОЦИС достаточно располагать процессорами, которые выполняют операции суммирования и интегрирования. Как показано выше при рассмотрении цифровых интеграторов, к этим операциям следует добавить операцию квантования приращений интеграла и операцию экстраполяции приращений.

Имея в распоряжении процессор, выполняющий операции суммирования, интегрирования, квантования и экстраполяции, а также располагая ячейками коммутации, нетрудно синтезировать однородную цифровую интегрирующую структуру, состоящую из множества однотипных интегрирующих процессоров, выполняющих указанные операции, и из однородной коммутационной структуры, обеспечивающей образование необходимых каналов связи между процессорами. При этом программа образования каналов связи задается фактически двумя бинарными матрицами Ар и Aq, состоящими из нулей и единиц, которые однозначно определяют в зависимости от решаемой задачи соединения выходов всех интегрирующих процессоров с соответствующими входами других процессоров.

В ОЦИС реализуется фактически не система дифференциальных уравнений Шеннона (8.18), а эквивалентная ей разностная схема. В зависимости от типа интеграторов, использованных при синтезе однородных цифровых интегрирующих структур - интерполяционных или экстраполяционных, многоразрядных или одноразрядных, в ОЦИС будут реализовываться различные разностные схемы.

Е

;

;![]()

![]()

;

;![]()

;![]()

![]()

![]()

Здесь матрицы Ар

и Аq,

задают программу решения системы

уравнений Шеннона, векторы

![]() и

и![]() являются приращениями векторов искомых

переменных

являются приращениями векторов искомых

переменных

![]() и

и![]() ,

а функция

,

а функция ![]() представляет собой

одну из интерполяционных формул

численного интегрирования по Стилтьесу,

использованную для синтеза цифрового

интегратора.

представляет собой

одну из интерполяционных формул

численного интегрирования по Стилтьесу,

использованную для синтеза цифрового

интегратора.

Так как неизвестные

приращения ![]() входят не только

в левые, но и в правые части уравнений

интерполяционной разностной схемы

(8.23), то вычислять их можно только

итерационным методом. Для того, чтобы

воспользоваться итерационным методом,

необходимо представить интерполяционную

разностную схему в следующей форме:

входят не только

в левые, но и в правые части уравнений

интерполяционной разностной схемы

(8.23), то вычислять их можно только

итерационным методом. Для того, чтобы

воспользоваться итерационным методом,

необходимо представить интерполяционную

разностную схему в следующей форме:

;![]()

;![]()

;

;

(8.24)![]()

![]()

![]()

![]()

И

![]() ,

после чего на основе уравнений (8.24)

реализуется итерационный процесс (k

= 1, 2, …, N),

который продолжается до того момента,

пока изменения векторов

,

после чего на основе уравнений (8.24)

реализуется итерационный процесс (k

= 1, 2, …, N),

который продолжается до того момента,

пока изменения векторов

![]() и

и![]() за одну итерацию не станут меньше

векторов квантов Z,

Yp

и Yq.

После этого производится переход к

следующему шагу интегрирования, который

осуществляется таким же итерационным

методом.

за одну итерацию не станут меньше

векторов квантов Z,

Yp

и Yq.

После этого производится переход к

следующему шагу интегрирования, который

осуществляется таким же итерационным

методом.

Рассмотренная итерационная процедура справедлива только в случае многоразрядных приращений и, следовательно, только в случае использования в интеграторах интерполяционной формулы трапеций или более точных формул численного интегрирования.

Структура ОЦИС интерполяционного типа, в которой реализуется описанный итерационный процесс, приведена на рис. 8.11.

Достоинство итерационных ОЦИС состоит в том, что в них легко организуется процесс интегрирования на начальном участке, а также в отсутствии экстраполяторов приращений. К недостаткам следует отнести снижение скорости вычислений за счет итерационного процесса и необходимость производить оценку сходимости итерационного процесса, а также оценку получаемой при итерациях точности, что усложняет работу ОЦИС.

Рис. 8.11 Структура ОЦИС интерполяционного типа

Более быстродействующими и более удобными являются ОЦИС экстраполяционного типа, в которых реализуется экстраполяционная разностная схема интегрирования уравнений Шеннона, записываемая в следующей матрично-векторной форме:

;

;![]()

![]()

;![]()

;

;![]()

![]()

![]()

Структура ОЦИС экстраполяционного типа изображена на рис. 8.12.

Рис. 8.12 Структура ОЦИС экстраполяционного типа

Экстраполяционные ОЦИС являются более быстродействующими, чем интерполяционные, за счет устранения итерационного процесса. К недостаткам их относятся некоторые трудности реализации процесса интегрирования на начальном участке. Однако эти трудности можно преодолеть, если сначала реализовать на начальном участке вместо экстраполяционного итерационный процесс интегрирования, что достигается за счет отключения экстраполяторов и организации итераций, а затем через несколько шагов интегрирования перейти вновь к экстраполяционной схеме вычислений.

Как интерполяционные, так и экстраполяционные ОЦИС, работают на основе достаточно точных формул интегрирования с многоразрядными приращениями. Скорость и точность ОЦИС этих типов достаточно велики за счет использования точных формул интегрирования и параллельности процесса вычислений в ОЦИС.

Е

;

;![]()

![]()

;![]()

;![]()

![]()

![]()

Соответствующая структура ОЦИС изображена на рис. 8.13.

Рис. 8.13 Структура ОЦИС оперирующая с одноразрядными приращениями

Конструктивно ОЦИС могут быть выполнены в виде структуры, состоящей из однотипных интегрирующих процессоров, равномерно распределенных в пространстве, и некоторой коммутационной структуры, заполняющей свободные промежутки между процессорами.

Успехи микроэлектроники позволили в настоящее время построить цифровой интегрирующий процессор в виде единой твердой схемы, размеры которой составляют всего несколько квадратных миллиметров, а вес исчисляется миллиграммами. Еще более простыми и миниатюрными могут быть выполнены коммутационные элементы, предназначенные для электронной коммутации процессоров между собой.

Любой процессор ОЦИС может быть окружен несколькими слоями коммутационных элементов, а входы и выходы процессора могут быть соединены с отдельными коммутационными элементами, каждый из которых, в свою очередь, соединяется с соседними элементами, входящими в слои.

Если такую систему, состоящую из одного цифрового интегратора и ряда слоев коммутационных элементов, изготовить в виде монолитной большой интегральной схемы, то образуется универсальный стандартный блок однородной цифровой интегрирующей структуры, который можно поместить в одном корпусе.

Из подобных блоков легко набирается однородная цифровая интегрирующая структура с любым количеством процессоров. Для этого стандартные блоки располагаются на плоскости или в пространстве и соединяются однотипным образом с соседними блоками путем объединения выходов крайних коммутационных элементов одного блока с входами крайних коммутационных элементов другого блока и наоборот.

В зависимости от взаимного расположения процессоров и коммутирующих элементов можно представить себе три типа однородных цифровых интегрирующих структур: линейные, плоские и пространственные.

Рис. 8.14 Структура линейной ОЦИС

Стандартный блок линейной ОЦИС представляет собой процессор, входы и выходы которого располагаются с одной стороны (рис. 8.14) и соединяются с входами и выходами участка однородной коммутационной структуры, состоящей из нескольких рядов коммутационных элементов. Входы и выходы боковых коммутационных элементов, входящих в блок, служат для соединения с соседними стандартными блоками.

Располагая подобные стандартные блоки в одну линию и соединяя между собой их входы и выходы, получим линейную однородную вычислительную структуру (рис. 8.15).

В такой структуре легко образуются любые соединения между входами и выходами процессоров за счет настройки коммутирующих элементов на соответствующие каналы связи.

Рис. 8.15 Структура линейной ОЦИС с универсальной коммутацией

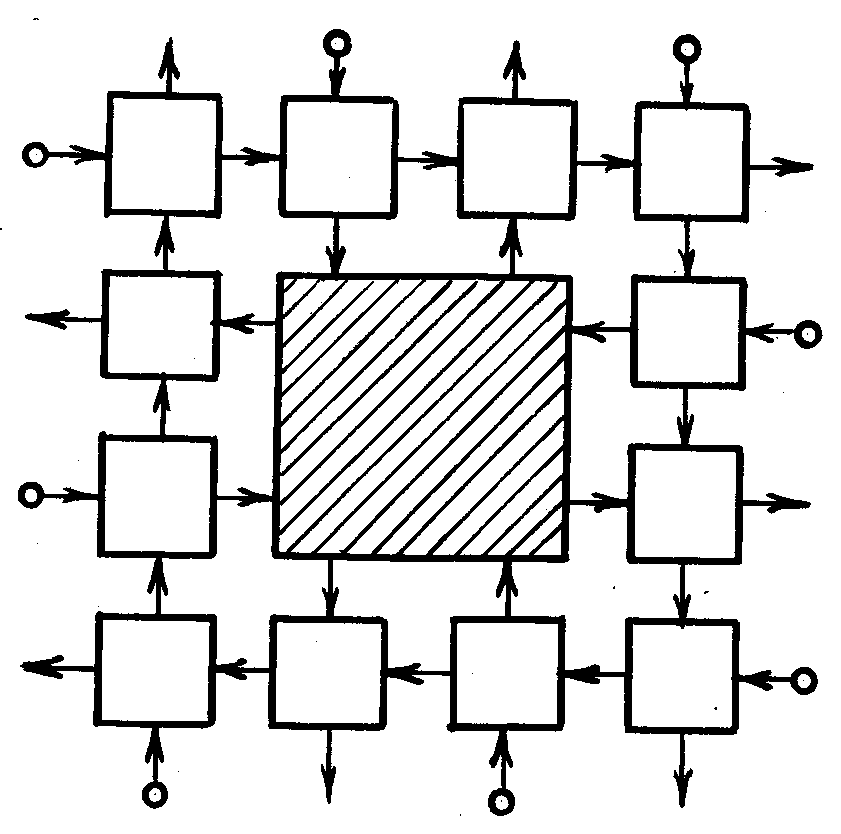

Наряду с линейными могут быть построены плоские ОЦИС. В основу таких структур кладется стандартный блок, состоящий в простейшем случав из процессора, окруженного одним слоем коммутационных элементов (рис. 8.16).

Рис. 8.16 Структура плоской ОЦИС с одним слоем коммутирующих элементов

Стандартный блок с одним слоем коммутационных элементов существенно ограничивает возможность образования каналов связи между процессорами плоской ОЦИС. Поэтому следует, как правило, использовать стандартные блоки, в которых процессор окружается несколькими слоями коммутационных элементов (рис. 8.17).

Рис. 8.17 Структура ОЦИС с несколькими слоями коммутирующих элементов

Располагая подобные стандартные блоки на плоскости плотно один к другому, получаем плоскую однородную цифровую интегрирующую структуру (рис. 8.18).

Рис. 8.18 Структура плоской ОЦИС с универсальной коммутацией.

В зависимости от числа слоев коммутационных элементов можно обеспечить соединение каждого процессора ОЦИС с любым другим процессором либо ограничиться соединением каждого процессора только с теми процессорами, которые расположены в его ближайших окрестностях. Первый метод коммутации носит название коммутации по принципу полного графа. Второй метод коммутации называется коммутацией по принципу близкодействия.

Хотя коммутация по принципу полного графа является наиболее универсальной, этот принцип целесообразно применять лишь в структурах с малым числом процессором, так как при значительном их количестве число необходимых коммутирующих элементов оказывается очень большим. Основная часть задач, встречающихся на практике, не требует максимальной универсальности ОЦИС. Многие задачи расчленяются обычно на более простые задачи, каждая из которых может быть запрограммирована с помощью отдельной группы интеграторов, причем такие группы объединяются между собой относительно небольшим числом каналов связей. В результате рассмотренные задачи можно решать в однородной интегрирующей структуре, организованной по принципу близкодействия. Число коммутирующих элементов в подобной структуре существенно уменьшается.

Аналогично плоским ОЦИС могут быть синтезированы также и пространственные ОЦИС, в которых интеграторы и коммутационные элементы рас-полагаются и соединяются между собой в трехмерном пространстве [36, 76, 77].