- •В.Ф. Гузик проектирование проблемно - ориентированных вычислительных систем

- •Часть 1

- •Предисловие

- •Производительность суперкомпьютеров

- •Глава первая. Концепция построения многопроцессорных вычислительных систем с программируемой архитектурой (мвс па)

- •Глава вторая. Организация математического обеспечения мвс с программируемой архитектурой

- •2.1. Основы математического обеспечения многопроцессорных вычислительных систем с программируемой архитектурой

- •2.2. Организация машинных языков высокого уровня и технология программирования мвс с программируемой архитектурой

- •2.3. Организация параллельных вычислительных процессов в мвс с программируемой архитектурой

- •Глава третья. Проблемно-ориентированные мвс па

- •3.1.Методика перехода от систем дифференциальных и алгебраических уравнений к системе уравнений Шеннона

- •3.1.1.Представление исходной задачи в форме, удобной для реализации на цифровых интегрирующих машинах (цим)

- •3.1.2. Методика перехода от заданных функций к системе уравнений Шеннона

- •3.1.3. Методика перехода от заданных дифференциальных уравнений к системе уравнений Шеннона

- •3.1.4.Методика перехода от систем линейных алгебраических уравнений к системе уравнений Шеннона

- •3.1.5.Получение программных матриц соединений цифровых решающих модулей

- •3.1.6.Методика перехода от программных матриц к схеме соединения цифровых решающих модулей (црм) в цим с жесткими связями

- •3.2.Примеры структурной организации вычислительного процесса в цим.

- •3.2.1.Задача №1

- •3.2.2.Задача №2

- •3.2.3.Задача №3

- •Приложение 3.2

- •3.2.4.Задача №4

- •3.2.5.Задача №5

- •Глава четвёртая. Теоретические основы построения интегрируЮщих вычислительных структур модульного типа

- •4.1. Общая структурно-логическая схема проектирования (анализа и синтеза) модульных ивс

- •4.2. Представление задач для модульных ивс в операторном пространстве

- •4.3. Построение базиса в операторном -пространстве для ивс модульного типа

- •4.4. Разработка эффективного машинного алгоритма выбора базиса в операторном -пространстве

- •4.5. Математическая модель ивс модульного типа на основе t -алгоритмов

- •4.6. Примеры, иллюстрирующие работу базовой машины ивс

- •Глава пятая. Анализ и синтез универсальных решающих блоков интегрирующих вычислительных структур (ивс)

- •5.1. Синтез алгоритма универсального решающего блока интегрирующих вычислительных структур

- •5.2. Разработка алгоритма автоматического масштабирования переменных и приращений в универсальном решающем блока ивс

- •5.3. Построение структурных схем универсальных решающих блоков ивс с автоматическим масштабированием переменных

- •5.4 Разработка алгоритма универсального решающего блока, основанного на принципе цифрового слежения и синтез его структурной схемы

- •5.5.Проектирование решающей части интегрирующих вычислительных структур

- •Глава шестая. Проектирование функциональных модулей интегрирующих вычислительных структур

- •6.1. Исследование принципов построения коммутационных систем модульных интегрирующих вычислительных структур

- •6.2. Разработка волновых каскадных коммутирующих сред для интегрирующих вычислительных структур

- •6.3. Принципы построения цифровых решающих и функциональных модулей ивс

- •6.4.Определение параметров функциональных модулей интегрирующих вычислительных структур

- •6.5.Матричное представление функциональных модулей интегрирующих вычислительных структур

- •6.6. Построение специализированного микропроцессора интегрирующей вычислительной структуры

- •Глава седьмая. Система математического обеспечения модульных интегрирующих вычислительных структур

- •7.1. Структура системы математического обеспечения модульных ивс

- •7.2. Разработка языка структурного программирования высокого уровня для модульных ивс

- •7.3.Разработка транслятора, загрузчика и диспетчера системы программного обеспечения модульных ивс

- •7.4. Построение пакета системных программ для программного обеспечения ивс

- •7.5. Организация вычислительных процессов в модульных ивс

- •Глава восьмая. Однородные цифровые интегрирующие структуры

- •8.1. Цифровые интеграторы для оцис

- •8.2. Интерполяционные и экстраполяционные, одноразрядные и многоразрядные однородные цифровые интегрирующие структуры

- •Глава девятая. Примеры проектирования проблемно- ориентированных мвс на интегрирующих структурах

- •9.1. Моделирующий вычислительный комплекс для исследования систем инерциальной навигации на основе модульных ивс

- •9.2. Применение интегрирующих вычислительных структур для реализации систем управления манипуляционными устройствами автономных роботов

- •9.3. Специализированная вычислительная система для решения задач управления с прогнозированием

- •9.4. Логико-интегрирующие вычислительные структуры

- •Приложение 1 Примерный перечень

- •Министерство образования и науки российской федерации

- •Курс «Технология программирования»

- •Практические задания

- •Курс «Интерфейсы периферийных устройств»

- •Курс «Конструкторско-технологическое обеспечение производства эвм»

- •Библиографический список

- •Оглавление

Глава первая. Концепция построения многопроцессорных вычислительных систем с программируемой архитектурой (мвс па)

Приведём основные принципы построения так называемых «универсальных» МВС ПА. Слово универсальных взято в кавычки, так как здесь понимается гипотетическая возможность решения любых задач на МВС ПА.

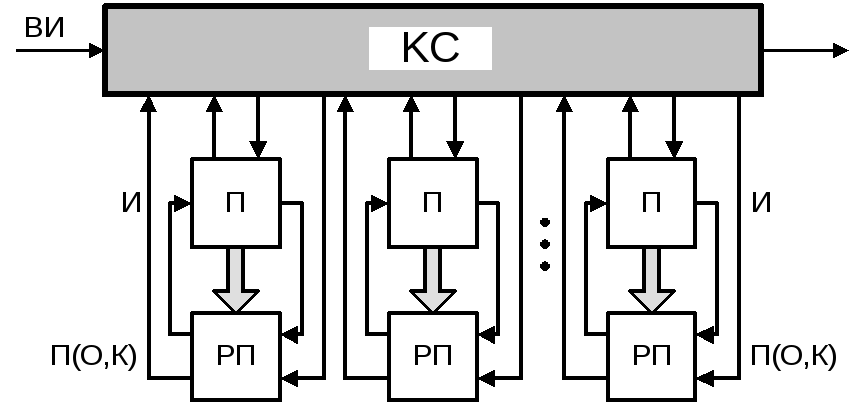

Многопроцессорная система с программируемой архитектурой должна иметь мощную универсальную коммутационную структуру КС, которая позволяет образовывать путем программирования любые прямые каналы связи между входами и выходами любых процессоров П, входящих в систему, между процессорами и распределенной памятью РП, а также между отдельными секторами памяти (рис.1.1).

Универсальная коммутационная структура дает возможность запрограммировать при решении любой задачи такую систему каналов связи между процессорами многопроцессорной системы, которая будет адекватна внутренней структуре решаемой задачи (рис 1.2).

Рис. 1.1. Многопроцессорная система с программируемой архитектурой

Рис.1.2. Многопроцессорная система с запрограммированной коммутацией

Программирование прямых каналов связи обеспечивает наилучшее распараллеливание вычислительного процесса, высокую скорость обмена данными между процессорами и максимальную производительность системы. Особое значение имеет то, что программирование прямых каналов связи адекватно отражает внутреннюю структуру задачи, обеспечивает линейный рост производительности многопроцессорной системы с программируемой архитектурой в зависимости от числа задействованных в решении задачи процессоров, что не удается обеспечить в многопроцессорных системах с жесткой архитектурой.

Конструктивно многопроцессорная вычислительная система с программируемой архитектурой может быть выполнена в модульной форме (рис.1.3), состоящей из сверхбольших интегральных схем СБИС, каждая из которых включает процессор П, сектор распределенной памяти РП и локальную коммутационную структуру КС. Внутренние каналы связи СБИС организуются так, чтобы процессор имел прямой доступ к распределенной памяти и коммутационной структуре, а распределенная память была связана прямым каналом связи с коммутационной структурой.

Такие СБИС соединяются регулярно с соседними с помощью жестких каналов связи между ближайшими локальными коммутационными структурами, в результате чего образуется общая программируемая коммутационная структура и многопроцессорная система с программируемой архитектурой в целом.

Рис.1.3. Многопроцессорная система в модульной форме

Многопроцессорные системы с программируемой архитектурой дают возможность организовывать любые многопроцессорные системы других классов. В частности, в многопроцессорной системе с программируемой архитектурой может быть легко запрограммирована известная жесткая многопроцессорная система: магистральная (рис.1.4), матричная и др. Это соответствует программированию виртуальных машин в однопроцессорных ЭВМ. Однако существенная разница заключается в том, что, в отличие от процедурной реализации виртуальной машины в однопроцессорной ЭВМ, в многопроцессорной системе с программируемой архитектурой виртуальная вычислительная система реализуется аппаратно (структурно).

Таким образом, мощная программируемая коммутационная структура обеспечивает быструю перестройку многопроцессорной системы на любую архитектуру, как известную, так и такую, которая может быть предложена в дальнейшем. Дело заключается лишь в создании мощной коммутационной структуры, позволяющей программировать и настраивать тысячи и десятки тысяч каналов связи и изменять их в процессе работы многопроцессорной системы в соответствии с изменением структуры решаемой задачи или ее параметров.

Рис.1.4 Структура магистральной многопроцессорной системы

В настоящее время созданы большие интегральные схемы коммутаторов со значительным числом входов и выходов, которые позволяют программировать соединение любого входа с любой группой выходов. Из подобных схем могут быть образованы весьма мощные коммутационные структуры с сотнями и даже тысячами входов и выходов, которые обеспечивают возможность программирования, настройки и перестройки сотен и тысяч каналов связи в процессе работы многопроцессорной системы.

В основе организации вычислительных процессов в многопроцессорных системах с программируемой архитектурой лежит принцип потока данных. Как известно, господствующий в настоящее время при разработке и синтезе ЭВМ и даже большинства многопроцессорных систем фон-неймановский принцип потока управления заключается в том, что программой задаётся поток инструкций, под воздействием которого системой управления в процессоре организуется процедура обработки данных. Поток инструкций циркулирует в соответствии с программой между сосредоточенной памятью СП, системой управления СУ и процессором П. Каждая инструкция (команда) потока определяет необходимые данные, которые должны быть извлечены из памяти; операцию, выполняемую над ними; адрес памяти, куда направляется результат; очередную инструкцию потока управления (рис. 1.5).

Рис.1.5 Многопроцессорная система с сосредоточенной памятью

Применение принципа потока управления к многопроцессорным системам значительно затрудняет организацию взаимодействия между параллельно работающими процессорами, осложняет программирование, приводит к громоздким операционным системам и, безусловно, снижает производительность системы. Поэтому при синтезе многопроцессорных систем с программируемой архитектурой используется принцип потока данных, который состоит в том, что к каждому процессору многопроцессорной системы подводится поток данных, под воздействием которого процессор настраивается на необходимые операции, и затем эти операции выполняются над поступившими данными.

Инструкции в многопроцессорной системе (И), основанной на принципе потока данных (рис. 1.6), распределяются заранее или в процессе решения задач операционной системой и системой управления СУ между параллельно работающими процессорами П.

Рис.1.6 Многопроцессорная система на принципе потока данных

Поступившие в процессоры инструкции не изменяются затем в течение длительного периода времени, необходимого для реализации законченного алгоритма или даже для решения задачи в целом. Одновременно с распределением инструкций между процессорами операционная система и СУ задают в КС многопроцессорной системы каналы связи для передачи потоков данных между процессорами, а также между процессорами и распределенной памятью. В результате в многопроцессорной системе с программируемой архитектурой, использующей принцип потока данных, каждый процессор реализует одну из инструкций, которая начинает выполняться, как только поступают соответствующие данные, а результаты сразу же передаются для дальнейшей обработки в следующие параллельно функционирующие процессоры. Таким образом, каждый процессор обрабатывает определенный поток данных, используя для этого одну длительно действующую инструкцию, и выполняет соответствующую ей операцию. Отличительной особенностью такого подхода является безадресная работа с данными и использование раздельных каналов связи для передачи данных и обмена инструкциями.

Многопроцессорная система с программируемой архитектурой, основанная на принципе потока данных, автоматически использует параллелизм, присущий решаемым задачам. Это значительно облегчает организацию параллельной работы процессоров, распределение заданий между ними при программировании и организацию обмена информацией между процессорами. В результате производительность многопроцессорной системы существенно возрастает.

В многопроцессорных системах с программируемой архитектурой необходимо отказаться от классической сосредоточенной общей для всех процессоров памяти (рис. 1.5), которая приводит при обмене информацией между процессорами и памятью к образованию очередей и падению производительности системы.

В основу таких систем с программной архитектурой кладется распределенная локальная память РП (см. рис. 1.1 и 1.2), к которой все процессоры системы могут обращаться параллельно без очередей. Наличие в многопроцессорной системе с программируемой архитектурой мощной коммутационной структуры обеспечивает возможность образования прямых каналов связи для перекачки информации из одного сектора РП в другой и для обмена данными между каждым процессором и любым сектором распределенной памяти.

Однако полностью исключать из многопроцессорной системы с программируемой архитектурой общую сосредоточенную память нецелесообразно. Наряду с распределенной памятью она предназначена для хранения редко используемой в вычислениях информации. Последняя извлекается по мере необходимости, образуя для этого в программируемой коммутационной структуре временные прямые каналы связи между СП и соответствующим сектором РП (рис. 1.6).

В многопроцессорных системах с программируемой архитектурой используется аппаратурный принцип реализации макроопераций, при котором для выполнения макрооперации программируется не процедура последовательности простейших команд и соответствующих им операций, как это делается в обычных классических процессорах, а внутренняя структура процессора с целью аппаратурной реализации необходимой макрооперации.

Основная проблема аппаратурной реализации макроопераций состоит в том, что необходимо обеспечить возможность выполнения различных макроопераций одним и тем же процессором только путем программной перестройки его внутренней структуры. Решается эта задача введением в процессор внутренней коммутационной структуры, программирование которой и обеспечивает аппаратурную реализацию различных макроопераций.

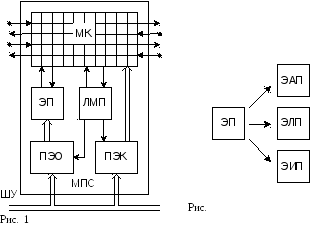

Организация внутренней структуры процессоров, основанных на принципе программирования аппаратуры, значительно отличается от классических процессоров, основанных на принципе программирования процедуры. Классический процессор, использующий процедурный принцип выполнения макроопераций, как известно, содержит арифметико-логическое устройство, блок регистров, интерфейс и систему управления. В отличие от него процессор с программируемой структурой, основанный на принципе аппаратурной реализации макроопераций, содержит набор элементарных процессоров ЭП (рис.1.7), выполняющих простейшие элементарные операции типа арифметических; набор элементарных коммутаторов ЭК, обеспечивающих соединение ЭП в схему, аппаратурно реализующую крупную операцию (макрооперацию).

Далее имеется набор секторов памяти операции ПО, обеспечивающих настройку ЭП на соответствующие элементарные операции; набор секторов памяти коммутаций ПК, определяющих настройку ЭК на аппаратную реализацию в ЭП необходимых макроопераций; набор секторов оперативной памяти ОП, предназначенных для хранения обрабатываемых данных.

Программирование макроопераций в процессоре с программируемой структурой осуществляется настройкой ЭП на требуемые элементарные операции с помощью ПО и образования необходимых каналов связи между ЭП путем настройки элементарных коммутаторов ЭК с помощью ПК (ШНЭП – шина набора элементарных процессоров, ШНЭК – шина набора элементарных коммутаторов, ШУР – шина управления режимами, ШД – шина данных).

Рис.1.7 Секционированная многопроцессорная система

Типовые структурные схемы макрокоммутатора, локальной макропамяти и макропроцессорной секции приведены ниже (рис 1.8, 1.9, 1.10).

Здесь МК – макрокоммутатор; ПМК – память макрокоммутатора; ЛМП – локальная макропамять; ЭП – элементарный процессор; ПЭО – память элементарных операций; ПЭК – память элементарных коммутаций; ШУ – шина управления. ЭП может быть разных типов, например ЭАП – элементарные арифметические процессоры; ЭЛП – элементарные логические процессоры; ЭИП – элементарные интегрирующие процессоры (рис. 1.11).

.10 Структура

макропроцессорной

секции

1.11

Типы элементарных процессоров

Если объединить несколько макропроцессорных секций с помощью макрокоммутаторов, то получится макропроцессор с программируемой структурой. Структурная схема такого макропроцессора на 8 элементарных процессоров приведена на рис. 1.12.

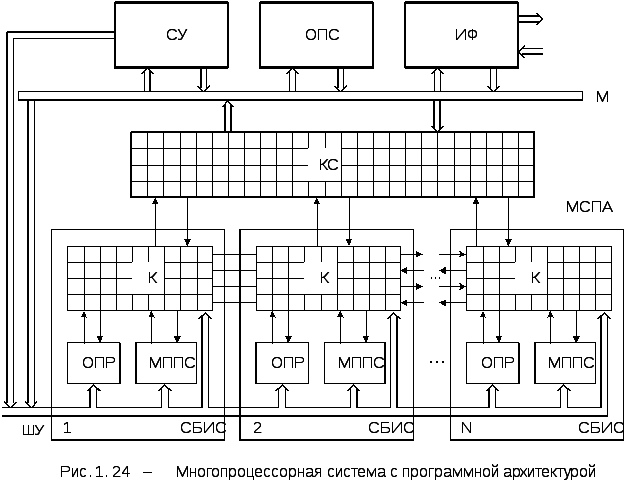

Структурная схема многопроцессорных систем с программной архитектурой на типовых макропроцессорах приведена на рис. 1.13. Здесь:

СУ – система управления; ОПС – оперативная память системы;

ИФ – интерфейсная система; М – магистраль системы;

КС – коммутирующая система; К – макрокоммутатор;

ОРП – оперативная распределённая память;

МППС – макропроцессор с программной структурой;

ШУ – шина управления;

СБИС – сверхбольшая интегральная схема макросекции.

Процессоры с программируемой структурой не только решают задачу аппаратурной реализации макрооперации и их структурного программирования, но и одновременно создают основу для перехода от внутренних машинных языков низкого уровня к машинным языкам высокого уровня, которые приближаются к внешним языкам высокого уровня и тем самым упрощают трансляцию и программирование.

Рис. 1.13

Структурная

схема многопроцессорной системы

Эта структурная схема и представляет собой вариант структурной схемы многопроцессорной вычислительной системы, построенной в соответствии с описанной концепцией: с гибкой программируемой архитектурой, мощной коммутационной системой, распределенной памятью РП и процессорами П, выполняющими макрооперации аппаратным методом за счет программирования их внутренней структуры.

Использование в многопроцессорных системах с программируемой архитектурой мощных коммутационных систем и процессоров с программируемой структурой, основанных на принципе аппаратурной реализации макроопераций, приводит к необходимости перехода от параллельных кодов, широко используемых в классических ЭВМ для представления, передачи и обработки информации, к последовательным кодам.

Действительно, если использовать в многопроцессорных системах с программируемой архитектурой параллельные коды, то это приведет к резкому увеличению затрат аппаратуры на синтез мощных коммутационных структур из-за необходимости параллельной передачи всех разрядов кодов в сотнях и даже тысячах каналов связи между процессорами, а также между процессорами и распределенной памятью. Такая же проблема возникает и в процессорах с программируемой структурой, в которых потребуется сильное усложнение системы коммутации и каналов связи, если информацию передавать параллельными кодами.

Переход к последовательным кодам устраняет эти факторы. Последовательные коды значительно уменьшают число необходимых коммутационных элементов и настраиваемых каналов связи в коммутационных системах, что приводит к более простым структурам процессоров, требующим меньшей степени интеграции БИС.

Однако следует иметь в виду, что выполнение операций над последовательными кодами путем их обработки младшими разрядами вперед в процессорах с программируемой структурой неприемлемо. Это является следствием того, что для выполнения многих арифметических и других операций при обработке младшими разрядами вперед требуется значительное время, в несколько раз превышающее время прохождения одного последовательного слова. Кроме того, для разных операций требуются разные затраты времени, что создает технические трудности при реализации макроопераций.

В связи с этим в многопроцессорных системах с программируемой архитектурой оказывается более удобным использовать знакоразрядную двоичную систему, которая позволяет выполнять операции над последовательными знакоразрядными кодами старшими разрядами вперед за время, необходимое для прохождения слова и нескольких дополнительных служебных тактов. При этом обеспечивается возможность по мере выдачи процессором старших разрядов результата сразу же использовать их в других процессорах, не ожидая появления младших разрядов. В результате снижается время на реализацию макроопераций и стандартизируется время, необходимое для выполнения различных операций, а также существенно уменьшается оборудование, необходимое для организации каналов связи.

Отличительной особенностью многопроцессорных систем с программируемой архитектурой является простота программирования, которая, по существу, сводится к двум простым этапам. Первый этап состоит в распределении в соответствии с решаемой задачей макроопераций между процессорами системы, это распределение выполняется на машинном языке высокого уровня, практически совпадающем с внешним входным языком высокого уровня. Второй этап заключается в настройке в соответствии со структурой задачи необходимых каналов связи между процессорами, а также между процессорами и распределенной памятью, что осуществляется программированием коммутационной структуры многопроцессорной системы. После этого осуществляется автоматический режим работы многопроцессорной системы, в течение которого в систему извне вводится необходимая информация. Одновременно с вводом данных информация перерабатывается и полученные результаты вычислений передаются далее. Перепрограммирование структуры процессоров и коммутации системы проводится только при переходе от одной задачи к другой.

Следует отметить такую возможность многопроцессорной системы с программируемой архитектурой, как работу со многими потребителями путем распределения между ними аппаратурных ресурсов системы, осуществляемую соответствующей настройкой коммутационной структуры. Здесь имеется принципиальное отличие от однопроцессорных ЭВМ и многопроцессорных систем с жесткой архитектурой, в которых при работе с многими потребителями осуществляется разделение времени, а не аппаратурных ресурсов.

Вследствие однотипности процессоров, однородности распределенной памяти и коммутационной структуры многопроцессорные системы с программируемой архитектурой отличаются высокой технологичностью и ремонтоспособностью, а также способностью к наращиванию аппаратурных ресурсов. Все структурные элементы многопроцессорных систем с программируемой архитектурой могут быть изготовлены в виде БИС или СБИС, причем число типов необходимых БИС и СБИС невелико.

Многопроцессорные системы с программируемой архитектурой отличаются высокой живучестью и надежностью – они продолжают эффективно работать при выходе из строя даже значительной части входящих в систему макропроцессоров, секторов распределенной памяти или локальных элементов коммутационной структуры.

Таким образом, вычислительные системы с программируемой архитектурой строятся на основе следующей концепции.

Архитектура многопроцессорной вычислительной системы не формируется полностью при разработке системы. Пользователь получает возможность программировать архитектуру вычислительной системы под соответствующий класс задач.

Процесс обработки информации в вычислительной системе строится на основе потока данных.

В вычислительной системе имеется распределенная память, обеспечивающая параллельный доступ к информации всех процессоров.

Обмен информацией между процессорами, а также между процессорами и распределенной памятью организуется структурным методом путем программирования прямых каналов связи в коммутационной системе.

Внутренний машинный язык является языком высокого уровня и основан на наборе макроопераций и стандартных макрокоммутаций.

Макрооперации в процессорах выполняются структурным методом путем программирования внутренней структуры процессора.

Суть программирования состоит в распределении в соответствии с задачей макрооператоров между процессорами и в организации необходимых каналов связи между процессорами.

Отметим положительные факторы концепции программируемой архитектуры.

Обеспечивается подстройка структуры вычислительной системы под структуру решаемой задачи, что облегчает распараллеливание вычислительного процесса.

Принцип потока данных значительно снижает затраты времени на обмен данными.

Распределенная память снижает конфликты между процессорами при обращении за информацией.

Программирование прямых каналов связи уменьшает затраты времени на организацию взаимодействия процессоров.

Внутренний машинный язык приближается к языкам высокого уровня, что упрощает трансляцию и повышает производительность.

Структурный метод обеспечивает аппаратную параллельную реализацию макрооператоров в процессорах, повышает производительность и облегчает взаимодействие процессоров.

Структурный метод программирования обеспечивает эффективное использование естественной параллельности задач, повышая тем самым производительность системы.

Обеспечивается линейная зависимость производительности от числа процессоров и тем самым реализуется максимальная производность.

Для микропроцессорных вычислительных систем с программной архитектурой производительность пропорциональна числу процессоров. Для МВС с фон-неймовской архитектурой при определенном числе процессов производительность системы снижается за счет эффекта гонок и конфликтов в таких системах. На рис. 1.14 приведены зависимости производительности многопроцессорных систем в зависимости от числа процессоров (графики 1) – для МВС фон-неймовской архитектуры и прямая (график 2) – для МВС с программируемой архитектурой.

Рис. 1.14. Производительность многопроцессорной системы в зависимости от числа процессоров

Одной из основных проблем при создании многопроцессорных вычислительных систем с программируемой архитектурой является решение вопроса об определении оптимального набора крупных математических операций, которые должен реализовать микропроцессор с программируемой структурой, являющийся основной составной частью МВС с программируемой архитектурой.