- •About This Manual

- •Additional Resources

- •Manual Contents

- •Conventions

- •Typographical

- •Online Document

- •Using Foundation Express with VHDL

- •Hardware Description Languages

- •Typical Uses for HDLs

- •Advantages of HDLs

- •About VHDL

- •Foundation Express Design Process

- •Using Foundation Express to Compile a VHDL Design

- •Design Methodology

- •Design Descriptions

- •Entities

- •Entity Generic Specifications

- •Entity Port Specifications

- •Architecture

- •Declarations

- •Components

- •Concurrent Statements

- •Constant Declarations

- •Processes

- •Signal Declarations

- •Subprograms

- •Type Declarations

- •Examples of Architectures for NAND2 Entity

- •Configurations

- •Packages

- •Using a Package

- •Package Structure

- •Package Declarations

- •Package Body

- •Resolution Functions

- •Data Types

- •Type Overview

- •Enumeration Types

- •Enumeration Overloading

- •Enumeration Encoding

- •Enumeration Encoding Values

- •Integer Types

- •Array Types

- •Constrained Array

- •Unconstrained Array

- •Array Attributes

- •Record Types

- •Record Aggregates

- •Predefined VHDL Data Types

- •Data Type BOOLEAN

- •Data Type BIT

- •Data Type CHARACTER

- •Data Type INTEGER

- •Data Type NATURAL

- •Data Type POSITIVE

- •Data Type STRING

- •Data Type BIT_VECTOR

- •Unsupported Data Types

- •Physical Types

- •Floating-Point Types

- •Access Types

- •File Types

- •Express Data Types

- •Subtypes

- •Expressions

- •Overview

- •Operators

- •Logical Operators

- •Relational Operators

- •Adding Operators

- •Unary (Signed) Operators

- •Multiplying Operators

- •Miscellaneous Arithmetic Operators

- •Operands

- •Operand Bit-Width

- •Computable Operands

- •Aggregates

- •Attributes

- •Expressions

- •Function Calls

- •Identifiers

- •Indexed Names

- •Literals

- •Numeric Literals

- •Character Literals

- •Enumeration Literals

- •String Literals

- •Qualified Expressions

- •Records and Fields

- •Slice Names

- •Limitations on Null Slices

- •Limitations on Noncomputable Slices

- •Type Conversions

- •Sequential Statements

- •Assignment Statements and Targets

- •Simple Name Targets

- •Indexed Name Targets

- •Slice Targets

- •Field Targets

- •Aggregate Targets

- •Variable Assignment Statements

- •Signal Assignment Statements

- •Variable Assignment

- •Signal Assignment

- •if Statements

- •Evaluating Conditions

- •Using the if Statement to Infer Registers and Latches

- •case Statements

- •Using Different Expression Types

- •Invalid case Statements

- •loop Statements

- •Basic loop Statement

- •while...loop Statements

- •for...loop Statements

- •Steps in the Execution of a for...loop Statement

- •for...loop Statements and Arrays

- •next Statements

- •exit Statements

- •Subprograms

- •Subprogram Always a Combinatorial Circuit

- •Subprogram Declaration and Body

- •Subprogram Calls

- •Procedure Calls

- •Function Calls

- •return Statements

- •Procedures and Functions as Design Components

- •Example with Component Implication Directives

- •Example without Component Implication Directives

- •wait Statements

- •Inferring Synchronous Logic

- •Combinatorial Versus Sequential Processes

- •null Statements

- •Concurrent Statements

- •Overview

- •process Statements

- •Combinatorial Process Example

- •Sequential Process Example

- •Driving Signals

- •block Statements

- •Nested Blocks

- •Guarded Blocks

- •Concurrent Versions of Sequential Statements

- •Concurrent Procedure Calls

- •Concurrent Signal Assignments

- •Simple Concurrent Signal Assignments

- •Conditional Signal Assignments

- •Selected Signal Assignments

- •Component Instantiation Statements

- •Direct Instantiation

- •generate Statements

- •for...generate Statements

- •Steps in the Execution of a for...generate Statement

- •Common Usage of a for...generate Statement

- •if...generate Statements

- •Register and Three-State Inference

- •Register Inference

- •The Inference Report

- •Latch Inference Warnings

- •Controlling Register Inference

- •Inferring Latches

- •Inferring Set/Reset (SR) Latches

- •Inferring D Latches

- •Inferring Master-Slave Latches

- •Inferring Flip-Flops

- •Inferring D Flip-Flops

- •Inferring JK Flip-Flops

- •Inferring Toggle Flip-Flops

- •Getting the Best Results

- •Understanding Limitations of Register Inference

- •Three-State Inference

- •Reporting Three-State Inference

- •Controlling Three-State Inference

- •Inferring Three-State Drivers

- •Inferring a Simple Three-State Driver

- •Three-State Driver with Registered Enable

- •Three-State Driver Without Registered Enable

- •Writing Circuit Descriptions

- •How Statements Are Mapped to Logic

- •Design Structure

- •Adding Structure

- •Using Variables and Signals

- •Using Parentheses

- •Using Design Knowledge

- •Optimizing Arithmetic Expressions

- •Arranging Expression Trees for Minimum Delay

- •Sharing Common Subexpressions

- •Changing an Operator Bit-Width

- •Using State Information

- •Propagating Constants

- •Sharing Complex Operators

- •Asynchronous Designs

- •Don’t Care Inference

- •Using Don’t Care Default Values

- •Differences Between Simulation and Synthesis

- •Synthesis Issues

- •Feedback Paths and Latches

- •Fully Specified Variables

- •Asynchronous Behavior

- •Understanding Superset Issues and Error Checking

- •Foundation Express Directives

- •Notation for Foundation Express Directives

- •Foundation Express Directives

- •Translation Stop and Start Pragma Directives

- •synthesis_off and synthesis_on Directives

- •Resolution Function Directives

- •Component Implication Directives

- •Foundation Express Packages

- •std_logic_1164 Package

- •std_logic_arith Package

- •Using the Package

- •Modifying the Package

- •Data Types

- •UNSIGNED

- •SIGNED

- •Conversion Functions

- •Arithmetic Functions

- •Example 10-1: Binary Arithmetic Functions

- •Example 10-2: Unary Arithmetic Functions

- •Comparison Functions

- •Example 10-3: Ordering Functions

- •Example 10-4: Equality Functions

- •Shift Functions

- •ENUM_ENCODING Attribute

- •pragma built_in

- •Type Conversion

- •numeric_std Package

- •Understanding the Limitations of numeric_std package

- •Using the Package

- •Data Types

- •Conversion Functions

- •Resize Function

- •Arithmetic Functions

- •Comparison Functions

- •Defining Logical Operators Functions

- •Shift Functions

- •Rotate Functions

- •Shift and Rotate Operators

- •std_logic_misc Package

- •ATTRIBUTES Package

- •VHDL Constructs

- •VHDL Construct Support

- •Design Units

- •Data Types

- •Declarations

- •Specifications

- •Names

- •Identifiers and Extended Identifiers

- •Specifics of Identifiers

- •Specifics of Extended Identifiers

- •Operators

- •Shift and Rotate Operators

- •xnor Operator

- •Operands and Expressions

- •Sequential Statements

- •Concurrent Statements

- •Predefined Language Environment

- •VHDL Reserved Words

- •Examples

- •Moore Machine

- •Mealy Machine

- •Read-Only Memory

- •Waveform Generator

- •Smart Waveform Generator

- •Definable-Width Adder-Subtracter

- •Count Zeros—Combinatorial Version

- •Count Zeros—Sequential Version

- •Soft Drink Machine—State Machine Version

- •Soft Drink Machine—Count Nickels Version

- •Carry-Lookahead Adder

- •Carry Value Computations

- •Implementation

- •Serial-to-Parallel Converter—Counting Bits

- •Input Format

- •Implementation Details

- •Serial-to-Parallel Converter—Shifting Bits

- •Programmable Logic Arrays

VHDL Reference Guide

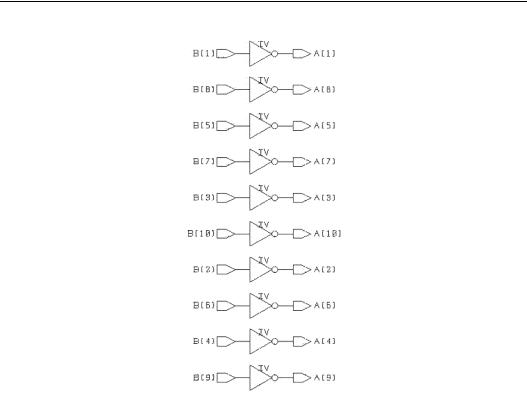

Figure 5-6 Circuit for for...loop Statement Operating on an

Entire Array

next Statements

The next statement skips execution to the next iteration of an enclosing loop statement, called label in the syntax, as follows.

next [ label ] [ when condition ] ;

•label: A next statement with no label terminates the current iteration of the innermost enclosing loop. When you specify a loop label, the current iteration of that named loop is terminated.

•when is an optional clause that executes its next statement when its condition (a Boolean expression) evaluates TRUE.

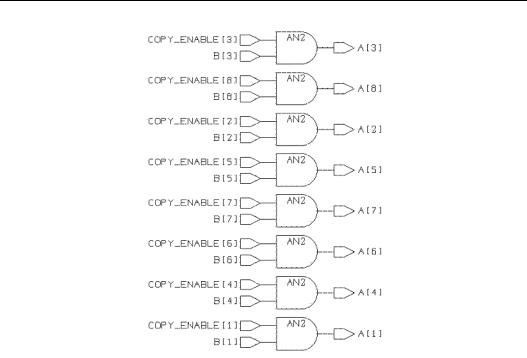

The following example uses the next statement to copy bits conditionally from bit vector B to bit vector A only when the next condition

5-20 |

Xilinx Development System |

Sequential Statements

evaluates to TRUE. The corresponding design is shown in the figure following the example.

entity example5_14 is port(

signal B, COPY_ENABLE: in BIT_VECTOR (1 to 8); signal A: out BIT_VECTOR (1 to 8)

);

end example5_14;

architecture behave of example5_14 is

begin

process (B, Copy_ENABLE) begin

A <= “00000000";

for I in 1 to 8 loop

next when COPY_ENABLE(I) = ’0’; A(I) <= B(I);

end loop;

end process; end behave;

VHDL Reference Guide |

5-21 |

VHDL Reference Guide

Figure 5-7 Circuit Design for next Statement

The example below shows the use of nested next statements in named loops. This example processes in the following manner.

•The first element of vector X against the first element of vector Y

•The second element of vector X against each of the first two elements of vector Y

•The third element of vector X against each of the first three elements of vector Y

The processing continues in this manner until it is completed.

signal X, Y: BIT_VECTOR(0 to 7);

A_LOOP: for I in X’range loop

. . .

B_LOOP: for J in Y’range loop

. . .

next A_LOOP when I < J;

. . .

end loop B_LOOP;

5-22 |

Xilinx Development System |

Sequential Statements

. . .

end loop A_LOOP;

exit Statements

The exit statement completes execution of an enclosing loop statement, called label in the syntax. The completion is conditional if the statement includes a condition, such as the when condition in the following syntax.

exit [ label ] [ when condition ] ;

•label: An exit statement with no label terminates the innermost enclosing loop. When you specify a loop label, the current iteration of than named loop is terminated, as shown in the previous example of a named next statement.

•when is an optional clause that executes its next statement when its condition (a Boolean expression) evaluates TRUE.

Note: The exit and next statements have identical syntax, and they both skip the remainder of the enclosing (or named) loop. The difference between the two statements is that exit terminates its loop and, then, continues with the next loop iteration (if any).

The example below compares two bit vectors. An exit statement exits the comparison loop when a difference is found. The corresponding circuit design is shown in the figure following this example.

entity example5 16 is port(

signal A, B: in BIT_VECTOR(1 downto 0); signal A_LESS_THAN_B: out Boolean;

);

end example5 16;

architecture behave of example5 16 is

begin

process (A, B) begin

A_LESS_THAN_B <= FALSE;

for I in 1 downto 0 loop

if (A(I) = ’1’ and B(I) = ’0’) then A_LESS_THAN_B <= FALSE;

exit;

VHDL Reference Guide |

5-23 |