- •1. Введение в анализ и синтез базовых узлов линейной обработки

- •1.1. Преобразование Лапласа как метод анализа линейных схем

- •1.2. Примеры расчета передаточных функций некоторых пассивных

- •1.2.1. Пассивный rc фильтр низких частот первого порядка

- •1.2.2. Простейший пассивный rlc фильтр низких частот

- •1.3. Примеры расчета передаточных функций простейших активных

- •1.3.1. Неинвертирующий усилитель

- •1.3.2. Инвертирующий усилитель

- •1.3.3. Активный инвертирующий интегратор

- •1.4. Введение в реализацию arc биквада

- •1.4.1. Принцип масштабирования пассивных элементов в arc фильтрах

- •1.5. Введение в концепцию переключаемых конденсаторов

- •1.5.1. Неинвертирующий переключаемый конденсатор с задержкой,

- •1.5.2. Неинвертирующий переключаемый конденсатор без задержки,

- •1.5.3. Инвертирующий пк интегратор без задержки, не чувствительный

- •1.5.4. Инвертирующий переключаемый конденсатор с задержкой,

- •1.5.5. Неинвертирующий пк интегратор с задержкой

- •1.6. Реализация биквада на базе переключаемых конденсаторах

- •1.7. Дискретизация аналогового сигнала. Идеальные выборки

- •1.7.1. Передаточная функция пк интегратора без задержки

- •1.7.2. Передаточная функция пк интегратора с задержкой

- •Модели элементов интегральных схем

- •3. Базовые элементы кмдп операционных усилителей

- •3.1. Простейший усилитель напряжения с общим истоком

- •3.1.1. Простейший усилительный каскад с общим истоком и активной

- •3.1.2. Малосигнальные характеристики простейшего кмдп усилителя

- •3.1.3. Частота единичного усиления простейшего усилителя

- •3.1.4. Соотношение малосигнальных параметров простейшего

- •3.1.5. Простейший усилитель в режиме большого сигнала

- •3.1.6. Расчет выходного сопротивления

- •3.1.7. Элементарный анализ величины входной емкости. Емкость Миллера

- •3.1.8. Пример топологии простейшего усилителя

- •3.2. Выходное сопротивление и коэффициент передачи каскада с диодом в нагрузке

- •3.3. Токовое зеркало

- •3.3.1. Формирование режимных потенциалов в простейшем усилителе с общим истоком

- •3.4. Истоковый повторитель

- •3.4.1. Выходное сопротивление и входная емкость истокового

- •3.5. Метод увеличения выходного сопротивления усилителя

- •3.6. Каскодный усилитель

- •3.6.1. Передаточная функция простейшего каскодного усилителя с идеальной токовой нагрузкой

- •3.6.2. Роль емкости в выходном узле каскодного усилителя.

- •3.6.3. Диапазон изменения выходного напряжения

- •3.6.4. Схемы формирования постоянного смещения на затворе каскодного транзистора.

- •3.6.5. Каскодное токовое зеркало

- •3.6.6. Самосмещаемое каскодное токовое зеркало

- •3.7. Концепция активного каскодного транзистора (материал для дополнительного изучения подготовленными студентами с использованием периодической литературы)

- •3.8. Дифференциальный каскад

- •3.8.1. Допустимый диапазон входного синфазного напряжения

- •3.8.2. Дифференциальный каскад как источник тока, управляемый входным напряжением. Несимметричный и симметричный входные сигналы

- •4. Архитектуры кмдп операционных усилителей

- •4.1. Методика оценки малосигнальных характеристик операционного усилителя

- •4.1.1. Методика замены нескольких действительных неосновных полюсов в передаточной функции операционного усилителя одним «эффективным» неосновным полюсом

- •4.1.2. Расчет запаса фазы операционного усилителя с действительными

- •4.2. Однокаскадные операционные усилители как операционные

- •4.2.1. «Телескопический» оитун

- •4.2.1.1. Базовые характеристики «телескопического» оитун

- •4.2.1.2. Упрощенная методика расчета фазы в «телескопическом» усилителе

- •4.2.1.3. Оценка частот неосновных полюсов «телескопического» оитун

- •4.2.1.4. Анализ переходных процессов

- •4.2.2. «Согнутый» каскодный оитун с р-канальным входом

- •4.2.2.1. Диапазоны входного синфазного и выходного напряжений

- •4.2.2.2. Режим малого сигнала

- •4.2.2.3. Переходной процесс в режиме большого сигнала

- •4.2.3. «Согнутый» каскодный оитун с n-канальным входом

- •4.3. Двухкаскадный операционный усилитель (оитун)

- •4.3.1. Базовая схема двухкаскадного оитун

- •4.3.2. Эквивалентная малосигнальная схема двухкаскадного усилителя

- •4.3.3. Передаточная функция двухкаскадного усилителя

- •4.3.4. Соотношение частот неосновного полюса, нуля и частоты единичного усиления

- •4.3.5. Частота единичного усиления двухкаскадного оитун

- •4.3.7. Реакция двухкаскадного оитун на большой входной сигнал.

- •4.3.8. Реакция двухкаскадного оитун на большой синусоидальный

- •4.3.9. Распространенная архитектура двухкаскадного оитун

- •5. Шум и его анализ в кмдп аналоговых имс

- •5.1. Основные определения

- •5.1.1. Cуммирование шумов

- •5.1.2. Анализ шума в частотной области

- •5.2. Пример расчета шума arc фильтра первого порядка

- •5.2.1. Реакция на шумовой источник тока

- •5.2.2. Реакция на шумовой источник тока

- •5.2.3. Реакция на шумовой источник напряжения

- •5.4. Приведенный ко входу собственный «белый» шум повторителя

- •5.5. Собственный шум многокаскадного усилителя

- •5.6. Шум каскодного усилителя

- •6. Полностью дифференциальные оитун

- •6.1. Базовая архитектура полностью дифференциальных схем

- •6.2. Принципиальные преимущества полностью дифференциальных схем

- •6.2.1. Зависимость потенциала общего истока дифкаскада от сигнала

- •6.3. Принципиальные недостатки полностью дифференциальных схем

- •6.4. Варианты непрерывных во времени схем синфазной обратной связи (сос).

- •6.4.1. Схема с ограниченным диапазоном входных сигналов.

- •6.4.2. Непрерывная во времени cхема сос с максимальным диапазоном

- •6.4.3. Варианты схем синфазной обратной связи на базе переключаемых конденсаторов

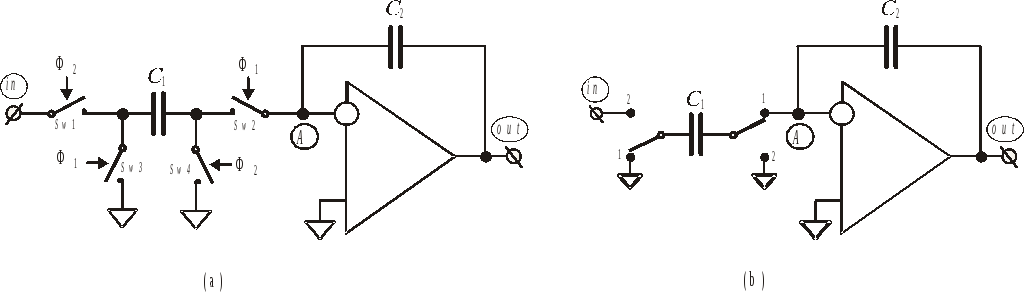

1.5.5. Неинвертирующий пк интегратор с задержкой

На рис. 1.14 представлена схема неинвертирующего интегратора с задержкой на базе инвертирующего ПК с задержкой. Рассматриваемый интегратор является неинвертирующим, поскольку состоит из инвертирующего ПК, подключенному к инвертирующему же входу операционного усилителя (ОУ).

Согласно

(1.42), в момент времени

![]() из правой обкладки конденсатора

из правой обкладки конденсатора![]() через ключSw2

в узел А инвертирующего входа ОУ вносится

заряд, равный

через ключSw2

в узел А инвертирующего входа ОУ вносится

заряд, равный

![]() .

Если

.

Если

![]() ,

то привнесенный в узел А заряд изменяет

потенциал узла в отрицательную сторону

и, соответственно, потенциал выходного

узла

,

то привнесенный в узел А заряд изменяет

потенциал узла в отрицательную сторону

и, соответственно, потенциал выходного

узла![]() изменяется в положительную сторону.

При этом в правую обкладку инвертирующего

конденсатора

изменяется в положительную сторону.

При этом в правую обкладку инвертирующего

конденсатора![]() вносится положительный заряд, и такой

же положительный заряд «выталкивается»

из левой обкладки в узел А, компенсируя

находящийся там отрицательный заряд,

«вытолкнутый» из левой обкладки

вносится положительный заряд, и такой

же положительный заряд «выталкивается»

из левой обкладки в узел А, компенсируя

находящийся там отрицательный заряд,

«вытолкнутый» из левой обкладки![]() .

.

Рис. 1.14. Неинвертирующий ПК интегратор с задержкой:

(а) с подробным изображением ключей; (b) с условными перекидными

ключами

При

идеальных ключах и ОУ процессы компенсации

и установления соответствующего

потенциала на выходе интегратора

происходят мгновенно, т.е. уже

непосредственно в момент времени

![]() выходной потенциал заканчивает изменяться

на величину, достаточную для компенсации

зарядов в узле А. В реальности процесс

компенсации проходит за промежуток

времени, равный половине периода, от

выходной потенциал заканчивает изменяться

на величину, достаточную для компенсации

зарядов в узле А. В реальности процесс

компенсации проходит за промежуток

времени, равный половине периода, от![]() до

до![]() ,

пока узел А ещеотрицателен

относительно неинвертирующего входа

ОУ. При положительном

изменении выходного потенциала и

сравнивании потенциалов обоих входов

ОУ (при отсутствии смещения нуля в

идеальном ОУ), величина положительного

заряда величины

,

пока узел А ещеотрицателен

относительно неинвертирующего входа

ОУ. При положительном

изменении выходного потенциала и

сравнивании потенциалов обоих входов

ОУ (при отсутствии смещения нуля в

идеальном ОУ), величина положительного

заряда величины

![]() ,

(1.45)

,

(1.45)

«вытолкнутого»

из левой обкладки конденсатора

![]() ,

сравнивается с величиной отрицательного

заряда, «вытолкнутого» из правой обкладки

,

сравнивается с величиной отрицательного

заряда, «вытолкнутого» из правой обкладки![]() и равного

и равного

![]() (1.46)

(1.46)

Таким образом, для изменения напряжения на выходе ПК интегратора с задержкой можно записать:

![]() (1.47а)

(1.47а)

Поскольку

в промежуток времени от

![]() до

до![]() ключSw2

разомкнут

и левая обкладка конденсатора

ключSw2

разомкнут

и левая обкладка конденсатора

![]() является плавающей, то заряд конденсатора

является плавающей, то заряд конденсатора![]() величины

величины![]() сохраняется до момента

сохраняется до момента

![]() .

По этой причине промежуток времени от

.

По этой причине промежуток времени от![]() до

до![]() называется временемхранения,

и выражение (1.47а) можно дополнить:

называется временемхранения,

и выражение (1.47а) можно дополнить:

![]() (1.47b)

(1.47b)

1.6. Реализация биквада на базе переключаемых конденсаторах

прямой заменой резисторов на переключаемые конденсаторы

Предположим, что

резисторы имитируются переключаемым

конденсатором (ПК) с частотой переключения

![]() ,

много большей наивысшей частоты

,

много большей наивысшей частоты![]() сигнала на входе фильтра. В этом случае

номинал

сигнала на входе фильтра. В этом случае

номинал![]() резистора вARC

реализации (в первом приближении)

заменяется на эффективное сопротивление,

определяемое выражением

резистора вARC

реализации (в первом приближении)

заменяется на эффективное сопротивление,

определяемое выражением

![]() ,

(1.48)

,

(1.48)

где номинал

![]() соответствующего переключаемого

конденсатора определяется из этого же

выражения (1.38). Одной из трудностей

классическойARC

реализации биквада является необходимость

наличия в составе биквада отрицательного

резистора. При использовании ОУ с

недифференциальными выходами требуется

введение в состав биквада дополнительного

активного инвертора сигнала (пример

активного инвертора – инвертирующий

усилитель на рисунке 1.4 с одинаковыми

резисторами

соответствующего переключаемого

конденсатора определяется из этого же

выражения (1.38). Одной из трудностей

классическойARC

реализации биквада является необходимость

наличия в составе биквада отрицательного

резистора. При использовании ОУ с

недифференциальными выходами требуется

введение в состав биквада дополнительного

активного инвертора сигнала (пример

активного инвертора – инвертирующий

усилитель на рисунке 1.4 с одинаковыми

резисторами

![]() и

и![]() ).

Красивым решением является использование

полностью дифференциальных операционных

усилителей (см. рис. 1.9), и, хотя такое

решение удваивает количество пассивных

компонентов, оно применяется практически

везде, где нужны фильтры на базе ПК, по

причине радикального снижения

чувствительности к помехам и увеличения

быстродействия.

).

Красивым решением является использование

полностью дифференциальных операционных

усилителей (см. рис. 1.9), и, хотя такое

решение удваивает количество пассивных

компонентов, оно применяется практически

везде, где нужны фильтры на базе ПК, по

причине радикального снижения

чувствительности к помехам и увеличения

быстродействия.

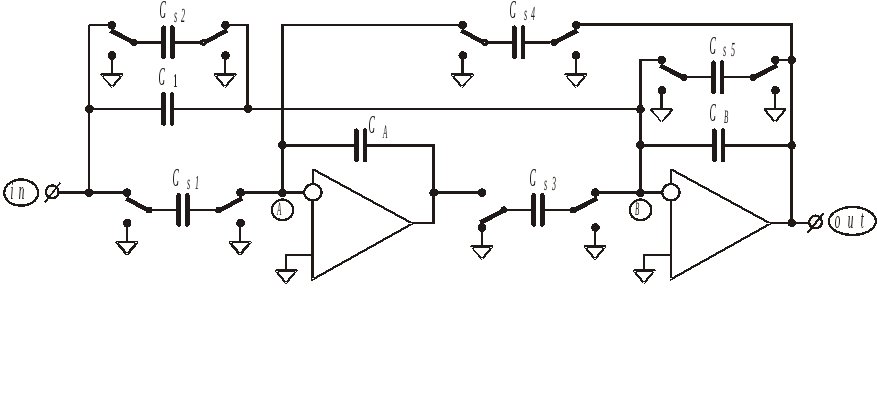

При проектировании биквада на базе переключаемых конденсаторов с ОУ, имеюших недифференциальные выходы, применение инверторов сигналя принципиально НЕ является необходимым, поскольку существует инвертор заряда, описанный выше как инвертирующий переключаемый конденсатор. Схема биквада на базе ОУ с недифференциальным выходом после прямой замены резисторов на ПК (включая неинвертирующие ПК и один инвертирующий), приведена на рис. 1.14.

Рис. 1.15. Реализация биквада при прямой замене резисторов на ПК.

Отметим, что у некоторых переключаемых конденсаторов, например, CS1 и СS2, левые обкладки имеют одинаковый потенциал в любом из положений ключей, что позволяет объединить эти обкладки и подключать к соответствующим узлам с помощью единственного ключа. Одинаковый потенциал имеют также правая обкладка CS1 и левая обкладка CS4, правые обкладки CS2 и CS3 и левая обкладка CS5, правые обкладки CS4 и CS5. Благодаря этому обстоятельству, схему можно упростить (оптимизировать). Оптимизированный вариант биквада на базе ПК представлен на рис. 1.15.

Рис. 1.16. Оптимизированная реализация биквада на рис. 1.15 на базе ОУ с одним выходом после объединения узлов с одинаковыми потенциалами.

Оптимизированная реализация полностью дифференциального ПК биквада представлена на рис. 1.17.

Рис. 1.17. Оптимизированная реализация полностью дифференциального ПК биквада