- •1. Введение в анализ и синтез базовых узлов линейной обработки

- •1.1. Преобразование Лапласа как метод анализа линейных схем

- •1.2. Примеры расчета передаточных функций некоторых пассивных

- •1.2.1. Пассивный rc фильтр низких частот первого порядка

- •1.2.2. Простейший пассивный rlc фильтр низких частот

- •1.3. Примеры расчета передаточных функций простейших активных

- •1.3.1. Неинвертирующий усилитель

- •1.3.2. Инвертирующий усилитель

- •1.3.3. Активный инвертирующий интегратор

- •1.4. Введение в реализацию arc биквада

- •1.4.1. Принцип масштабирования пассивных элементов в arc фильтрах

- •1.5. Введение в концепцию переключаемых конденсаторов

- •1.5.1. Неинвертирующий переключаемый конденсатор с задержкой,

- •1.5.2. Неинвертирующий переключаемый конденсатор без задержки,

- •1.5.3. Инвертирующий пк интегратор без задержки, не чувствительный

- •1.5.4. Инвертирующий переключаемый конденсатор с задержкой,

- •1.5.5. Неинвертирующий пк интегратор с задержкой

- •1.6. Реализация биквада на базе переключаемых конденсаторах

- •1.7. Дискретизация аналогового сигнала. Идеальные выборки

- •1.7.1. Передаточная функция пк интегратора без задержки

- •1.7.2. Передаточная функция пк интегратора с задержкой

- •Модели элементов интегральных схем

- •3. Базовые элементы кмдп операционных усилителей

- •3.1. Простейший усилитель напряжения с общим истоком

- •3.1.1. Простейший усилительный каскад с общим истоком и активной

- •3.1.2. Малосигнальные характеристики простейшего кмдп усилителя

- •3.1.3. Частота единичного усиления простейшего усилителя

- •3.1.4. Соотношение малосигнальных параметров простейшего

- •3.1.5. Простейший усилитель в режиме большого сигнала

- •3.1.6. Расчет выходного сопротивления

- •3.1.7. Элементарный анализ величины входной емкости. Емкость Миллера

- •3.1.8. Пример топологии простейшего усилителя

- •3.2. Выходное сопротивление и коэффициент передачи каскада с диодом в нагрузке

- •3.3. Токовое зеркало

- •3.3.1. Формирование режимных потенциалов в простейшем усилителе с общим истоком

- •3.4. Истоковый повторитель

- •3.4.1. Выходное сопротивление и входная емкость истокового

- •3.5. Метод увеличения выходного сопротивления усилителя

- •3.6. Каскодный усилитель

- •3.6.1. Передаточная функция простейшего каскодного усилителя с идеальной токовой нагрузкой

- •3.6.2. Роль емкости в выходном узле каскодного усилителя.

- •3.6.3. Диапазон изменения выходного напряжения

- •3.6.4. Схемы формирования постоянного смещения на затворе каскодного транзистора.

- •3.6.5. Каскодное токовое зеркало

- •3.6.6. Самосмещаемое каскодное токовое зеркало

- •3.7. Концепция активного каскодного транзистора (материал для дополнительного изучения подготовленными студентами с использованием периодической литературы)

- •3.8. Дифференциальный каскад

- •3.8.1. Допустимый диапазон входного синфазного напряжения

- •3.8.2. Дифференциальный каскад как источник тока, управляемый входным напряжением. Несимметричный и симметричный входные сигналы

- •4. Архитектуры кмдп операционных усилителей

- •4.1. Методика оценки малосигнальных характеристик операционного усилителя

- •4.1.1. Методика замены нескольких действительных неосновных полюсов в передаточной функции операционного усилителя одним «эффективным» неосновным полюсом

- •4.1.2. Расчет запаса фазы операционного усилителя с действительными

- •4.2. Однокаскадные операционные усилители как операционные

- •4.2.1. «Телескопический» оитун

- •4.2.1.1. Базовые характеристики «телескопического» оитун

- •4.2.1.2. Упрощенная методика расчета фазы в «телескопическом» усилителе

- •4.2.1.3. Оценка частот неосновных полюсов «телескопического» оитун

- •4.2.1.4. Анализ переходных процессов

- •4.2.2. «Согнутый» каскодный оитун с р-канальным входом

- •4.2.2.1. Диапазоны входного синфазного и выходного напряжений

- •4.2.2.2. Режим малого сигнала

- •4.2.2.3. Переходной процесс в режиме большого сигнала

- •4.2.3. «Согнутый» каскодный оитун с n-канальным входом

- •4.3. Двухкаскадный операционный усилитель (оитун)

- •4.3.1. Базовая схема двухкаскадного оитун

- •4.3.2. Эквивалентная малосигнальная схема двухкаскадного усилителя

- •4.3.3. Передаточная функция двухкаскадного усилителя

- •4.3.4. Соотношение частот неосновного полюса, нуля и частоты единичного усиления

- •4.3.5. Частота единичного усиления двухкаскадного оитун

- •4.3.7. Реакция двухкаскадного оитун на большой входной сигнал.

- •4.3.8. Реакция двухкаскадного оитун на большой синусоидальный

- •4.3.9. Распространенная архитектура двухкаскадного оитун

- •5. Шум и его анализ в кмдп аналоговых имс

- •5.1. Основные определения

- •5.1.1. Cуммирование шумов

- •5.1.2. Анализ шума в частотной области

- •5.2. Пример расчета шума arc фильтра первого порядка

- •5.2.1. Реакция на шумовой источник тока

- •5.2.2. Реакция на шумовой источник тока

- •5.2.3. Реакция на шумовой источник напряжения

- •5.4. Приведенный ко входу собственный «белый» шум повторителя

- •5.5. Собственный шум многокаскадного усилителя

- •5.6. Шум каскодного усилителя

- •6. Полностью дифференциальные оитун

- •6.1. Базовая архитектура полностью дифференциальных схем

- •6.2. Принципиальные преимущества полностью дифференциальных схем

- •6.2.1. Зависимость потенциала общего истока дифкаскада от сигнала

- •6.3. Принципиальные недостатки полностью дифференциальных схем

- •6.4. Варианты непрерывных во времени схем синфазной обратной связи (сос).

- •6.4.1. Схема с ограниченным диапазоном входных сигналов.

- •6.4.2. Непрерывная во времени cхема сос с максимальным диапазоном

- •6.4.3. Варианты схем синфазной обратной связи на базе переключаемых конденсаторов

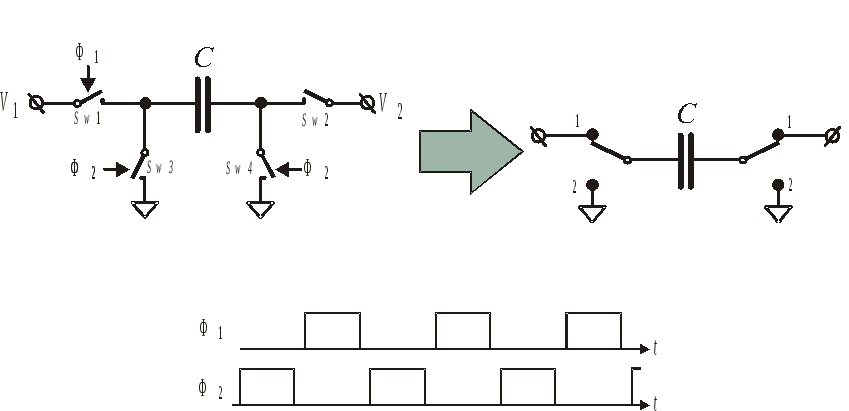

1.5.2. Неинвертирующий переключаемый конденсатор без задержки,

не чувствительный к паразитным емкостям

Для

устранения влияния нелинейных паразитных

конденсаторов на эффективную емкость

переключаемого конденсатора (ПК),

предложена другая схема коммутации ПК,

представленная на рис. 1.11. Здесь

![]() и

и![]() – паразитные ёмкости аналоговых ключей,

подключенные соответственно к левой и

правой обкладкам ПК.

– паразитные ёмкости аналоговых ключей,

подключенные соответственно к левой и

правой обкладкам ПК.

Требуется

передать заряд из положительного

(относительно аналоговой земли) источника

напряжения

![]() в другой источник

в другой источник![]() произвольного знака и произвольной

величины. Как и для ПК на Рис. 1.10, замкнутые

состояния ключей, управляемые тактами

Ф1

и

Ф2,

не перекрываются.

произвольного знака и произвольной

величины. Как и для ПК на Рис. 1.10, замкнутые

состояния ключей, управляемые тактами

Ф1

и

Ф2,

не перекрываются.

Рис. 1.11. Инвертирующий переключаемый конденсатор без задержки, не чувствительный к паразитным емкостям.

(А)

Подготовительный полупериод от

![]() до

до![]() .

Состояние тактовых сигналов: Ф2

=1 и Ф1

=0, т.е. ключи,

Sw3

и Sw4

замкнуты, а ключи Sw1

и Sw2

–

разомкнуты. При этом:

.

Состояние тактовых сигналов: Ф2

=1 и Ф1

=0, т.е. ключи,

Sw3

и Sw4

замкнуты, а ключи Sw1

и Sw2

–

разомкнуты. При этом:

– конденсатор

С1

приведен в исходное состояние, т.е. обе

обкладки принимают нулевой потенциал

аналоговой земли и разряжаются. Любые

заряды, бывшие на обеих обкладках

конденсатора, уходят в источники

напряжения аналоговой земли, и в

результате приведен в исходное состояние.

Паразитные конденсаторы

![]() и

и![]() также разряжены до нуля.

также разряжены до нуля.

(В)

Рабочий такт в момент времени

![]() .

Состояние тактовых сигналов: Ф1

=1 и Ф2

=0, т.е. ключи,

Sw1

и Sw2

замкнуты,

а ключи Sw3

и Sw4

– разомкнуты. При этом левая обкладка

конденсатора

заряжается до

.

Состояние тактовых сигналов: Ф1

=1 и Ф2

=0, т.е. ключи,

Sw1

и Sw2

замкнуты,

а ключи Sw3

и Sw4

– разомкнуты. При этом левая обкладка

конденсатора

заряжается до

![]() зарядом

зарядом![]() .

Поскольку конденсатор в любой момент

времени должен в целом быть электронейтральным

(в макроскопическом смысле), такой же

заряд, идентичный и по величине и по

знаку уходит («выталкивается») из правой

обкладки (с другой стороны, это эквивалентно

приходу на правую обкладку заряда той

же величины, но противоположного по

знаку). В результате в момент времени

.

Поскольку конденсатор в любой момент

времени должен в целом быть электронейтральным

(в макроскопическом смысле), такой же

заряд, идентичный и по величине и по

знаку уходит («выталкивается») из правой

обкладки (с другой стороны, это эквивалентно

приходу на правую обкладку заряда той

же величины, но противоположного по

знаку). В результате в момент времени![]() через ключSw2

в

источник V2

из

правой обкладки конденсатора

через ключSw2

в

источник V2

из

правой обкладки конденсатора

![]() «выталкивается» заряд, по величине и

по знаку идентичный заряду, пришедшему

из источника

«выталкивается» заряд, по величине и

по знаку идентичный заряду, пришедшему

из источника

![]() на зарядку левой обкладки. Очевидно,

что настоящий ПК должен быть назван

«неинвертирующим

ПК без задержки»,

т.е.

на зарядку левой обкладки. Очевидно,

что настоящий ПК должен быть назван

«неинвертирующим

ПК без задержки»,

т.е.

![]() .

(1.39)

.

(1.39)

Что касается паразитных конденсаторов, то

(С)

паразитный конденсатор

![]() перезаряжается только от входного

источникаV1

и, очевидно, не влияет на величину заряда,

«вытолкнутого» в источник V2

и

перезаряжается только от входного

источникаV1

и, очевидно, не влияет на величину заряда,

«вытолкнутого» в источник V2

и

(D)

паразитный

конденсатор

![]() в обоих случаях, и приФ1

=1, и

при Ф2

=1,

разряжается

только до нулевого потенциала, т.е не

перезаряжается.

Очевидно, что рассматриваемый переключаемый

конденсатор на рис. 3.11 не

зависит от паразитных емкостей.

в обоих случаях, и приФ1

=1, и

при Ф2

=1,

разряжается

только до нулевого потенциала, т.е не

перезаряжается.

Очевидно, что рассматриваемый переключаемый

конденсатор на рис. 3.11 не

зависит от паразитных емкостей.

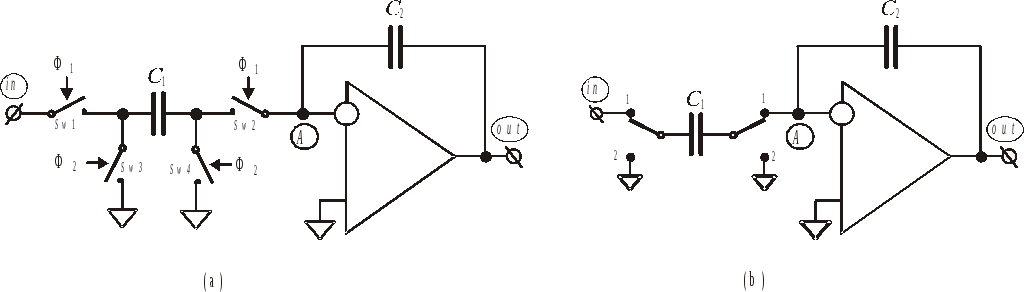

1.5.3. Инвертирующий пк интегратор без задержки, не чувствительный

к паразитным емкостям

Рассмотрим работу интегратора, роль резистора в котором выполняет неинвертирующий ПК без задержки, не чувствительный к паразитным емкостям. Рассматриваемый интегратор является инвертирующим, поскольку состоит из неинвертирующего ПК, подключенному к инвертирующему входу операционного усилителя ОУ.

В целях упрощения анализа операционный усилитель является идеальным, т.е. в нем отсутствует смещение нуля, отсутствует чувствительность к синфазной помехе, и в бесконечной полосе частот ОУ имеет бесконечное усиление. Рассматриваемый интегратор изображен на рис. 1.12.

Рис. 1.12. Инвертирующий интегратор без задержки:

(а) с подробным изображением ключей; (b) с условными перекидными

ключами

При анализе будем руководствоваться соображениями, приведшими к выражению (1.39).

Итак,

в момент времени

![]() интегратор подключается к входному

напряжению

интегратор подключается к входному

напряжению![]() ,

и заряд

,

и заряд![]() через ключSw2

«выталкивается» из правой обкладки

конденсатора

через ключSw2

«выталкивается» из правой обкладки

конденсатора

![]() в узел А, являющимся инвертирующим

входом ОУ.

в узел А, являющимся инвертирующим

входом ОУ.

Пусть

для определенности

![]() ,

т.е. входной потенциал более положителен,

чем потенциал аналоговой земли, равный

половине напряжения питания. В этом

случае пришедший в узел А заряд также

положителен, и потенциал этого узла

становится более положительным

относительно потенциала «аналоговой

земли». Поскольку неинвертирующий вход

ОУ подключен к аналоговой земле, а

инвертирующий вход стал более положительным

то потенциал выхода ОУ, являющийся также

выходом интегратора, изменяется вотрицательном

направлении. При этом в правую обкладку

интегрирующего конденсатора

,

т.е. входной потенциал более положителен,

чем потенциал аналоговой земли, равный

половине напряжения питания. В этом

случае пришедший в узел А заряд также

положителен, и потенциал этого узла

становится более положительным

относительно потенциала «аналоговой

земли». Поскольку неинвертирующий вход

ОУ подключен к аналоговой земле, а

инвертирующий вход стал более положительным

то потенциал выхода ОУ, являющийся также

выходом интегратора, изменяется вотрицательном

направлении. При этом в правую обкладку

интегрирующего конденсатора

![]() входит отрицательный заряд, что приводит

к «выталкиванию» из левой обкладки

входит отрицательный заряд, что приводит

к «выталкиванию» из левой обкладки![]() в узел А такого же по величине и знаку,

т.е.отрицательного

заряда, который компенсирует

положительный заряд, пришедший в узел

А из правой обкладки конденсатора

в узел А такого же по величине и знаку,

т.е.отрицательного

заряда, который компенсирует

положительный заряд, пришедший в узел

А из правой обкладки конденсатора

![]() .

Процесс компенсации проходит все время,

пока узел А еще положителен относительно

неинвертирующего входа ОУ (при идеальных

ОУ и ключах все происходит мгновенно).

При изменении выходного потенциала на

величину

.

Процесс компенсации проходит все время,

пока узел А еще положителен относительно

неинвертирующего входа ОУ (при идеальных

ОУ и ключах все происходит мгновенно).

При изменении выходного потенциала на

величину![]() потенциалы обоих входов ОУ сравниваются,

т.е. отрицательный заряд величины

потенциалы обоих входов ОУ сравниваются,

т.е. отрицательный заряд величины

![]() ,

(1.40)

,

(1.40)

«вытолкнутого»

из левой обкладки конденсатора

![]() ,

сравнивается с величиной положительного

заряда, «вытолкнутого» из правой обкладки

,

сравнивается с величиной положительного

заряда, «вытолкнутого» из правой обкладки![]() и равного

и равного

![]() (1.41)

(1.41)

Дополнительно

напоминаем, что и ключи, и операционный

усилитель предполагаются идеальными,

поэтому цепочка процессов (1) «выталкивание»

положительного заряда из правой обкладки

конденсатора

![]() через ключSw2

в узел А; (2) увеличение потенциала узла

А; (3) переходной процесс отрицательного

изменения выходного потенциала на

величину

через ключSw2

в узел А; (2) увеличение потенциала узла

А; (3) переходной процесс отрицательного

изменения выходного потенциала на

величину

![]() ;

(4) компенсация зарядов в узле А –

происходят мгновенно, в момент времени

;

(4) компенсация зарядов в узле А –

происходят мгновенно, в момент времени![]() подачи логической «единицы» на управляющие

входы ключейSw1

и Sw2

и подключения левой обкладки конденсатора

подачи логической «единицы» на управляющие

входы ключейSw1

и Sw2

и подключения левой обкладки конденсатора

![]() к входному сигналу.

к входному сигналу.

В

реальности все перечисленные процессы

происходят за промежуток времени от

![]() до

до![]() ,

пока Ф1=1

и замкнуты (проводят ток) ключи Sw1

и Sw2.

В связи с этим напряжение на выходе

интегратора устанавливается только к

моменту

,

пока Ф1=1

и замкнуты (проводят ток) ключи Sw1

и Sw2.

В связи с этим напряжение на выходе

интегратора устанавливается только к

моменту

![]() ,

и реальное минимальное время «отработки»

интегратором входного сигнала равно

половине периода тактового сигнала.

,

и реальное минимальное время «отработки»

интегратором входного сигнала равно

половине периода тактового сигнала.

В

следующую половину периода, когда Ф1=0,

интегрирующий конденсатор

![]() становится плавающим, поскольку при

идеальных ключах отсутствуют какие-либо

токи, разряжающие его левую обкладку.

В промежуток времени от

становится плавающим, поскольку при

идеальных ключах отсутствуют какие-либо

токи, разряжающие его левую обкладку.

В промежуток времени от![]() до

до![]() ,

называемом временемхранения,

заряд на

,

называемом временемхранения,

заряд на

![]() неизменен и неизменно напряжение на

выходе интегратора, т.е.

неизменен и неизменно напряжение на

выходе интегратора, т.е.![]() .

.

Поскольку

до

момента

![]() в конденсатореуже

находился некоторый начальный заряд

и, соответственно, на выходе интегратора

уже было начальное напряжение

в конденсатореуже

находился некоторый начальный заряд

и, соответственно, на выходе интегратора

уже было начальное напряжение

![]() ,

то можно записать:

,

то можно записать:

![]() (1.42)

(1.42)

Из (1.42) следует важный вывод: точность приращения выходного напряжения на выходе ПК интегратора за время, равное периоду частоты дискретизации, определяется точностью отношения номиналов конденсаторов, находящейся, как правило, в пределах от 0,05% до 0,2%. В ARC интеграторе непрерывного времени случайные разбросы номиналов резисторов достигают ±20%, а конденсаторов – около ±5%, поэтому разброс в постоянной времени, как правило, более ±20%.