- •Л.А. Торгонский

- •Содержание

- •1 Введение 6

- •2 Проектирование элементов и кристаллов биполярных имс 19

- •3 Элементы и кристаллы имс на полевых структурах 197

- •1 Введение

- •1.1 Термины и определения предметной области

- •1.2 Классификация микросхем

- •1.3 Обозначение имс

- •1.4 Конструкции и состав имс

- •1.5 Цели и задачи изучения дисциплины

- •1.6 Этапы проектирования микросхем

- •2 Проектирование элементов и кристаллов биполярных имс

- •2.2 Состав радиоэлементов бпт имс

- •2.3 Материалы имс

- •2.3.1 Введение

- •2.3.2 Кристаллические материалы имс

- •2.4 Изоляция элементов

- •2.5 Технологические слои структур бпт имс

- •2.6 Кремниевые пластины с эпс

- •2.7 Кремниевые пластины с эпс и скрытыми слоями

- •2.8 Кремниевые пластины с полной диэлектрической изоляцией карманов

- •2.9 Арсенид галлия в производстве имс

- •2.10 Технологические варианты структур бпт

- •2.11 Параметры слоев структур бпт имс

- •2.11.1 Оценка параметров слоя

- •2.12 Проектирование бпт

- •2.12.1 Введение

- •2.12.2 Функциональные параметры бпт

- •2.12.3 Расчетные соотношения оценки параметров бпт

- •2.12.4 Проектирование топологии бпт

- •2.12.5 Объемные формы и габаритные размеры элементов имс

- •2.12.6 Межэлектродные сопротивления бпт

- •2.12.7 Зависимость коэффициента передачи от топологии

- •2.12.8 Параметры быстродействия транзистора

- •2.13 Алгоритм проектирования бпт

- •2.14 Диоды ис

- •2.14.1 Общие замечания

- •2.14.2 Структуры интегральных диодов

- •2.14.3 Топологические конфигурации диодов

- •2.14.4 Проектные параметры диодов

- •2.14.5 Схема замещения диода

- •2.14.6 Алгоритм проектирования диодов

- •2.14.7 Диоды Шоттки в структурах бпт

- •2.15 Модификации бпт специального назначения

- •2.15.1 Общие сведения

- •2.15.2 Многоэмиттерный бпт

- •2.15.3 Многоколлекторный бпт

- •2.15.4 Транзисторы с контактными переходами Шоттки

- •2.15.5 Транзисторы с продольной структурой

- •2.15.6 Транзисторы со сверхтонкой базой

- •2.15.7 Транзисторы приборов совмещенных технологий

- •2.16 Резисторы полупроводниковых имс

- •2.16.1 Общие замечания

- •2.16.2 Структуры резисторов полупроводниковых имс

- •2.16.3 Топологические конфигурации резисторов

- •2.16.4 Проектные параметры резисторов

- •2.16.5 Расчетные соотношения

- •2.16.6 Алгоритм проектирования полупроводниковых резисторов

- •2.17 Конденсаторы биполярных имс

- •2.17.1 Общие сведения

- •2.17.2 Конденсаторы на основе р-n-перехода

- •2.17.3 Конденсаторы со структурой моп

- •2.17.4 Параметры конденсаторов бпт имс

- •2.17.5 Алгоритм проектирования конденсаторов бп имс

- •2.18 Соединения и контакты бпт имс

- •2.18.1 Общие сведения

- •2.18.2 Материалы и структуры соединений и контактов

- •2.18.3 Параметры и размеры соединений и контактов

- •2.19 Базовые элементы цифровых биполярных микросхем

- •2.19.1 Введение

- •2.19.2 Элементы транзисторно-транзисторной логики

- •2.19.3 Элементы ттл с приборами Шоттки

- •2.19.4 Элементы эмиттерно-связанной логики

- •2.19.5 Элементы инжекционной логики (и2л)

- •2.19.6 Элементы и2л с диодами Шоттки

- •2.20 Кристаллы ис

- •2.20.1 Введение

- •2.20.2 План кристалла

- •2.20.3 Сокращение потерь площади рабочей кристалла

- •2.20.4 Проектирование топологии ис на бпт

- •3 Элементы и кристаллы имс на полевых структурах

- •3.1 Проектирование полевых структур

- •3.1.1 Введение

- •3.1.2 Структуры и классификация мдп-транзисторов

- •3.1.3 Вольтамперные характеристики мдп-транзистров

- •3.1.4 Параметры мдп-транзистора и расчетные соотношения

- •3.1.5 Конструкции мдп-транзисторов

- •3.1.6 Алгоритмы проектирования мдп-транзисторов имс

- •3.2 Элементы цифровых имс на мдп-транзисторах

- •3.2.1 Введение

- •3.2.2 Защита конструкций мдп-микросхем

- •3.2.3 Логический инвертор с пассивной нагрузкой мдп

- •3.2.4 Логический инвертор с активной нагрузкой мдп

- •3.2.5 Логические элементы на мдп-структурах

- •3.2.6 Совмещенные биполярнополевые структуры

- •3.2.7 Полевые элементы устройств хранения информации

- •3.2.8 Проектирование топологии ис на мдп

- •3.3 Полевые структуры с зарядовой связью

- •3.3.1 Введение

- •3.3.2 Приборы с зарядовой связью (пзс)

- •3.3.3 Варианты структур элементов пзс

- •3.3.4 Ввод и детектирование заряда в пзс

- •3.3.5 Параметры пзс

- •3.3.6 Транзисторы с зарядовой связью (тзс)

- •3.3.7 «Пожарные» мдп-цепочки

- •3.3.8 Проектирование пзс

- •Список литературы

3.2.7 Полевые элементы устройств хранения информации

Базовыми элементами исполнения запоминающих устройств на МДП-транзисторах являются статические и динамические элементы памяти (ЭП) [3, 8, 11]. Схемы статических ЭП изображены на рисунках 3.27, а, б. В них применяются статические триггеры, составленные из активных МДП-транзисторов VT5, VT6 и динамических нагрузочных сопротивлений, исполненных на транзисторах VT3, VT4 c одним типом канала (см. рис. 3.27, а) и разным типом канала (см. рис. 3.27, б). Транзисторы VТ1 и VТ2 используются в качестве вентилей подключения к триггеру, В статическом состоянии адресная шина заземлена, и транзисторы VТ1, VТ2 закрыты, изолируя триггер от разрядных шин. На рисунке 3.27, в приведены временные диаграммы функционирования статического ЭП.

При считывании, с результате подачи импульса в адресную шину, транзисторы VТ1, VТ2 отпираются и контролируется ток, протекающий через открытую половину триггера. Подбором амплитуды напряжения считывания обеспечивается неизменное состояние триггера с тем, чтобы осуществить неразрушающее считывание. При записи одна из разрядных шин получает потенциал общего провода и в узлах триггера устанавливаются соответствующие уровни напряжений. Потребление энергии в статических режимах определяется нагрузочными транзисторами VТЗ, VТ4 и слабо не зависит от смены режимов считывания – записи.

Рисунок 3.27

Существенное снижение потребляемой мощности статических ЭП можно достигается в схеме на рисунке 3.27, б с применением МДП-транзисторов с каналами разных типов проводимостей, где один из транзисторов в последовательной паре «активный прибор-нагрузка» всегда открыт, а второй — всегда закрыт, поэтому потребляемая элементом мощность мала и определяется в статическом режиме лишь токами утечки.

Наряду с малым рассеиванием энергии, что обеспечивает их высокую надежность, к достоинствам таких схем относятся высокая степень использования напряжения питания (размах выходного сигнала практически равен этому напряжению), большая помехоустойчивость, способность работать от одного источника питания с низкими требованиями по стабильности напряжения. Недостатком КМДП схем, как отмечалось, являются повышение в сравнении с одноканальными структурами удельной стоимости ЭП и меньшая плотность упаковки.

Динамические интегральные ЭП на МДП-транзисторах позволяют добиться трех-, четырехкратного увеличения плотности упаковки информации, по сравнению со статическими ЭП, вместе с повышением быстродействия и снижением уровня рассеиваемой энергии.

Информация в динамическом ЭП сохраняется в виде заряда емкости С р-n-переходов МДП-транзисторов. Хранящуюся в динамическом ЭП информацию необходимо периодически обновлять, поскольку заряд такого запоминающего «конденсатора» постоянно уменьшается из-за действия токов утечки. Постоянная времени такого разряда лежит в пределах от нескольких миллисекунд до секунды при величине ёмкости 0,05–0,2 пф. Для обновления информации, помимо обычных источников питания, используют внешние источники тактирования или источники синхросигналов. Основной отличительной чертой динамического ЭП является количество используемых в нем транзисторов. На рисунке 3.28 показаны различные конфигурации динамического ЭП.

Рисунок 3.28

В однотранзисторном ЭП (см рис. 3.28, а) используются одна адресная шина и одна разрядная. Обе работают как при записи, так и при считывании. Запоминающим узлом является емкость стока МДП-транзистора. В таком ЗУ информация обновляется поочередно — по одному ряду матриц за цикл. Принцип работы ЭП основан на том, что при считывании возбужденная адресная шина передает заряд от запоминающего конденсатора в разрядную шину, а при записи устанавливается определенный уровень напряжения в разрядной шине, после чего возбуждается адресная шина. Считывание, как и обновление, происходит с разрушением информации, поэтому любой цикл в пределах матрицы включает обе операции — записи и считывания.

В двухтранзнсторном ЭП (см. рис. 3.28, б) имеются раздельные шины для записи и считывания. Эта схема также работает с разрушающим считыванием.

Варианты схем трехтранзисторных динамических ЭП изображены на рисунке 3.28, в. В них могут использоваться как раздельные, так и общие для записи и считывания адресные и разрядные шипы. Триггерные схемы в таких ЭП обычно не применяются. Состояние элемента определяется уровнем заряда паразитной емкости в запоминающем узле, которым является емкость затвора одного из МДП-транзисторов. Обновляется информация в ЭП путем ее считывания в усилитель обновления и повторной записи в ЭП, т.е. трехтранзисторные ЭП также функционируют в режиме разрушаюшего считывания.

Четырехтранзисторный ЭП (см. рис. 3.28, г) представляет собой триггер. В схеме используется одна общая адресная шина и дифференциальная пара информационных (разрядных) шин, используемых как при считывании, так и при записи. При обращении в процессе считывания связанные с адресной шиной транзисторы работают как нагрузочные сопротивления, образуется обычный триггер, информация считывается без ее разрушения. Необходимость в проведении регенеративной перезаписи отпадает, однако и в таком ЭП обновление информации необходимо, поскольку заряд паразитной емкости затвора понижается за счет токов утечки. Обновлению обычно одновременно подвергаются данные во всех ЭП, расположенных на одной интегральной подложке.

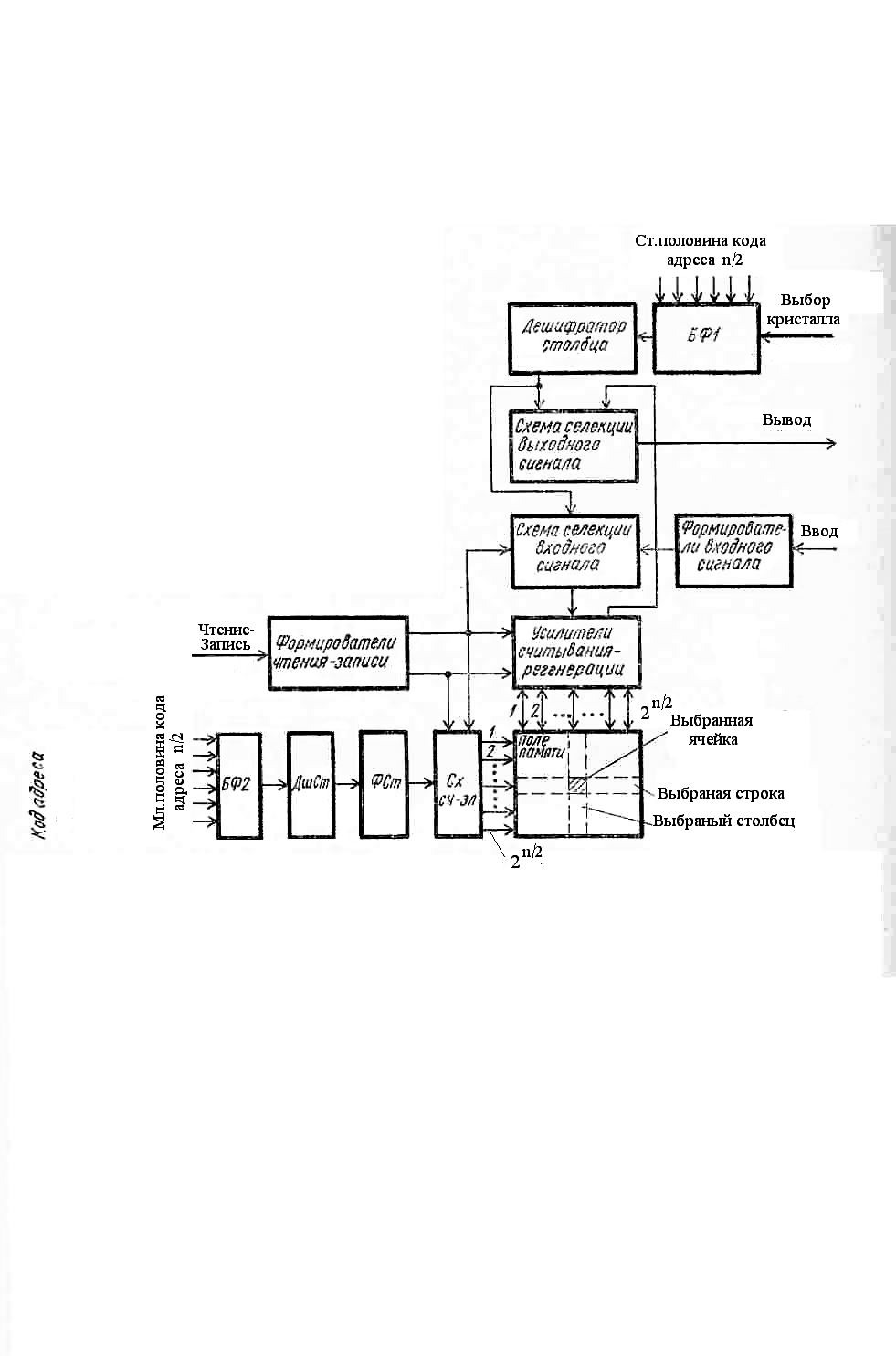

Структурная схема динамической МДП БИС, показана на рисунке 3.29. Массив ЭП организован в матрицу, содержащую n строки и n столбца. Младшая половина адресного кода декодируется дешифратором строк (ДшСт) для выбора определенной строки, а старшая половина разрядов декодируется для выбора столбцов. Ячейка памяти выбирается по сигналу совпадения выбранных строки и столбца. Сигнал выбор кристалла управляет буферными схемами ввода — вывода (БФ1, БФ2), разрешая при наличии сигнала Запись на входе Чтение — Запись занесение информации в выбранную ячейку памяти, а при наличии сигнала Чтение на этом же входе — вывод считанной информации.

Рисунок 3.29

Так как в динамических ЭП информация сохраняется определенное время, то ее необходимо восстанавливать, по крайней мере, через время, равное времени хранения. Режим восстановления данных (регенерации) реализуется в матричных организациях ЗУ (см. рис. 3.29) построчно перебором состояний разрядов младшей половины адресного кода при активных сигналах Выбор кристалла и Чтение.

Потребляемая мощность МДП ЗУ без потери хранимых данных может быть уменьшена путем понижения напряжения источника питания в режиме хранения. В режимах чтения, записи и регенерации значение напряжения источника питания должно быть восстановлено до номинального.