- •1 .Параллельный регистр на rs-триггерах.

- •2. Параллельный регистр на d-триггерах.

- •3. Разрядная схема параллельного регистра, реализующая запись с двух направлений.

- •4. Сдвигающий регистр.

- •5. Организация межрегистровых связей

- •6. Основные параметры и классификация счетчиков

- •8. Вычитающий счетчик с последовательным переносом на т-триггерах

- •Реверсивный счетчик на т-триггерах.

- •10.Счетчик с параллельным переносом на т-триггерах.

- •11. Структура счетчика с комбинированным переносом.

- •12. Счетчик со сквозным переносом на т-триггерах.

- •13. Двоично-кодированные счетчики на т-триггерах.

- •14. Кольцевой счетчик на т-триггерах.

- •15.Мультиплексор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •16. Схема мультиплексорного дерева

- •17. Демультиплексор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •18.Схема демультиплексорного дерева

- •1 9. Преобразователи кодов.

- •Шифратор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •22.Реализация демультиплексора с использованием дешифратора.

- •23 Реализация мультиплексора с использованием дешифратора.

- •Многоступенчатый дешифратор.

- •25. Полный двоичный дешифратор на базе двух двоично–десятичных де-шифраторов.

- •26. Цифровой компаратор. Таблица истинности. Математическое описание. Принципиальная схема

- •27. Счетчики в коде Грея

- •1. Счетчики в коде «1 из n»

- •3.Распределитель с автоматическим вхождением в рабочий цикл за 1 такт

- •4. Счетчик Джонсона.

- •5.Полиномиальные счетчики.

- •6. Схемы генераторов псевдослучайной последовательности (гпсп).

- •7. Арифметико-логические устройства (алу). Назначение и основные параметры.

- •8. Сумматоры. Алгоритм двоичного сложения.

- •9. Сумматоры. Сложение многоразрядных двоичных кодов.

- •11. Одноразрядный сумматор

- •12. Многоразрядный сумматор параллельного действия.

- •13. Многоразрядный сумматор последовательного действия.

- •14. Сумматор с параллельным переносом.

- •15.Сумматоры с цепным переносом.

- •16.Выполнение операций арифметического умножения.

- •17.Классификация запоминающих устройств.

- •18.Структура озу типа 2d.

- •19.Структура озу типа 3d.

- •20.Структура озу типа 2dm.

- •Запоминающие устройства типа

- •21.Масочные запоминающие устройства.

- •22.Матрица моп- транзисторных элементов зу.

- •23.Запоминающие устройства типа prom.

- •24/25.Запоминающие устройства типа eprom eeprom.

- •26.Статистические озу (sram).

- •27.Динамические озу(dram).

- •Запоминающие элементы

- •Основные сведения. Система параметров. Классификация

- •Параметры зу

- •Параметры зу

1. Счетчики в коде «1 из n»

Их применяют в синхронизации управления и др. цифровых устройствах. На их основе получают импульсную последовательность с заданными временными диаграммами. Для построения счетчика «1 из n» временные диаграммы разбивают на части – кванты, каждый из которых соответствует минимальному времени интервала временной диаграммы. В этом случае входную последовательность счетчика можно представить в виде генератора, частота которого = m/T , где m- число квантов в периоде Т.

Входные импульсы задающего генератора после прохождения счетчика «1 из n» распределяют каждый квант во времени и пространстве.

Часто счетчик «1 из n» называют разделителем тактовых сигналов(импульсов).

С четчик

«1 из n»

имеет 1 вход, на кот. подается импульсная

последовательность и n

выходов. На рисунке приведено устройство,

кот. реализует следующую функцию:

импульс попадает на i-й

канал. В случае, если пауза между выходным

значением отсутствует, то счетчик -

уровней, если паузы присутствуют -

распределитель импульсов. Распределитель

импульсов реализуется на основе

распределителя уровней путем включения

в выход цепи распределения уровней

коньюнкторов.

четчик

«1 из n»

имеет 1 вход, на кот. подается импульсная

последовательность и n

выходов. На рисунке приведено устройство,

кот. реализует следующую функцию:

импульс попадает на i-й

канал. В случае, если пауза между выходным

значением отсутствует, то счетчик -

уровней, если паузы присутствуют -

распределитель импульсов. Распределитель

импульсов реализуется на основе

распределителя уровней путем включения

в выход цепи распределения уровней

коньюнкторов.

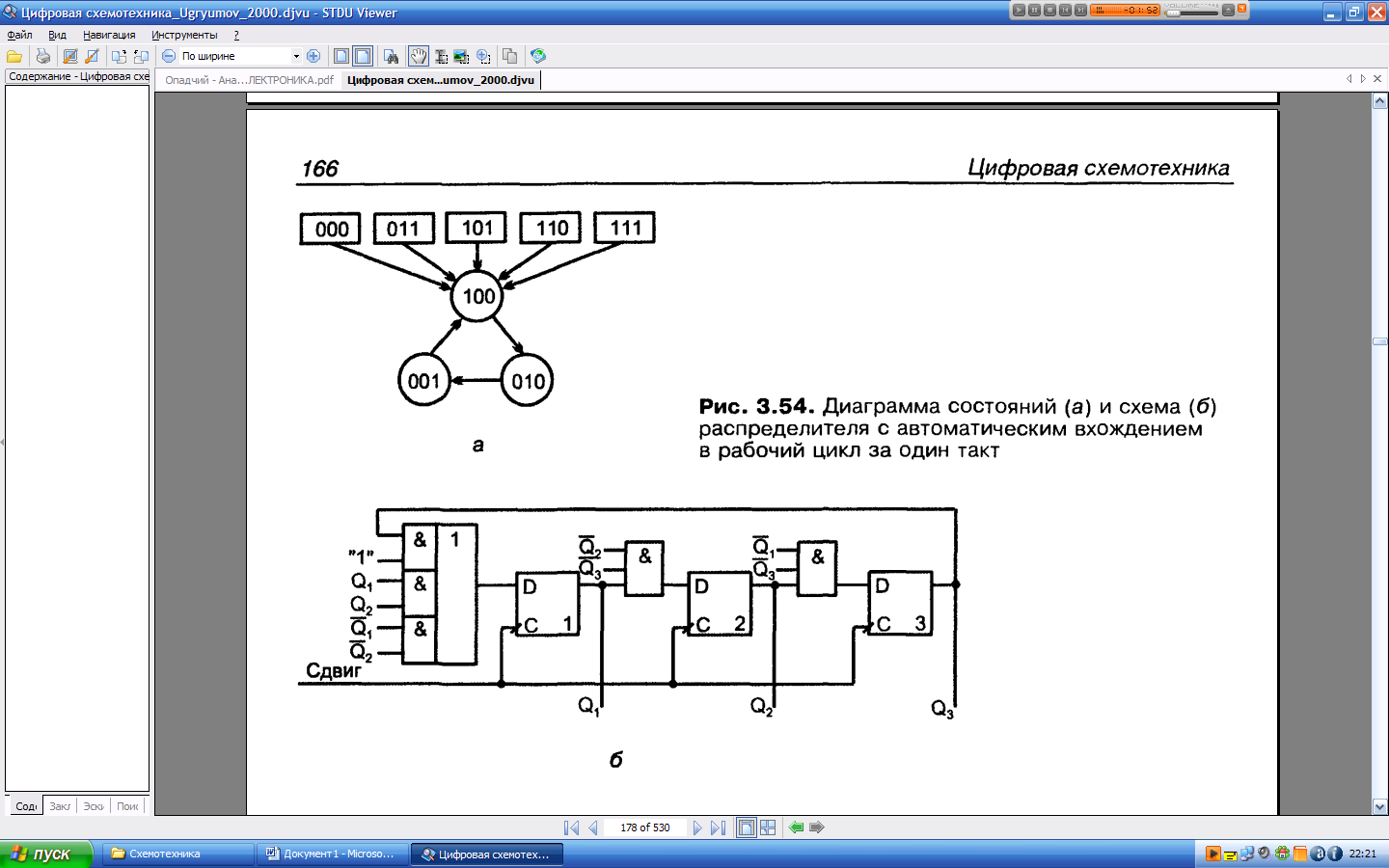

3.Распределитель с автоматическим вхождением в рабочий цикл за 1 такт

Распределителем тактов является сдвигающий регистр, замкнутый в кольцо, если записанное в регистр слово содержит всего одну единицу. При сдвигах единица перемещается с одного выхода на другой, циркулируя в кольце. Число выходов РТ =разрядности регистра. Недостаток схемы – потеря правильного функционирования при сбое. Если в силу каких-либо причин слово в рег-ре исказится, то возникшая ошибка станет постоянной. Схема не обладает свойством автозапуска.

Поэтому ставится задача быстрого исправления сбоев, причем в ближайшем такте. Для этого задают и реализовывают соответствующую диаграмму состояний распределителя. Пусть у нас трехканальный распределитель. Диагр. состояний приведена на рис.1. (кружками обозначены рабочие циклы, прямоугольниками – ложные состояния).

Э

той

диагр соответствует таблица истинности.

той

диагр соответствует таблица истинности.

Рис.1.

Выбираем для

построения схемы триггеры типа D,

учитывая,

что функция возбуждения этого триггера

![]() .

Исходя из табл, для функций

.

Исходя из табл, для функций

![]() имеем следующие соотношения

имеем следующие соотношения

Схема распределителя показана на следующем рисунке

Распределители на кольцевых регистрах применяются при малом числе выходных каналов, когда необходимость иметь по триггеру на каждый канал не ведет к чрезмерно большим аппаратурным затратам. Достоинством распределителей на кольцевых регистрах является отсутствие дешифраторов в их структуре и, как следствие, высокое быстродействие ( задержка перехода в новое состояние равна времени переключения триггера).