- •1 .Параллельный регистр на rs-триггерах.

- •2. Параллельный регистр на d-триггерах.

- •3. Разрядная схема параллельного регистра, реализующая запись с двух направлений.

- •4. Сдвигающий регистр.

- •5. Организация межрегистровых связей

- •6. Основные параметры и классификация счетчиков

- •8. Вычитающий счетчик с последовательным переносом на т-триггерах

- •Реверсивный счетчик на т-триггерах.

- •10.Счетчик с параллельным переносом на т-триггерах.

- •11. Структура счетчика с комбинированным переносом.

- •12. Счетчик со сквозным переносом на т-триггерах.

- •13. Двоично-кодированные счетчики на т-триггерах.

- •14. Кольцевой счетчик на т-триггерах.

- •15.Мультиплексор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •16. Схема мультиплексорного дерева

- •17. Демультиплексор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •18.Схема демультиплексорного дерева

- •1 9. Преобразователи кодов.

- •Шифратор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •22.Реализация демультиплексора с использованием дешифратора.

- •23 Реализация мультиплексора с использованием дешифратора.

- •Многоступенчатый дешифратор.

- •25. Полный двоичный дешифратор на базе двух двоично–десятичных де-шифраторов.

- •26. Цифровой компаратор. Таблица истинности. Математическое описание. Принципиальная схема

- •27. Счетчики в коде Грея

- •1. Счетчики в коде «1 из n»

- •3.Распределитель с автоматическим вхождением в рабочий цикл за 1 такт

- •4. Счетчик Джонсона.

- •5.Полиномиальные счетчики.

- •6. Схемы генераторов псевдослучайной последовательности (гпсп).

- •7. Арифметико-логические устройства (алу). Назначение и основные параметры.

- •8. Сумматоры. Алгоритм двоичного сложения.

- •9. Сумматоры. Сложение многоразрядных двоичных кодов.

- •11. Одноразрядный сумматор

- •12. Многоразрядный сумматор параллельного действия.

- •13. Многоразрядный сумматор последовательного действия.

- •14. Сумматор с параллельным переносом.

- •15.Сумматоры с цепным переносом.

- •16.Выполнение операций арифметического умножения.

- •17.Классификация запоминающих устройств.

- •18.Структура озу типа 2d.

- •19.Структура озу типа 3d.

- •20.Структура озу типа 2dm.

- •Запоминающие устройства типа

- •21.Масочные запоминающие устройства.

- •22.Матрица моп- транзисторных элементов зу.

- •23.Запоминающие устройства типа prom.

- •24/25.Запоминающие устройства типа eprom eeprom.

- •26.Статистические озу (sram).

- •27.Динамические озу(dram).

- •Запоминающие элементы

- •Основные сведения. Система параметров. Классификация

- •Параметры зу

- •Параметры зу

8. Сумматоры. Алгоритм двоичного сложения.

Сумматор – комбин-я схема, предназначенная для сложения чисел, кот. предст. в двоичном коде. Под сумматором поним. достаточно широкий спектр устройств от простейших комб-х схем до очень сложных цифровых узлов. Общее для них – ф-ция сложения двоичных чисел.

Алгоритм сложения двоичных чисел.

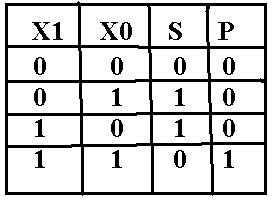

Т аблица

соотв. для одноразрядного сумматора:

аблица

соотв. для одноразрядного сумматора:

p – тип переноса

s – рез-т

Значение Р будет=1 тогда, когда сумма х1, х0 будет иметь 1 в старшем разряде.

Опишем логическую фун-ю работы сумматора:

![]() P=х1*х0

P=х1*х0

Таким образом для суммир. 2 однор-х чисел необходимо вып. опред. «Искл-е ИЛИ»

![]()

![]()

9. Сумматоры. Сложение многоразрядных двоичных кодов.

Сумматоры-это комбинац. схемы, предназначенные для сложения чисел,представленных в двоичном коде. При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и т.п. Под сумматорами понимают дост. большое кол-во устройств,общим для которых является функция сложения двоичных чисел.

В зависимости от системы счисления различают: двоичные; двоично-десятичные; десятичные; прочие (например, амплитудные).

По количеству одновременно обрабатываемых разрядов складываемых чисел: одноразрядные; многоразрядные.

По числу выводов: полусумматоры, одноразрядные, многоразрядные (последовательные и параллельные).

По способу тактирования: синхронные, асинхронные.

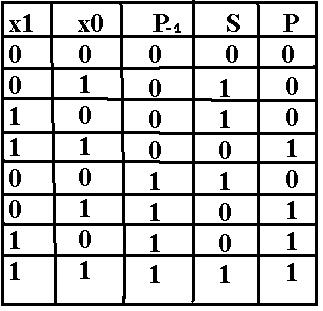

Табл. истинности для сложения многоразрядных двоичных кодов:

Функция,

опис. ТИ:

Функция,

опис. ТИ:

S=(x1![]() x0)*

x0)*![]() +(

+(![]() -1

– бит

переноса

-1

– бит

переноса

P=x1*x0+(x1 x0)* p-1

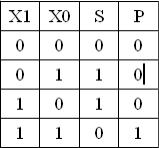

10. Двоичный полусумматор. Это устройство, предназначенное для сложения одноразрядных двоичных чисел, имеющее два входа и два выхода (s и p). Его таблица истинности:

(s

— результат, p — бит переноса). Его

логическая функция:

(s

— результат, p — бит переноса). Его

логическая функция:

s=┐x1*x0+x1*┐x0; p=x1*x0.

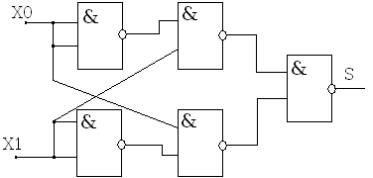

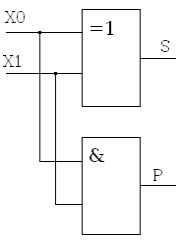

Принципиальная схема полусумматора в базисе «И-НЕ»:

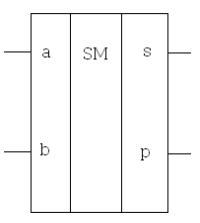

О бщая

схема полусумматора с учётом бита

переноса: УГО полусумматора:

бщая

схема полусумматора с учётом бита

переноса: УГО полусумматора:

Время выполнения операций: T=3*tcp

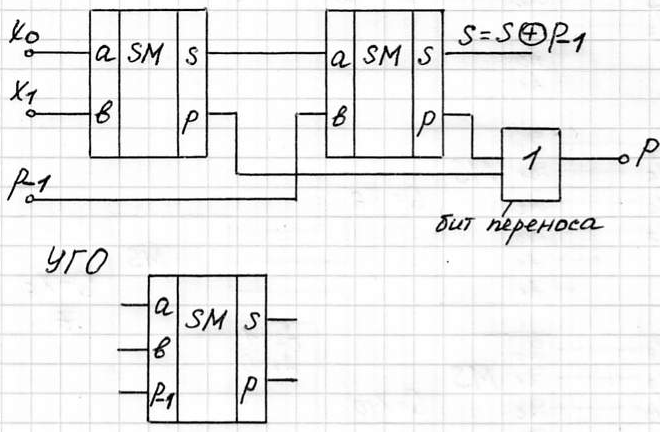

11. Одноразрядный сумматор

Сумматор - комбинационная схема, предназначенная для сложения чисел, представленных в двоичном коде.

Функция, описывающая работу одноразрядного сумматора:

![]()

![]()

Такая функция может быть реализована на логических элементах различного типа. Рассмотрим сумматор, построенный на основе полусумматоров.

А нализируя

аналитическую функцию одноразрядного

сумматора можно увидеть, что на основе

обычных логических элементов можно

реализовать более простую схему.

нализируя

аналитическую функцию одноразрядного

сумматора можно увидеть, что на основе

обычных логических элементов можно

реализовать более простую схему.

Время проведения операции в таком сумматоре будет определяться как:

tп∑=2*tп=6tsp

Бит переноса будет формироваться быстрее: 5tзад

12. Многоразрядный сумматор параллельного действия.

В зависимости от способа ввода разрядов слагаемых сумматоры делятся на два типа: послед-го и парал-го действия. В сумматоры 1го типа разряды чисел вводятся в послед. форме, т. е. разряд за разрядом (младшим разрядом вперед), в сумматоры 2го типа каждое из слагаемых подается в параллельной форме, т. е. одновременно всеми разрядами.

С умматор

параллельного действия

- состоит из отдельных разрядов, каждый

из которых содержит одноразрядный

сумматор: (рис).

умматор

параллельного действия

- состоит из отдельных разрядов, каждый

из которых содержит одноразрядный

сумматор: (рис).

При подаче слагаемых цифры их разрядов поступают на соответствующие одноразрядные сумматоры. Каждый из одноразрядных сумматоров формирует на своих выходах цифру соотв.разряда суммы и перенос, передаваемый на вход одноразрядного сумматора следующего (более старшего) разряда. Такая организация процесса организации переноса, называемая последовательным переносом, снижает быстродействие многоразрядных сумматоров, т.к. получение результата в старшем разряде сумматора обеспечивается только после завершения распространения переноса по всем разрядам.