- •1 .Параллельный регистр на rs-триггерах.

- •2. Параллельный регистр на d-триггерах.

- •3. Разрядная схема параллельного регистра, реализующая запись с двух направлений.

- •4. Сдвигающий регистр.

- •5. Организация межрегистровых связей

- •6. Основные параметры и классификация счетчиков

- •8. Вычитающий счетчик с последовательным переносом на т-триггерах

- •Реверсивный счетчик на т-триггерах.

- •10.Счетчик с параллельным переносом на т-триггерах.

- •11. Структура счетчика с комбинированным переносом.

- •12. Счетчик со сквозным переносом на т-триггерах.

- •13. Двоично-кодированные счетчики на т-триггерах.

- •14. Кольцевой счетчик на т-триггерах.

- •15.Мультиплексор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •16. Схема мультиплексорного дерева

- •17. Демультиплексор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •18.Схема демультиплексорного дерева

- •1 9. Преобразователи кодов.

- •Шифратор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •22.Реализация демультиплексора с использованием дешифратора.

- •23 Реализация мультиплексора с использованием дешифратора.

- •Многоступенчатый дешифратор.

- •25. Полный двоичный дешифратор на базе двух двоично–десятичных де-шифраторов.

- •26. Цифровой компаратор. Таблица истинности. Математическое описание. Принципиальная схема

- •27. Счетчики в коде Грея

- •1. Счетчики в коде «1 из n»

- •3.Распределитель с автоматическим вхождением в рабочий цикл за 1 такт

- •4. Счетчик Джонсона.

- •5.Полиномиальные счетчики.

- •6. Схемы генераторов псевдослучайной последовательности (гпсп).

- •7. Арифметико-логические устройства (алу). Назначение и основные параметры.

- •8. Сумматоры. Алгоритм двоичного сложения.

- •9. Сумматоры. Сложение многоразрядных двоичных кодов.

- •11. Одноразрядный сумматор

- •12. Многоразрядный сумматор параллельного действия.

- •13. Многоразрядный сумматор последовательного действия.

- •14. Сумматор с параллельным переносом.

- •15.Сумматоры с цепным переносом.

- •16.Выполнение операций арифметического умножения.

- •17.Классификация запоминающих устройств.

- •18.Структура озу типа 2d.

- •19.Структура озу типа 3d.

- •20.Структура озу типа 2dm.

- •Запоминающие устройства типа

- •21.Масочные запоминающие устройства.

- •22.Матрица моп- транзисторных элементов зу.

- •23.Запоминающие устройства типа prom.

- •24/25.Запоминающие устройства типа eprom eeprom.

- •26.Статистические озу (sram).

- •27.Динамические озу(dram).

- •Запоминающие элементы

- •Основные сведения. Система параметров. Классификация

- •Параметры зу

- •Параметры зу

18.Схема демультиплексорного дерева

П ри

передаче сигналов от нескольких

источников по одному каналу с разделением

по времени нужны не только мультиплексоры,

но и устр-ва обратного действия, которые

распределяют информацию из одного

источника(канала) между несколькими

приемниками, такие устр-ва называются

демультиплексорами.

ри

передаче сигналов от нескольких

источников по одному каналу с разделением

по времени нужны не только мультиплексоры,

но и устр-ва обратного действия, которые

распределяют информацию из одного

источника(канала) между несколькими

приемниками, такие устр-ва называются

демультиплексорами.

Особенностью демультиплексорного дерева является то, что все демультиплексоры, входящие в его состав должны иметь вход разрешения работы инверсный.

1 9. Преобразователи кодов.

В цифровой схемотехнике применяются различные типы кодирования информации. При работе ЭВМ используются прямой, обратный, дополнительный, двоично-десятичный и другие коды. При передаче информации по ЛС (линии связи) целесообразно использовать другое кодирование (помехозащищённое кодирование; сжимающие коды; коды, которые позволяют восстанавливать информацию при возникновении ошибки). В связи с этим всегда возникает задача преобразования из одного кода в другой. Такую задачу выполняют комбинационные схемы, которые называются преобразователями кодов (шифраторы/дешифраторы).

Преобразователем кода называется устройство, которое изменяет вид кодированной информации.

Как и всякое логическое устройство преобразователь кода характеризуется ТИ (таблицей истинности), которая ставит в соответствие значениям на выходе значения на входе устройства. В общем случае количество разрядных входов и выходов не совпадает. Самое главное, что такая таблица должна обеспечить однозначное соответствие различных комбинаций на входе и на выходе. Такая таблица является основой для синтеза устройства.

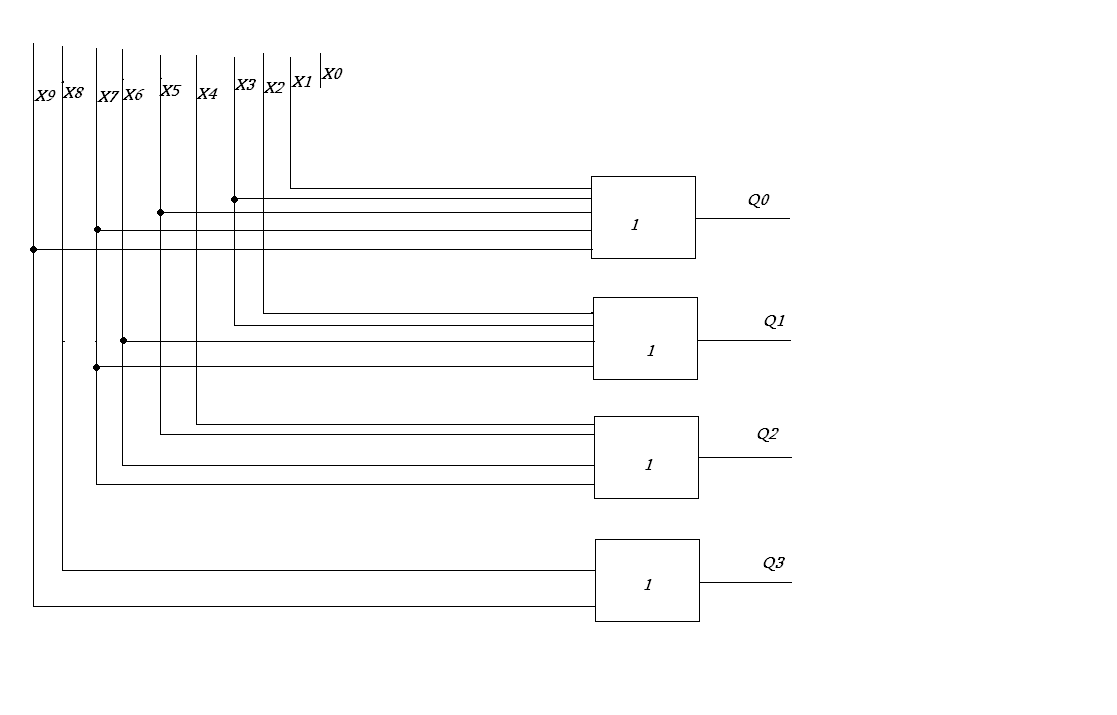

Шифратор. Таблица истинности. Мат. Описание. Принципиальная схема.

Шифраторы – преобр. кода из одного вида в другой. Примером является преобр. кода из десятичной системы счисления в двоичную. Кодам шифратора последовательно присваивается значение десятичных чисел. Поэтому подача логического сигнала на один из входов шифратора воспринимается им, как подача соответствующего десятичного числа. Поданный на вход сигнал на выходе преобразуется в двоичный код. По определению данный шифратор имеет <= 2n входов, где n – количество выходов.

Такого типа шифратор имеет ТИ:

|

23 |

22 |

21 |

20 |

||||||||||

№ |

Х9 |

Х8 |

Х7 |

Х6 |

Х5 |

Х4 |

Х3 |

Х2 |

Х1 |

Х0 |

Q3 |

Q2 |

Q1 |

Q0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

4 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

5 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

6 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

7 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

8 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

9 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

Используя ТИ, запишем функции Q3,Q2,Q1,Q0:

Q3=X8+X9

Q2=X4+X5+X6+X7

Q1=X2+X3+X6+X7

Q0=X1+X3+X5+X7+X9

Полученные функции позволяют создать лог. схему, реализующую преобразование десятичного кода в двоичный:

Анализ схемы показывает, что вход Х0 не используется для преобразования кода, поэтому схема воспринимает отсутствие сигналов на входах Х1-Х9 как 0. Основное применение такие схемы получили в вводе информации с клавиатуры.