- •1 .Параллельный регистр на rs-триггерах.

- •2. Параллельный регистр на d-триггерах.

- •3. Разрядная схема параллельного регистра, реализующая запись с двух направлений.

- •4. Сдвигающий регистр.

- •5. Организация межрегистровых связей

- •6. Основные параметры и классификация счетчиков

- •8. Вычитающий счетчик с последовательным переносом на т-триггерах

- •Реверсивный счетчик на т-триггерах.

- •10.Счетчик с параллельным переносом на т-триггерах.

- •11. Структура счетчика с комбинированным переносом.

- •12. Счетчик со сквозным переносом на т-триггерах.

- •13. Двоично-кодированные счетчики на т-триггерах.

- •14. Кольцевой счетчик на т-триггерах.

- •15.Мультиплексор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •16. Схема мультиплексорного дерева

- •17. Демультиплексор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •18.Схема демультиплексорного дерева

- •1 9. Преобразователи кодов.

- •Шифратор. Таблица истинности. Мат. Описание. Принципиальная схема.

- •22.Реализация демультиплексора с использованием дешифратора.

- •23 Реализация мультиплексора с использованием дешифратора.

- •Многоступенчатый дешифратор.

- •25. Полный двоичный дешифратор на базе двух двоично–десятичных де-шифраторов.

- •26. Цифровой компаратор. Таблица истинности. Математическое описание. Принципиальная схема

- •27. Счетчики в коде Грея

- •1. Счетчики в коде «1 из n»

- •3.Распределитель с автоматическим вхождением в рабочий цикл за 1 такт

- •4. Счетчик Джонсона.

- •5.Полиномиальные счетчики.

- •6. Схемы генераторов псевдослучайной последовательности (гпсп).

- •7. Арифметико-логические устройства (алу). Назначение и основные параметры.

- •8. Сумматоры. Алгоритм двоичного сложения.

- •9. Сумматоры. Сложение многоразрядных двоичных кодов.

- •11. Одноразрядный сумматор

- •12. Многоразрядный сумматор параллельного действия.

- •13. Многоразрядный сумматор последовательного действия.

- •14. Сумматор с параллельным переносом.

- •15.Сумматоры с цепным переносом.

- •16.Выполнение операций арифметического умножения.

- •17.Классификация запоминающих устройств.

- •18.Структура озу типа 2d.

- •19.Структура озу типа 3d.

- •20.Структура озу типа 2dm.

- •Запоминающие устройства типа

- •21.Масочные запоминающие устройства.

- •22.Матрица моп- транзисторных элементов зу.

- •23.Запоминающие устройства типа prom.

- •24/25.Запоминающие устройства типа eprom eeprom.

- •26.Статистические озу (sram).

- •27.Динамические озу(dram).

- •Запоминающие элементы

- •Основные сведения. Система параметров. Классификация

- •Параметры зу

- •Параметры зу

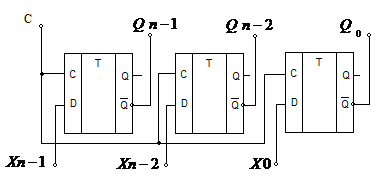

1 .Параллельный регистр на rs-триггерах.

Параллельный регистр предназначен для выполнения 1,3,4,6 микроопераций над кодовыми словами, т. е. парал. регистр обрабатывает информ. только в парал. форме, поэтому образование его ячейки не связано друг с другом.

Такой регистр содержит N триггеров ,входы которых объединены между собой.На его входы (Xn-1..Xo) подается информ. в прямом и обратном коде, а с выходов (Qn-1..Qo)

снимается инф. только в обратном коде. Следственно согласно классификации это однотактный регистр с парафазными входами и однофаз. инверсными выходами. Запись инф. в такой регистр происходит за 1 такт синхронизации. Если для записи в данный регистр используется только неинвер. или инвер. входы ,то запись информ. происходит за 2 такта. По первому такту необходимо сбросить или установить все триггеры в регистре в требуемое состояние(установка или сброс происходит подачей на вход соответ. последовательности).

2. Параллельный регистр на d-триггерах.

П аралл.

регистр – предназначен для вып. 1,3,4,6-ой

микроопераций над кодовыми словами,

т.е. паралл. регистр обрабатывает инф.

только в паралл. форме, поэтому образующие

его ячейки несвязанны непоср. друг с

другом.

аралл.

регистр – предназначен для вып. 1,3,4,6-ой

микроопераций над кодовыми словами,

т.е. паралл. регистр обрабатывает инф.

только в паралл. форме, поэтому образующие

его ячейки несвязанны непоср. друг с

другом.

Заменив в структурной схеме на RS-тригерах на D триггеры, мы получаем паралл. регистр с однофазными входами. Использ. такой структуры позволяет увеличить быстродейств. Регистра в два раза, т.к. D-тригер уст. на выходе значение, которое было на входе за 1 такт и при этом для его верной работы необходимо уст. нач. значения.

3. Разрядная схема параллельного регистра, реализующая запись с двух направлений.

Использую различные комбинационные схемы можно разработать разрядную ячейку (триггер в регистре), реализующую необходимый алгоритм работы параллельных триггеров, например схему обеспечивающую запись данный в регистр из 2х направлений. Например:

При С0 =1 и С1=0 в триггер будет записана. инфо с канала х, а при С0 =0 и С1=1 с канала y.

Используя такие схемы можно построить многотактные параллельные регистры.

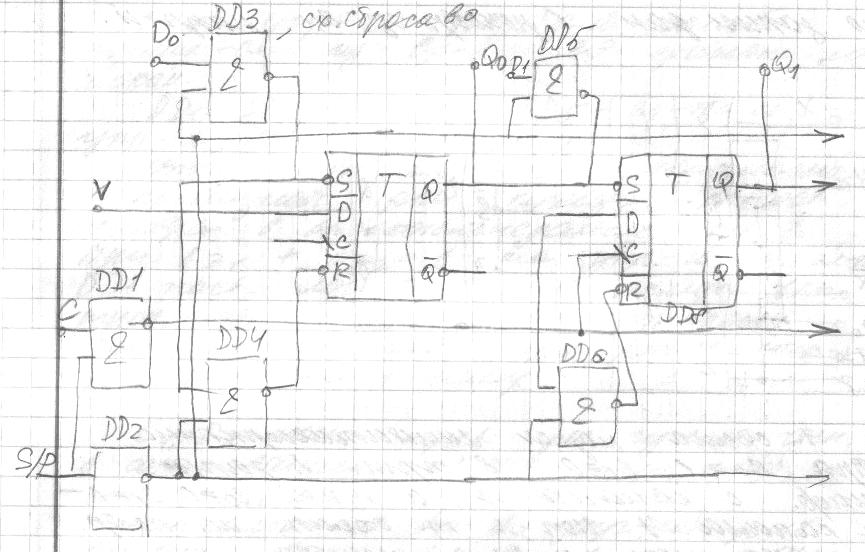

4. Сдвигающий регистр.

О днотактный

сдвигающий регистр с возможностью

параллельной записи

днотактный

сдвигающий регистр с возможностью

параллельной записи

Вход S/p – вход выбора режима работы регистра. Если сигнал на этом входе=0, элемент DD1 при любом значении тактового входа С блокирует переключение триггеров разрядных схем. Одновременно выходной сигнал инвертора DD2 преобразует элементы «2И-НЕ» DD3 и DD5 в инверторы и сигналы, присутствующие на входе D0 и D1, перезаписываются в разрядные схемы. Элементы DD4 и DD6 в таком режиме работают как инверторы и предотвращают подачу на асинхронные входы R и S двух активных уровней.

Е сли

вход S/p=1, - параллельная запись в триггер

невозможна, т.к. ЛЭ DD3, DD6, независимо от

входов параллельной записи D0 и D1 формируют

на асинхронных входах R, S активные

логические уровни. Одновременно с этим

DD1 поступает в инвертор и по фронту

импульса С вводит информацию в первую

разрядную схему со входа V.

сли

вход S/p=1, - параллельная запись в триггер

невозможна, т.к. ЛЭ DD3, DD6, независимо от

входов параллельной записи D0 и D1 формируют

на асинхронных входах R, S активные

логические уровни. Одновременно с этим

DD1 поступает в инвертор и по фронту

импульса С вводит информацию в первую

разрядную схему со входа V.

В регистр 2-й разрядной схемы перезаписывается информация с выхода перворазрядной и т. д. Регистр осуществляет последовательный прием данных и сдвиг полученной информации на такт влево.

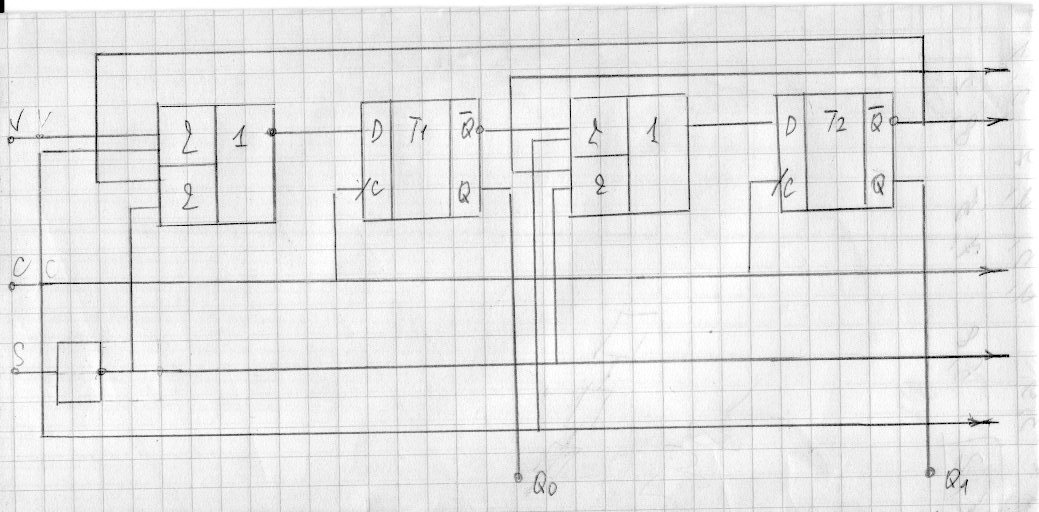

УГО регистра

Если регистр сдвигает информацию из старшего разряда, то на УГО стрелка направлена вправо и наоборот; если в обе стороны, - регистр равновесный (необходим дополнительный вход, т. е. дополнительный элемент «2И-ИЛИ»)

Фрагмент схемы реверсивного сдвигающего регистра

Э лементы

«2И-ИЛИ-НЕ» используют как мультиплексор,

изменяющий направление передачи сигнала.

При S=1 входы и выходы различных разделяющих

схем соединяются так, чтобы происходил

сдвиг информации влево, а при – впарво.

лементы

«2И-ИЛИ-НЕ» используют как мультиплексор,

изменяющий направление передачи сигнала.

При S=1 входы и выходы различных разделяющих

схем соединяются так, чтобы происходил

сдвиг информации влево, а при – впарво.

При этом в сдвигающих регистрах используются только двухтактные триггеры или триггеры с динамическим управлением. Это гарантирует сдвиг информации только на 1 разряд за 1 такт синхронизации