- •СОДЕРЖАНИЕ

- •ВВЕДЕНИЕ

- •НАЧАЛЬНЫЕ СВЕДЕНИЯ О ПЛИС

- •Интегральные схемы типа FPGA

- •Перестраиваемый логический блок

- •Генераторы логических функций

- •Триггер

- •Блоки ввода/вывода сигналов

- •Программируемые соединения

- •Динамические параметры конфигурируемого логического блока

- •ОРГАНЫ УПРАВЛЕНИЯ УНИВЕРСАЛЬНОГО ЛАБОРАТОРНОГО СТЕНДА

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •Список литературы

- •ВВЕДЕНИЕ

- •ПРОЕКТИРОВАНИЕ ОДНОВЫХОДНОЙ КОМБИНАЦИОННОЙ СХЕМЫ

- •СИНТЕЗ КОМБИНАЦИОННЫХ МНОГОВЫХОДНЫХ СХЕМ

- •Реализация булевых функций с помощью постоянного запоминающего устройства

- •ПРОЕКТИРОВАНИЕ КОМБИНАЦИОННЫХ СХЕМ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •СИНХРОННЫЕ ТРИГГЕРЫ СО СТАТИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •СИНХРОННЫЕ ДВУХСТУПЕНЧАТЫЕ ТРИГГЕРЫ

- •СИНХРОННЫЕ ТРИГГЕРЫ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •УСЛОВНОЕ ГРАФИЧЕСКОЕ ОБОЗНАЧЕНИЕ ТРИГГЕРНЫХ СХЕМ

- •ПРОЕКТИРОВАНИЕ ТРИГГЕРНЫХ СХЕМ

- •ПРОЕКТИРОВАНИЕ СИНХРОННЫХ ДВУХСТУПЕНЧАТЫХ ТРИГГЕРОВ

- •ПОСТРОЕНИЕ СИНХРОННЫХ ТРИГГЕРОВ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •ПРОЕКТИРОВАНИЕ ТРИГГЕРНЫХ СХЕМ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •СИНТЕЗ СИНХРОННЫХ СЧЕТЧИКОВ

- •Матрица переходов триггера

- •ПРИМЕР

- •ПРОЕКТИРОВАНИЕ СЧЕТЧИКОВ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •ПРОЕКТИРОВАНИЕ МНОГОФУНКЦИОНАЛЬНОГО РЕГИСТРА

- •ДИНАМИЧЕСКИЕ ПАРАМЕТРЫ РЕГИСТРОВ

- •ПРОЕКТИРОВАНИЕ РЕГИСТРА НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •Статические и динамические состязания сигналов

- •Функциональные и логические состязания сигналов

- •Синтез схем, свободных от логических состязаний

- •Анализ комбинационных схем с целью выявления состязаний

- •СОСТЯЗАНИЯ СИГНАЛОВ В ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМАХ

- •Последовательностные схемы

- •Условия надежного функционирования асинхронной схемы

- •Критические состязания

- •Существенные состязания

- •Анализ асинхронных последовательностных схем

- •Устранение критических состязаний

- •ЭКСПЕРИМЕНТАЛЬНОЕ ИССЛЕДОВАНИЕ СОСТЯЗАНИЙ СИГНАЛОВ

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •Логические элементы

- •Мультиплексоры

- •Описание цифрового осциллографа

- •Запуск и настройка осциллографа

- •Настройка изображения сигнала на экране осциллографа

- •Получение устойчивого изображения сигнала

- •Выбор цены деления по оси Х и Y

- •Выбор фронта сигнала по входу Х осциллографа

- •Измерение временных интервалов (измерение задержек)

Мультиплексоры

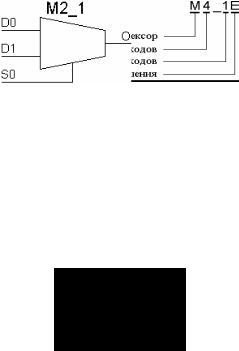

Пример соглашения для обозначения мультиплексоров в библиотеке элементов приведен на рис. П1.10.

Рис. П1.10. Обозначение мультиплексоров

Мультиплексор 2-1 (M2_1)

Мультиплексор выбирает один информационный вход из двух источников (D1 или D0) в зависимости от состояния управляющего входа S0. Выход (O) принимает состояние выбранного входа данных. При S0 = 0 на выходе появляется состояние входа D0, при

S0 = 1 — D1.

Условное графическое обозначение мультиплексора приведено на рис. П1.11, а его таблица истинности представлена табл. П1.2.

Рис. П1.11. Условное графическое обозначение мультиплексора M2_1

|

Таблица истинности мультиплексора M2_1 |

Таблица П1.2 |

|||||

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

Выход |

|

|

|

|

|

|

|

|

|

S0 |

|

D1 |

|

D0 |

|

O |

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

X |

|

1 |

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

X |

|

0 |

|

|

|

|

|

|

|

|

|

0 |

|

X |

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

0 |

|

X |

|

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

185 |

|

|

|

|

Мультиплексоры 2-1 с инверсными входами

(M2_1B1 и M2_1B2)

Условные графические обозначения мультиплексоров с инверсными входами приведено на рис. П1.12. Данные мультиплексоры отличаются от предыдущего наличием одного или двух инверсных входов, что отражено на их условном графическом обозначении

(см. рис. П1.13).

Рис. П1.12. Условное графическое обозначение мультиплексоров с инверсными входами

Мультиплексор 2-1 с входом разрешения (M2_1E)

Условное графическое обозначение мультиплексора M2_1Е приведено на рис. П1.13.

Вход Е разрешает работу мультиплексора. Когда разрешающий вход E = 1, то мультиплексор M2_1E выбирает один из информационных входов (D1 или D0) в зависимости от состояния управляющего входа S0. При Е = 0 состояние выхода равно 0.

Таблица истинности мультиплексора M2_1Е представлена табл. П1.3.

Рис. П1.13. Условное графическое обозначение мультиплексора M2_1Е

186

|

Таблица истинности мультиплексора M2_1Е |

Таблица П1.3 |

|||||

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

Выход |

|

|

|

|

|

|

|

|

|

|

E |

S0 |

|

D1 |

D0 |

|

O |

|

|

|

|

|

|

|

|

|

0 |

X |

|

X |

X |

|

0 |

|

|

|

|

|

|

|

|

|

1 |

0 |

|

X |

1 |

|

1 |

|

|

|

|

|

|

|

|

|

1 |

0 |

|

X |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

1 |

1 |

|

1 |

X |

|

1 |

|

|

|

|

|

|

|

|

|

1 |

1 |

|

0 |

X |

|

0 |

|

|

|

|

|

|

|

|

|

Мультиплексор 4-1 с входом разрешения (M4_1E)

Условное графическое обозначение мультиплексора M4_1Е приведено на рис. П1.14.

Рис. П1.14. Условное графическое обозначение мультиплексора M4_1Е

Вход Е разрешает работу мультиплексора. Когда разрешающий вход E = 1, то мультиплексор M4_1E выбирает один из четырех информационных входов (D3, D2, D1 или D0) в зависимости от состояния управляющих (адресных) входов S1 и S0. При Е = 0 состояние выхода равно 0.

Таблица истинности мультиплексора M4_1Е представлена табл. П1.4.

187

|

|

Таблица истинности мультиплексора M4_1Е |

Таблица П1.4 |

||||||

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

Выход |

|

|

|

|

|

|

|

|

|

|

|

E1 |

S1 |

|

S0 |

D0 |

D1 |

D2 |

D3 |

O |

|

|

|

|

|

|

|

|

|

|

|

0 |

X |

|

X |

X |

X |

X |

X |

0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

0 |

D0 |

X |

X |

X |

D0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

1 |

X |

D1 |

X |

X |

D1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

0 |

X |

X |

D2 |

X |

D2 |

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

1 |

X |

X |

X |

D3 |

D3 |

|

|

|

|

|

|

|

|

|

|

|

Триггеры

Основные сведения

В библиотеке элементов имеются три типа синхронных триггеров с динамическим управлением записью:

D-триггеры,

JK-триггеры, Т-триггеры.

JK-триггеры и Т-триггеры имеют прямой динамический синхронизирующий вход С. D-триггеры могут иметь как прямой так и инверсный синхронизирующий динамический вход С. Кроме того, указанные триггеры могут иметь вход разрешения для синхроим-

пульсов CE (clock enable).

Каждый из перечисленных типов триггеров может иметь асинхронный вход предварительной установки триггера или в 0 или в 1.

Также триггеры могут иметь синхронный вход предварительной установки триггера в 0 и/или в 1.

В системе XILINX FOUNDATION приняты следующие обозначения установочных входов на условном графическом обозначении триггера:

CLR (Clear), PRE (Preset) — асинхронные входы установки триггера в 0 и 1 соответственно;

188

R (Reset), S (Set) — синхронные входы установки триггера в 0 и 1 соответственно.

Обозначение триггеров

Наличие тех или входов у конкретного библиотечного триггера можно выяснить из его текстового обозначения. Пример соглашения для обозначения триггеров в библиотеке элементов приведен на рис. П1.15.

Рис. П1.15. Обозначение триггеров

Краткое описание триггеров

FDCE — D-триггер с входом разрешения синхросигнала и асинхронной установкой в 0

Условное графическое обозначения D-триггера FDCE приведено на рис. П1.16. а его таблица переходов представлена табл. П1.5.

189

Рис. П1.16. УсловноеграфическоеобозначениеD-триггераFDCE

|

Таблица переходов D-триггера FDCE |

Таблица П1.5 |

||||

|

|

|

||||

|

|

|

|

|

|

|

|

|

Входы |

|

Выход |

||

CLR |

CE |

|

D |

C |

Q |

|

1 |

X |

|

X |

X |

0 |

|

0 |

0 |

|

X |

X |

Q |

|

0 |

1 |

|

1 |

0/1 |

1 |

|

0 |

1 |

|

0 |

0/1 |

0 |

|

FDRE — D-триггер с входом разрешения синхросигнала и синхронной установкой в 0

Условное графическое обозначения D-триггера FDRE приведено на рис. П1.17, а его таблица переходов представлена табл. П1.6.

Рис.П1.17. УсловноеграфическоеобозначениеD-триггераFDRE

190

|

Таблица переходов D-триггера FDRE |

Таблица П1.6 |

|||

|

|

||||

|

|

|

|

|

|

|

|

Входы |

|

Выход |

|

R |

CE |

|

D |

C |

Q |

1 |

X |

|

X |

0/1 |

0 |

0 |

0 |

|

X |

X |

Q |

0 |

1 |

|

1 |

0/1 |

1 |

0 |

1 |

|

0 |

0/1 |

0 |

FJKCE — JK-триггер с входом разрешения синхросигнала и асинхронной установкой в 0

Условное графическое обозначения JK-триггера FJKCE приведено на рис. П1.18, а его таблица переходов представлена табл. П1.7.

Рис.П1.18.УсловноеграфическоеобозначениеJK-триггераFJKCE

|

Таблица переходов D-триггера FJKCE |

Таблица П1.7 |

|||||||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

Входы |

|

|

|

Выход |

|

||

CLR |

CE |

J |

|

K |

C |

|

Q |

|

|

1 |

X |

X |

|

X |

X |

0 |

|

|

|

0 |

0 |

X |

|

X |

X |

|

Q |

|

|

0 |

1 |

0 |

|

0 |

X |

|

Q |

|

|

0 |

1 |

0 |

|

1 |

0/1 |

0 |

|

|

|

0 |

1 |

1 |

|

0 |

0/1 |

1 |

|

|

|

0 |

1 |

1 |

|

1 |

0/1 |

|

|

|

|

|

Q |

|

|||||||

|

|

|

191 |

|

|

|

|

|

|

Приложение 2

ПОСТРОЕНИЕ ВРЕМЕННЫХ ДИАГРАММ РАБОТЫ ЦИФРОВЫХ СХЕМ

Построение временных диаграмм широко применяется при проектировании узлов и устройств ЭВМ. Это объясняется, прежде всего, большими возможностями, которые предоставляет временная диаграмма для анализа различного рода цифровых структур.

Процесс отображения последовательности переключения элементов цифровой схемы на временную ось будем называть по-

строением временной диаграммы.

Исходными данными для построения временной диаграммы являются:

логическая структура схемы, описание (модель) элементов схемы, начальное состояние схемы,

временная диаграмма входных воздействий.

Логическую структуру цифровой схемы обычно задают с помощью графического изображения, на котором показывают элементы и связи между ними. Перед построением временной диаграммы необходимо обозначить все входящие в схему элементы и все входные контакты.

Основу описания элемента составляет логическая функция, которую он реализует. Это математическая модель реального логического элемента, использующая аппарат булевой алгебры. Эту модель необходимо дополнить динамическими параметрами, взятыми из паспортных данных элемента. Такую модель элемента называют динамической.

При построении временных диаграмм приходится учитывать динамическую помехоустойчивость элемента, т.е. его способность не реагировать на высокочастотные изменения входного состояния. Данное свойство элемента описывается его динамической передаточной характеристикой (рис. П2.1).

192

Динамическая помехоустойчивость элемента достаточно точно учитывается с помощью следующего допущения (см. рис. П2.1):

Длительность выходного импульса динамической модели элемента не может быть меньше задержки переключения элемента по последнему входному воздействию.

Построение временной диаграммы работы схемы выполняют на листе клетчатой бумаги. Предварительно его следует разметить:

нанести ось времени с выбранной единицей измерения, слева записать обозначения внешних входов и элементов

схемы, задать временную последовательность сигналов на внешних

входах, а напротив обозначения элементов — их начальное состояние.

Рис. П2.1. Динамическая передаточная характеристика логического элемента, где: = t2_− t1 — интервал между изменениями сигналов на входах элемента, tи —- длительность импульса на выходе элемента

При изложении алгоритма подготовленный таким образом лист будем называть временной диаграммой. Он будет заполняться в процессе реализации алгоритма построения временной диаграммы.

193

Переключение любого сигнала в схеме из одного состояния в другое будем называть событием.

Момент времени, для которого определяется состояние схемы, будем называть текущим. Перед построением временной диаграммы это время соответствуют начальному состоянию схемы и равно нулю (tт = 0).

АЛГОРИТМ ПОСТРОЕНИЯ ВРЕМЕННОЙ ДИАГРАММЫ

1.Найти на временной диаграмме как входных, так и выходных сигналов элементов схемы ближайшее(-ие) к текущему моменту времени запланированное(-ые) событие(-я) (в схеме могут одновременно изменить свое состояние несколько сигналов).

2.Считать время наступления найденного(ых) события(ий) текущим.

3.Продолжить на временной диаграмме состояние выхода каждого элемента до текущего момента времени.

4.Образовать список текущих событий из элементов (внешних входов), чьи выходные состояния изменились в текущий момент времени.

5.Выполнить для каждого элемента из списка текущих событий следующие действия:

a)сформировать список из элементов, присоединенных к выходу рассматриваемого элемента;

b)вычислить для каждого элемента из этого списка значение его выхода. Если вычисленное значение не равно текущему, то отметить на временной диаграмме будущее переключение элемента. В противном случае ничего не делать. Время будущего переключения элемента определяется прибавлением соответствующей задержки к текущему моменту времени (tб = tт + tз).

6.Проверить временную диаграмму. Если будущих переключений нет, то построение временной диаграммы закончено. В противном случае перейти к п.1.

194

Пример

Рассмотрим процесс построения временной диаграммы для триггерной схемы, изображенной на рис. П2.2.

Рис. П2.2. Логическая схема JK-триггера

Элементы, используемые в схеме триггера, имеют следующие задержки: ЛА4 (3ИНЕ) — tз01 = 22 нс, t10з = 15 нс; ЛК3 (2-2И-

2ИЛИ/2-2И-2ИЛИ-НЕ) — t з01 = t10з = 15 нс.

Положим следующее начальное состояние внешних входов и элементов схемы: J = K = C = 1, D1 = 0, D2 = 1, D3 = 0, D4 = 1.

Будем считать, что входы J и K не изменяют своего состояния, а вход С переключается из 1 в 0 в момент времени t = 10 нс.

На рис. П2.3 показана временная диаграмма с этими исходными данными. Каждое деление на оси времени равно 5 нс.

1.Найдем на временной диаграмме событие, ближайшее к текущему моменту времен. Это переключение сигнала на входе С

(см. рис. П2.3).

2.Текущее время теперь равно 10 нс (см. рис. П2.3).

3.Продолжим состояние выходов элементов схемы до текущего момента времени (см. рис. П2.3).

195

4. Образуем список текущих переключений. Он будет состоять из одного переключения на входе С.

|

|

Рис. П2.3. Реализация события |

Рис. П2.4. Реализация события |

на входе С |

на выходе элемента D3 |

5. Из рис П2.2 следует, что событие С поступает на входы элементов D1 — D4.

Вычислим значения выходов данных элементов в текущий момент времени: D1 = 1, D2 = 1, D3 = 1, D4 = 1. Таким образом, элементы D1 и D3 изменяют свое состояние:

элемент D1 в момент времени t = tт +tз01 = 10 + 22 = 32 нс; элемент D3 в момент времени t = tт +t10з = 10 + 15 = 25 нс.

На рис П2.3 эти будущие переключения (события) отмечены пунктиром.

6.Так как на временной диаграмме имеются запланированные

вбудущем переключения сигналов, то переходим к выполнению п.1 алгоритма.

Очередным переключением на временной диаграмме (см. рис. П2.3) является событие на выходе элемента D3 в момент времени t = 25 нс. Выполняя последовательно пп. 2-6 алгоритма, выясним, какое влияние окажет данное событие на появление будущих переключений. Реализация данных пунктов алгоритма приведена на рис. П2.4. Результатом является запланированное событие на выходе элемента D4 в момент времени tб = 40 нс.

196

Очередным текущим событием является изменение сигнала на выходе элемента D1 (рис. П2.5). Его реализация приведет к планированию будущего переключения сигнала на выходе элемента D3 в момент времени tб = 47 нс (см. рис. П2.5).

|

|

Рис. П2.5. Реализация события |

Рис. П2.6. Реализация события |

на выходе элемента D1 |

на выходе элемента D4 |

Следующим текущим событием является изменение сигнала на выходе элемента D4 (рис. П2.6). Его реализация приведет к повторному будущему переключению сигнала на выходе элемента D3 в момент времени tб = 55 нс (см. рис. П2.6). Это приведет к появлению на выходе элемента D3 сигнала, длительность которого (55 - 47 = 8 нс) меньше величины задержки элемента (15 нс). В силу динамической помехоустойчивости элемента сигнал такой длительности не может появиться на выходе элемента. Следовательно, для отражения реальных свойств элемента необходимо эти будущие события отменить (см. рис. П2.6).

После реализации события на выходе элемента D4 в будущем отсутствуют какие-либо переключения сигналов (см. рис. П2.6). Поэтому построение временной диаграммы завершено.

197

Приложение 3

КРАТКОЕ РУКОВОДСТВО ПО РАБОТЕ С ЦИФРОВЫМ ОСЦИЛЛОГРАФОМ

После отработки схемы при помощи моделирования переходят к ее экспериментальному исследованию на универсальном лабораторном стенде сперва в статическом, а затем и в динамическом режиме.

Во втором случае на входы схемы подаются тестовые воздействия, следующие с близкой к реальной частотой повторения, а для наглядного представления хода событий в исследуемой схеме используется осциллограф. При визуальном отображении выходных сигналов схемы на экране осциллографа можно проанализировать не только логику функционирования, но и измерить амплитудные и временные характеристики сигналов. В частности, могут быть измерены и оценены такие важные динамические параметры, как времена задержек переключения и сдвигов сигналов относительно друг друга и ряд других.

Использование осциллографа дает наибольший эффект при наблюдении повторяющихся или периодических сигналов. В этом случае на экране осциллографа можно наблюдать неподвижную устойчивую картинку, характеризующую поведение сигнала в течение выбранного периода. Поэтому для обеспечения такого удобного режима наблюдения при исследовании схемы в динамическом режиме необходимо перевести ее в режим циклического повторения одной и той же последовательности переходов из одного состояния в другое.

198