- •СОДЕРЖАНИЕ

- •ВВЕДЕНИЕ

- •НАЧАЛЬНЫЕ СВЕДЕНИЯ О ПЛИС

- •Интегральные схемы типа FPGA

- •Перестраиваемый логический блок

- •Генераторы логических функций

- •Триггер

- •Блоки ввода/вывода сигналов

- •Программируемые соединения

- •Динамические параметры конфигурируемого логического блока

- •ОРГАНЫ УПРАВЛЕНИЯ УНИВЕРСАЛЬНОГО ЛАБОРАТОРНОГО СТЕНДА

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •Список литературы

- •ВВЕДЕНИЕ

- •ПРОЕКТИРОВАНИЕ ОДНОВЫХОДНОЙ КОМБИНАЦИОННОЙ СХЕМЫ

- •СИНТЕЗ КОМБИНАЦИОННЫХ МНОГОВЫХОДНЫХ СХЕМ

- •Реализация булевых функций с помощью постоянного запоминающего устройства

- •ПРОЕКТИРОВАНИЕ КОМБИНАЦИОННЫХ СХЕМ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •СИНХРОННЫЕ ТРИГГЕРЫ СО СТАТИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •СИНХРОННЫЕ ДВУХСТУПЕНЧАТЫЕ ТРИГГЕРЫ

- •СИНХРОННЫЕ ТРИГГЕРЫ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •УСЛОВНОЕ ГРАФИЧЕСКОЕ ОБОЗНАЧЕНИЕ ТРИГГЕРНЫХ СХЕМ

- •ПРОЕКТИРОВАНИЕ ТРИГГЕРНЫХ СХЕМ

- •ПРОЕКТИРОВАНИЕ СИНХРОННЫХ ДВУХСТУПЕНЧАТЫХ ТРИГГЕРОВ

- •ПОСТРОЕНИЕ СИНХРОННЫХ ТРИГГЕРОВ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •ПРОЕКТИРОВАНИЕ ТРИГГЕРНЫХ СХЕМ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •СИНТЕЗ СИНХРОННЫХ СЧЕТЧИКОВ

- •Матрица переходов триггера

- •ПРИМЕР

- •ПРОЕКТИРОВАНИЕ СЧЕТЧИКОВ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •ПРОЕКТИРОВАНИЕ МНОГОФУНКЦИОНАЛЬНОГО РЕГИСТРА

- •ДИНАМИЧЕСКИЕ ПАРАМЕТРЫ РЕГИСТРОВ

- •ПРОЕКТИРОВАНИЕ РЕГИСТРА НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •Статические и динамические состязания сигналов

- •Функциональные и логические состязания сигналов

- •Синтез схем, свободных от логических состязаний

- •Анализ комбинационных схем с целью выявления состязаний

- •СОСТЯЗАНИЯ СИГНАЛОВ В ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМАХ

- •Последовательностные схемы

- •Условия надежного функционирования асинхронной схемы

- •Критические состязания

- •Существенные состязания

- •Анализ асинхронных последовательностных схем

- •Устранение критических состязаний

- •ЭКСПЕРИМЕНТАЛЬНОЕ ИССЛЕДОВАНИЕ СОСТЯЗАНИЙ СИГНАЛОВ

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •Логические элементы

- •Мультиплексоры

- •Описание цифрового осциллографа

- •Запуск и настройка осциллографа

- •Настройка изображения сигнала на экране осциллографа

- •Получение устойчивого изображения сигнала

- •Выбор цены деления по оси Х и Y

- •Выбор фронта сигнала по входу Х осциллографа

- •Измерение временных интервалов (измерение задержек)

синхронные двухступенчатые триггеры, синхронные триггеры с динамическим управлением записью.

СИНХРОННЫЕ ТРИГГЕРЫ СО СТАТИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

Входная информация в рассматриваемых триггерах принимается только тогда, когда значение СИ соответствует единице, т.е. в течение всей длительности СИ. Это означает, что при С = 1 переключение сигналов на логических входах вызывает изменение состояния триггера, т.е. выхода Q. Поэтому информацию на логических входах триггера, как правило, меняют при С = 0.

RS-триггер

Синхронный RS-триггер со статическим управлением записью реализуется подключением двух элементов И-НЕ к ЗЯ (рис. 3.3). Смена сигналов на логических входах R и S разрешена между СИ. Временная диаграмма работы этого триггера приведена на рис. 3.4.

Рис. 3.3. Синхронный RS-триггер со статическим управлением записью, его условное графическое обозначение и таблица переходов

57

Рис.3.4. Временная диаграмма работы синхронного RS-триггера со статическим управлением записью

Схема синхронного RS-триггера с дополнительными инверсными асинхронными входами Ra и Sa (входами предварительной

установки триггера в 0 или 1) на элементах 2-2И-2ИЛИ-НЕ показана на рис. 3.5.

Рис. 3.5. Синхронный RS-триггер со статическим управлением записью

и асинхронными входами R a и S a и его условное графическое обозначение

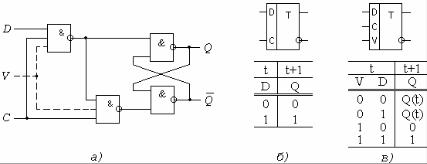

D-триггер

На практике наибольшее распространение получила схема синхронного D-триггера со статическим управлением записью. D- триггер имеет один логический вход D (Delay — задержка), со-

58

стояние которого с каждым СИ передается на выход, т.е. выходные сигналы представляют собой задержанные входные сигналы. Схему D-триггера можно получить из RS-триггера, если на вход R подать инвертированный сигнал входа S. Однако целесообразно использовать для инвертирования уже имеющиеся элементы

(рис. 3.6).

Рис. 3.6. Синхронный D-триггер со статическим управлением записью

(пунктиром показан вход V для DV-триггера):

а) логическая схема; б) условное графическое обозначение D-триггера и его таблица переходов; в) условное графическое обозначение DV-триггера и его таблица переходов

DV-триггер

Если к D-триггеру добавить еще один вход V (Vorentscheidung — предварительное разрешение) для блокирования СИ (пунктирная линия на рис. 3.6), то получим синхронный DVтриггер со статическим управлением записью. Легко заметить, что входы С и V можно поменять местами без нарушения логики работы триггера.

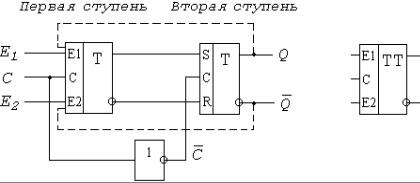

СИНХРОННЫЕ ДВУХСТУПЕНЧАТЫЕ ТРИГГЕРЫ

Синхронный двухступенчатый триггер — это триггерная схема, состоящая из двух частей, т.е. двух последовательно соединенных триггеров со статическим управлением записью, одновременный прием информации в которые запрещен. Это достигается включе-

59

нием инвертора в цепь синхронизирующих импульсов для второй ступени (рис. 3.7).

Рис. 3.7. Структура синхронного двухступенчатого триггера и его условное графическое обозначение

Логика работы синхронного двухступенчатого триггера следующая:

при С = 0 прием входной информации в первую ступень триггера закрыт. А поскольку на синхронизирующий вход второй ступени благодаря инвертору поступает сигнал 1, то прием информации во вторую ступень открыт (см. рис. 3.7). Вторая ступень принимает (копирует) информацию, хранимую в первой ступени триггера.

Следовательно, при С = 0 состояние обеих ступеней двухступенчатого триггера одинаково; в этом состоянии можно менять сигналы на логических входах без изменения состояния двухступенчатого триггера;

при С = 1 картина меняется: первая ступень открыта, а вторая, благодаря инвертору, закрыта по синхронизирующему входу (см. рис. 3.7). Информация, находящаяся на логических входах двухступенчатого триггера, принимается в первую ступень, а вторая ступень остается в покое.

Таким образом, при изменении 0/1 синхросигнала входная информация принимается в первую ступень, а при изменении 1/0 синхросигнала новое состояние первой ступени передается во вто-

60

рую ступень, т.е. появляется на выходе Q двухступенчатого триггера.

RS-триггер

Синхронный двухступенчатый RS-триггер представляет собой схему, состоящую из двух синхронных RS-триггеров со статическим управлением записью (рис. 3.8).

Рис. 3.8. Синхронный двухступенчатый RS-триггер (пунктиром показана обратная связь для JK-триггера)

Временная диаграмма, иллюстрирующая логику работы данного триггера, приведена на рис. 3.9. Из рассмотрения временной диаграммы видно, что сигнал на выходе триггера изменяется после окончания синхроимпульса. Это справедливо для любого синхронного двухступенчатого триггера.

61

Рис. 3.9. Временная диаграмма работы синхронного двухступенчатого RS-триггера

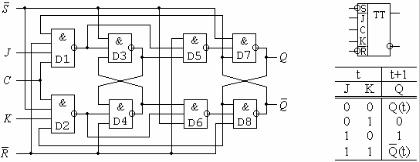

JK-триггер

На практике широкое распространение получил синхронный двухступенчатый JK-триггер. Данный триггер имеет два входа J и К. Если J = K = 1, то триггер с приходом синхроимпульса изменяет свое состояние на противоположное. При остальных значениях входов J и К триггер повторяет таблицу переходов RS-триггера.

Синхронный двухступенчатый RS-триггер, который имеет несколько S и R входов, объединенных функцией конъюнкции, легко преобразуется в синхронный JK-триггер. Для этого необходимо завести обратную связь с выходов триггера на его входы как показано на рис. 3.8.

Другой пример JK-триггера показан на рис. 3.10. Здесь элементы D5 и D6, отделяющие вторую ступень от первой, управляются не отдельным инвертором, а схемой управления первой ступени (элементы D1 и D2).

62

Рис. 3.10. Синхронный двухступенчатый JK-триггер с асинхронными входами R и S , его условное графическое обозначение и таблица переходов

Если С = 0, то элементы D1 и D2 закрыты и изменения сигналов на входах J и К не влияют на состояние триггера.

Передний фронт синхроимпульса (фронт 0/1) переключает в «0» элемент D1 или элемент D2 в зависимости от входных сигналов и состояния триггера второй ступени. Этот нулевой сигнал вначале отсоединяет вторую ступень от первой, а затем устанавливает ЗЯ первой ступени в требуемое состояние.

Задний фронт синхроимпульса (фронт 1/0) сначала отделяет первую ступень от входной информации, а затем открывает элементы D5 и D6, разрешая ЗЯ второй ступени скопировать состояние первой ступени.

Более детально логику работы данного триггера иллюстрирует временная диаграмма, приведенная на рис. 3.11.

Асинхронные входы двухступенчатого триггера

Обычно все синхронные триггеры со сложной внутренней организацией (двухступенчатые и с динамическим управлением записью) имеют асинхронные входы предварительной установки триггера в состояние 0 или 1 (см. рис. 3.10).

Сигналы, поступающие на данные входы, пользуются приоритетом, т.е. независимо от состояния других входов триггера эти сигналы сразу (по переднему фронту) устанавливают триггер в определенное состояние. Буквой S обозначают асинхронный вход для установки триггера в состояние 1, а буквой R — асинхронный вход

63

для установки триггера в состояние 0. Синхронный триггер по установочным входам реализует таблицу переходов асинхронного RS-триггера (см. рис. 3.2).

Наличие у синхронного триггера асинхронных входов указывают в его обозначении следующим образом: после сокращенного обозначения логических входов пишут обозначение асинхронных входов, например: -триггер.

Рис. 3.11. Временная диаграмма работы синхронного двухступенчатого JK R S -триггера

Динамические параметры синхронных двухступенчатых триггеров

Основными динамическими параметрами триггерных схем являются:

задержки переключения по различным входам, время предварительной установки логических сигналов, время удержания логических сигналов.

Проведем оценку динамических параметров двухступенчатых триггеров на примере JK-триггера (см. рис. 3.10 и рис. 3.11).

64

Задержки переключения

Задержки переключения триггера по синхронизирующему входу С из 0 в 1 и из 1 в 0 определяются задержками последовательно переключаемых логических элементов при изменении синхроимпульса из 1 в 0 (см. рис. 3.11). В силу симметричности структуры триггера задержки переключения для прямого и инверсного выходов триггера одинаковы. Положим, что все логические элементы

имеют одинаковые задержки tз01 ,tз10 . Задержки переключения триггера по синхронизирующему входу С равны:

|

01 |

|

01 |

|

|

|

01 |

|

10 |

|

|

|

t |

з.CQ |

= t |

|

|

|

= 2t |

з |

+tз |

|

; |

|

|

з.CQ |

|

|

|

|||||||||

|

10 |

|

10 |

|

|

|

|

01 |

|

10 |

|

|

|

tз.CQ |

= tз.CQ |

= 2(t |

з |

+t |

з |

). |

|||||

Как следует из |

схемы |

триггера |

и |

временной диаграммы |

||||||||

(см. рис. 3.10 и 3.11) задержки переключения по установочным входам равны:

t |

01 |

=t |

01 |

; |

|

|

t |

10 |

|

|

|

=t |

01 |

+t |

10 |

; |

||

з.SQ |

з |

|

|

з.SQ |

|

з |

з |

|||||||||||

|

10 |

|

|

01 |

|

10 |

|

t |

01 |

|

|

|

=t |

01 |

|

|

|

|

t |

з.RQ |

=tз |

|

+t |

з |

; |

|

|

|

з . |

|

|

||||||

|

з.RQ |

|

|

|

||||||||||||||

Время предварительной установки

Время предварительной установки (tуст) для триггерных схем — это интервал времени, в течение которого сигнал, поданный на логический вход, должен оставаться неизменным до активного изменения сигнала на входе С триггера.

Активным называют такое изменение синхроимпульса, которое вызывает переключение выходного сигнала. Для синхронного двухступенчатого триггера — это изменение 1/0 синхроимпульса. Таким образом, поступление новой информации на логические входы триггера должно опережать активный фронт синхроимпуль-

са как минимум на время tуст.

Время предварительной установки логических сигналов для синхронных двухступенчатых триггеров должно быть больше или

65