- •СОДЕРЖАНИЕ

- •ВВЕДЕНИЕ

- •НАЧАЛЬНЫЕ СВЕДЕНИЯ О ПЛИС

- •Интегральные схемы типа FPGA

- •Перестраиваемый логический блок

- •Генераторы логических функций

- •Триггер

- •Блоки ввода/вывода сигналов

- •Программируемые соединения

- •Динамические параметры конфигурируемого логического блока

- •ОРГАНЫ УПРАВЛЕНИЯ УНИВЕРСАЛЬНОГО ЛАБОРАТОРНОГО СТЕНДА

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •Список литературы

- •ВВЕДЕНИЕ

- •ПРОЕКТИРОВАНИЕ ОДНОВЫХОДНОЙ КОМБИНАЦИОННОЙ СХЕМЫ

- •СИНТЕЗ КОМБИНАЦИОННЫХ МНОГОВЫХОДНЫХ СХЕМ

- •Реализация булевых функций с помощью постоянного запоминающего устройства

- •ПРОЕКТИРОВАНИЕ КОМБИНАЦИОННЫХ СХЕМ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •СИНХРОННЫЕ ТРИГГЕРЫ СО СТАТИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •СИНХРОННЫЕ ДВУХСТУПЕНЧАТЫЕ ТРИГГЕРЫ

- •СИНХРОННЫЕ ТРИГГЕРЫ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •УСЛОВНОЕ ГРАФИЧЕСКОЕ ОБОЗНАЧЕНИЕ ТРИГГЕРНЫХ СХЕМ

- •ПРОЕКТИРОВАНИЕ ТРИГГЕРНЫХ СХЕМ

- •ПРОЕКТИРОВАНИЕ СИНХРОННЫХ ДВУХСТУПЕНЧАТЫХ ТРИГГЕРОВ

- •ПОСТРОЕНИЕ СИНХРОННЫХ ТРИГГЕРОВ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •ПРОЕКТИРОВАНИЕ ТРИГГЕРНЫХ СХЕМ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •СИНТЕЗ СИНХРОННЫХ СЧЕТЧИКОВ

- •Матрица переходов триггера

- •ПРИМЕР

- •ПРОЕКТИРОВАНИЕ СЧЕТЧИКОВ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •ПРОЕКТИРОВАНИЕ МНОГОФУНКЦИОНАЛЬНОГО РЕГИСТРА

- •ДИНАМИЧЕСКИЕ ПАРАМЕТРЫ РЕГИСТРОВ

- •ПРОЕКТИРОВАНИЕ РЕГИСТРА НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •Статические и динамические состязания сигналов

- •Функциональные и логические состязания сигналов

- •Синтез схем, свободных от логических состязаний

- •Анализ комбинационных схем с целью выявления состязаний

- •СОСТЯЗАНИЯ СИГНАЛОВ В ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМАХ

- •Последовательностные схемы

- •Условия надежного функционирования асинхронной схемы

- •Критические состязания

- •Существенные состязания

- •Анализ асинхронных последовательностных схем

- •Устранение критических состязаний

- •ЭКСПЕРИМЕНТАЛЬНОЕ ИССЛЕДОВАНИЕ СОСТЯЗАНИЙ СИГНАЛОВ

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •Логические элементы

- •Мультиплексоры

- •Описание цифрового осциллографа

- •Запуск и настройка осциллографа

- •Настройка изображения сигнала на экране осциллографа

- •Получение устойчивого изображения сигнала

- •Выбор цены деления по оси Х и Y

- •Выбор фронта сигнала по входу Х осциллографа

- •Измерение временных интервалов (измерение задержек)

ние триггера, а запоминающая ячейка второй ступени копирует состояние триггера первой ступени, поскольку открыты элементы связи, разделяющие оба триггера. Если теперь специальным (установочным) сигналом изменить состояние запоминающей ячейки первой ступени, то, очевидно, изменит свое состояние и триггер второй ступени (скопирует новое состояние триггера первой ступени). Время, через которое на выходах двухступенчатого триггера установится новое состояние, будет определяться задержкой, вносимой четырьмя последовательно включенными логическими элементами. Для увеличения быстродействия сигнал предварительной установки подается одновременно на запоминающие ячейки первой и второй ступени триггера (см. рис. 3.10 и 3.24). При этом новое состояние триггера установится через время, равное времени задержки двух элементов.

При С = 1 состояние логических входов непосредственно воздействует на состояние ЗЯ первой ступени двухступенчатого триггера. Поэтому при подаче установочного сигнала на входах данной ЗЯ может появиться запрещенная комбинация сигналов. Чтобы исключить появление запрещенной комбинации на входах ЗЯ, установочные сигналы подают и на схему управления первой ступени (см. рис. 3.10 и 3.24).

ПОСТРОЕНИЕ СИНХРОННЫХ ТРИГГЕРОВ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

Схемы триггеров с динамическим управлением записью отличаются большим разнообразием, поэтому для них затруднительно использовать изложенный выше подход проектирования.

Во второй части варианта домашнего задания необходимо построить по уравнениям (3.1) логическую структуру триггера с динамическим управлением записью. Эти уравнения получены при реализации метода синтеза триггерных схем на ЭВМ [2]. Если по приведенным уравнениям построить комбинационную схему на заданной системе элементов, а затем соединить одноименные полюса (вход-выход) схемы, т.е. образовать обратные связи (см. рис. 3.21), то получим структуру синтезированного триггера.

82

Рассмотрим подробнее вторую часть варианта домашнего задания на следующем примере. Задана система уравнений, описывающая логическую структуру триггера:

Y1 = S C y2 E 2 y3R E1 y1 y3R, Y 2 = R C y1 E1 y3S E2 y2 y3S , Y 3 =Q = S y2 y1 y3R.

Переменные y1, y2, y3 обозначают внутренние переменные триггера, S и R — асинхронные входы установки триггера в 1 и 0, а Q — прямой выход триггера. Во всех вариантах домашнего задания функция выхода Q равна внутренней переменной Y3. Поэтому после замыкания обратных связей выход комбинационной схемы Y3 будет являться прямым выходом Q триггера.

Прежде чем построить логическую структуру триггера по приведенным уравнениям, перейдем от минимальной дизъюнктивной нормальной формы, в которой заданы эти уравнения, к их представлению в базисе Шеффера:

Y1 = S C y2 E 2 R y3 E1 R y1 y3 = = S C y2 (E 2 R y3) (E1 R y1 y3);

Y 2 = R C y1 E1 S y3 E2 S y2 y3 = = R C y1 (E1 S y3) (E2 S y2 y3);

Q =Y 3 = S y2 R y1 y3 = S y2 (R y1 y3).

Логическая структура триггера на базовых элементах ПЛИС XC10PC84, реализованная по этим уравнениям, приведена на рис. 3.25.

83

Рис. 3.25. Реализация триггера с динамическим управлением записью

Заметим, что в приведенных примерах задана таблица переходов JK-триггера. Таким образом, нами получены две структуры JKтриггера (см. рис. 3.24 и 3.25), у которых E1 = J и E2 = K.

ПРОЕКТИРОВАНИЕ ТРИГГЕРНЫХ СХЕМ НА VHDL

В вариантах домашнего задания необходимо спроектировать на VHDL синхронный триггер с динамическим управлением записью по фронту 0/1 или 1/0 с входом предварительной (асинхронной или синхронной) установки триггера или в 0, или в 1. Последнее условие обусловлено тем, что библиотечные компоненты ПЛИС, в которые синтезатор выполняет отображение VHDL-описание схемы,

84

не используют асинхронный сброс и установку триггера, а используют только или сброс, или установку.

Средства VHDL, используемые для описания поведения триггера, зависят от того, как разработчик представляет алгоритм его функционирования.

Если в распоряжении разработчика имеется система уравнений, по которой построена структура триггера (см. раздел «Построение синхронных триггеров с динамическим управлением записью»), то его описание на языке VHDL может быть выполнено с использованием логических операторов и сигнального оператора присваивания (листинг 3.1).

Листинг 3.1. Описание триггера по уравнениям

entity trigger_0 is port (

S,R,C,E1,E2: in BIT; Q: out BIT

);

end trigger_0;

architecture trigger_0_arch of trigger_0 is signal Y1: BIT;

signal Y2: BIT; signal Y3: BIT;

begin

Y1 <= S or not c or not Y2 or (not E2 and not R and Y3) or (E1 and not R and Y1 and not Y3);

Y2 <= R or not c or not Y1 or (not E1 and not S and not

Y3)

or (E2 and not S and Y2 and

Y3);

Y3 <= S or not Y2 or (not R and Y1 and Y3); Q <= Y3;

end trigger_0_arch;

Данное описание требует наличия системы уравнений, описывающих структуру триггера, получение которых сопряжено с выполнением достаточно сложных процедур. Но закон функционирования триггера можно задать в более простой алгоритмической форме.

85

Рассмотрим вариант описания алгоритма функционирования триггера, используя его характеристическое уравнения. Характеристическое уравнение получают по таблице переходов триггера. Для этого перейдем от компактной записи таблицы переходов к её развернутой форме (рис. 3.26).

Е1(t) |

|

E2(t) |

Q(t+1) |

|

Е1(t) |

E2(t) |

Q(t) |

Q(t+1) |

||

0 |

|

0 |

Q(t) |

|

0 |

0 |

0 |

0 |

||

0 |

1 |

0 |

B |

0 |

0 |

1 |

1 |

|||

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

|||

1 |

1 |

|

|

(t) |

|

0 |

1 |

1 |

0 |

|

Q |

|

|||||||||

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

Рис. 3.26. Две формы таблицы переходов триггера

Затем выполним запись функции по 1 с последующим её упрощением. В результате получим следующее характеристическое уравнение триггера:

Qt+1 = (E1 & Q E2 & Q)t .

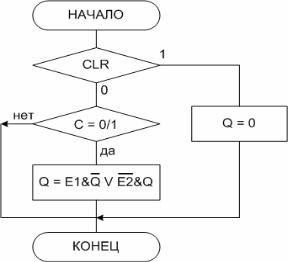

Алгоритм функционирования триггера с использованием характеристического уравнения можно представить, как показано на рис. 3.27.

Примечание. В данном алгоритме CLR обозначает асинхронный вход установки триггера в «0». При выполнении задания целесообразно придерживаться следующих обозначений для установочных входов, принятых в системе XILINX FOUNDATION: CLR, PRE – асинхронные входы установки триггера в 0 и 1 соответственно, R, S – синхронные входы установки триггера в 0 и 1 соответственно.

86

Рис. 3.27. Алгоритм функционирования триггера с использованием характеристического уравнения

Как видим, для того, чтобы описать данный алгоритм функционирования триггера на VHDL, необходимо средство описания изменения сигнала на входе С. Таким средством в языке VHDL является один из предопределенных атрибутов сигнала — признак event (event attribute). Атрибуты сигналов используют для получения информации о событиях, которые происходят с сигналами. Обращение к атрибутам имеет следующий синтаксис:

signal_name'attribute_name

Если ”C” — имя синхросигнала, то конструкция "C'event" на любом элементарном шаге по времени выдает значение true, когда сигнал C изменяет свое значение, и false — в противном случае.

В листинге 3.2 приведено описание закона функционирования триггера с использованием атрибута event. Заметим, что величина "C'event" истинна при любом изменении сигнала C, поэтому для анализа фронта 0/1 сигнала C предусмотрена проверка

C = ‘1’.

87

Листинг 3.2. Описание триггера с использованием характеристического уравнения

entity trigger_2 is port (

CLR,C,E1,E2: in BIT; Q: buffer BIT

);

end trigger_2;

architecture trigger_2_arch of trigger_2 is begin

process (CLR, C) begin

if CLR='1' then Q <= '0' ; elsif C'event and C='1' then

Q <= (E1 and not Q) or (not E2 and Q); end if;

end process;

end trigger_2_arch;

В соответствии с алгоритмом (см. рис. 3.27) асинхронный сигнал CLR преобладает над тактовым входным сигналом C и поэтому проверяется первым в предложении "if". Только тогда, когда сигнал на входе CLR имеет неактивный уровень, вступает в действие то, что предусмотрено предложением "else". При наличии активного изменения на входе С исполняется последовательный сигнальный оператор присваивания. Булево выражение, по которому определяется новое значение выхода триггера Q, — это характеристическое уравнение триггера, полученное из его таблицы переходов.

Алгоритм функционирования триггера можно представить и путем непосредственной интерпретации его таблицы переходов

(рис. 3.28).

88

Рис. 3.28. Алгоритм функционирования триггера на основе таблицы переходов

Задать приведенный алгоритм на языке VHDL можно с помощью операторов case или if.

Когда нужно выбирать среди нескольких альтернатив на основании значения только одного сигнала или выражения, обычно более читабельным и дающим лучший результат синтеза является оператор case.

Описание алгоритма функционирования триггера с использованием оператора case приведено в листинге 3.3. Для его применения необходимо ввести векторную переменную А и затем образовать её из сигналов Е1 и Е2 (см. листинг 3.3).

На рис 3.29 приведен алгоритм функционирования триггера с синхронным установочным входом R предварительной установки в «0». По этому входу триггер будет установлен в «0» только при активном изменении сигнала на синхронизирующем входе.

89

Листинг 3.3. Описание триггера с использованием оператора case

entity trigger_2 is port (

CLR,C,E1,E2: in BIT; Q: buffer BIT

);

end trigger_2;

architecture trigger_2_arch of trigger_2 is begin

process (CLR,C)

variable A: BIT_VECTOR (1 downto 0);

begin |

|

|

|

A:= E1 & E2; |

then Q <= '0' ; |

||

if CLR='1' |

|||

elsif C'event |

and C='1' then |

||

case A is |

Q <= |

Q; |

|

when "00" => |

|||

when "01" => |

Q |

<= |

'0'; |

when "10" => |

Q |

<= |

'1'; |

when "11" => |

Q |

<= |

not Q; |

end case; end IF;

end process;

end trigger_2_arch;

В листинге 3.4 приведено описание триггера по данному алгоритму с использованием оператора if.

90

Рис. 3.29. Алгоритм функционирования триггера с синхронным входом предварительной установки в «0»

Листинг 3.4. Описание триггера с использованием оператора if

entity trigger_3_arch is port (R,E1,C,E2: in BIT;

Q: buffer BIT); end ff_4;

architecture trigger_3_arch of trigger_3 is begin

process (C) begin

if C'event and C='1' then

if R ='1' then Q <= '0' ;

elsif E1='0' and E2='0' then null; elsif E1='1' and E2='0' then Q <= '1' ; elsif E1='0' and E2='1' then Q <= '0' ;

elsif E1='1' and E2='1' then Q <= not Q ; end if;

end if; end process;

end trigger_3_arch;

91