- •СОДЕРЖАНИЕ

- •ВВЕДЕНИЕ

- •НАЧАЛЬНЫЕ СВЕДЕНИЯ О ПЛИС

- •Интегральные схемы типа FPGA

- •Перестраиваемый логический блок

- •Генераторы логических функций

- •Триггер

- •Блоки ввода/вывода сигналов

- •Программируемые соединения

- •Динамические параметры конфигурируемого логического блока

- •ОРГАНЫ УПРАВЛЕНИЯ УНИВЕРСАЛЬНОГО ЛАБОРАТОРНОГО СТЕНДА

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •Список литературы

- •ВВЕДЕНИЕ

- •ПРОЕКТИРОВАНИЕ ОДНОВЫХОДНОЙ КОМБИНАЦИОННОЙ СХЕМЫ

- •СИНТЕЗ КОМБИНАЦИОННЫХ МНОГОВЫХОДНЫХ СХЕМ

- •Реализация булевых функций с помощью постоянного запоминающего устройства

- •ПРОЕКТИРОВАНИЕ КОМБИНАЦИОННЫХ СХЕМ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •СИНХРОННЫЕ ТРИГГЕРЫ СО СТАТИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •СИНХРОННЫЕ ДВУХСТУПЕНЧАТЫЕ ТРИГГЕРЫ

- •СИНХРОННЫЕ ТРИГГЕРЫ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •УСЛОВНОЕ ГРАФИЧЕСКОЕ ОБОЗНАЧЕНИЕ ТРИГГЕРНЫХ СХЕМ

- •ПРОЕКТИРОВАНИЕ ТРИГГЕРНЫХ СХЕМ

- •ПРОЕКТИРОВАНИЕ СИНХРОННЫХ ДВУХСТУПЕНЧАТЫХ ТРИГГЕРОВ

- •ПОСТРОЕНИЕ СИНХРОННЫХ ТРИГГЕРОВ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •ПРОЕКТИРОВАНИЕ ТРИГГЕРНЫХ СХЕМ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •СИНТЕЗ СИНХРОННЫХ СЧЕТЧИКОВ

- •Матрица переходов триггера

- •ПРИМЕР

- •ПРОЕКТИРОВАНИЕ СЧЕТЧИКОВ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •ПРОЕКТИРОВАНИЕ МНОГОФУНКЦИОНАЛЬНОГО РЕГИСТРА

- •ДИНАМИЧЕСКИЕ ПАРАМЕТРЫ РЕГИСТРОВ

- •ПРОЕКТИРОВАНИЕ РЕГИСТРА НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •Статические и динамические состязания сигналов

- •Функциональные и логические состязания сигналов

- •Синтез схем, свободных от логических состязаний

- •Анализ комбинационных схем с целью выявления состязаний

- •СОСТЯЗАНИЯ СИГНАЛОВ В ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМАХ

- •Последовательностные схемы

- •Условия надежного функционирования асинхронной схемы

- •Критические состязания

- •Существенные состязания

- •Анализ асинхронных последовательностных схем

- •Устранение критических состязаний

- •ЭКСПЕРИМЕНТАЛЬНОЕ ИССЛЕДОВАНИЕ СОСТЯЗАНИЙ СИГНАЛОВ

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •Логические элементы

- •Мультиплексоры

- •Описание цифрового осциллографа

- •Запуск и настройка осциллографа

- •Настройка изображения сигнала на экране осциллографа

- •Получение устойчивого изображения сигнала

- •Выбор цены деления по оси Х и Y

- •Выбор фронта сигнала по входу Х осциллографа

- •Измерение временных интервалов (измерение задержек)

Лабораторная работа 5

ПРОЕКТИРОВАНИЕ МНОГОФУНКЦИОНАЛЬНЫХ РЕГИСТРОВ

Цель: изучить один из основных узлов цифровых схем — регистр хранения и сдвига; овладеть методом проектирования многофункциональных регистров; получить навыки проектирования многофункциональных регистров на VHDL; приобрести опыт экспериментального исследования регистра.

ВВЕДЕНИЕ

Упорядоченную последовательность запоминающих элементов, предназначенную для хранения информации, называют регистром. При построении регистров в качестве запоминающих элементов обычно используют триггерные схемы. Запоминающие элементы (разряды) регистра нумеруют любым удобным образом. Как правило, регистры снабжают дополнительными цепями, которые позволяют выполнять различные микрооперации: прием, выдачу, сдвиг и преобразование кодов.

Регистры имеют широкий диапазон применений. Они обеспечивают создание управляющих, контролирующих и запоминающих схем, генераторов кодов, последовательно-параллельных и парал- лельно-последовательных преобразователей кодов, арифметических блоков и т.д. В настоящей работе рассматривается проектирование регистров с заданным набором микроопераций.

Регистры сдвига

При реализации различных операций в арифметическом и других устройствах компьютеров широкое применение находят различные виды сдвигов информации. Операция сдвига, как правило, выполняется на регистрах сдвига. Регистр сдвига представляет со-

119

бой схему на триггерах, соединения между которыми, называемые цепями сдвига, обеспечивают передачу двоичной информации от одних триггеров регистра к другим.

Сдвиги могут выполняться на один или несколько разрядов одновременно. Применяются сдвиги на k разрядов как в сторону младших разрядов числа (правый сдвиг), так и в сторону старших разрядов числа (левый сдвиг). Операция сдвига кода в регистре означает, что каждый триггер Тi этого регистра должен передать хранимую информацию элементу Тi+k и после этого принять информацию от триггера Тi-k (сдвиг на k разрядов).

В некоторых случаях освобождающиеся при сдвиге k старших (младших) разрядов регистра или сохраняют прежнее состояние, или заполняются нулями, или принимают новую информацию извне. Информация, выдвигаемая из k младших (старших) разрядов регистра, теряется или передается во внешние цепи. В других случаях регистр может быть замкнут в кольцо так, что информация, выдвигаемая из младших (старших) разрядов регистра, принимается в освобождающиеся триггеры старших (младших) разрядов регистра.

Основная трудность, которая возникает при построении регистров сдвига, состоит в том, что при выполнении сдвига каждый запоминающий элемент (разряд) должен одновременно и выдавать информацию в следующий разряд, и принимать новую информацию из предыдущего разряда. Поэтому при построении регистров сдвига используют синхронные триггеры с динамическим управлением записью либо с двухступенчатой организацией. Внутренняя организация данных триггерных схем предусматривает разделение во времени этапов приема входной информации и смены выходного сигнала триггера. По одному фронту синхронизирующего импульса происходит прием информации, по другому — смена выходного сигнала. Это позволяет обойтись одним триггером на каждый разряд при построении регистров сдвига.

Регистр сдвига на один разряд

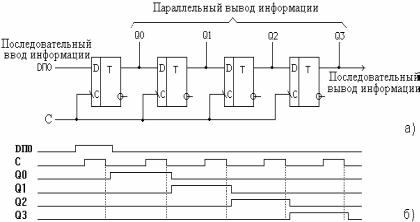

На рис. 5.1(а) изображена схема четырехразрядного регистра сдвига на один разряд вправо на D-триггерах. Для реализации функции сдвига вправо необходимо соединить прямой выход триг-

120

гера i-го разряда с входом D триггера (i+1)-го разряда. Объединенные синхронизирующие входы всех триггеров образуют шину сдвига.

Сдвиг на один разряд выполняется подачей одного импульса на шину сдвига. В момент поступления импульса значения сигналов на входе D каждого триггера определяют его переход в новое состояние. Это новое состояние каждый триггер принимает после окончания синхроимпульса (данный триггер переключается по заднему фронту синхроимпульса). На рис. 5.1(б) приведена временная диаграмма, поясняющая работу регистра сдвига.

Рис. 5.1. Регистр сдвига (а) и диаграмма его работы (б)

Последовательный входной сигнал DП0 — это новый бит, который «вдвигается» с одного конца на данном такте. Этот бит появляется на последовательном выходе Q3 спустя 4 такта и теряется на следующем такте (см. рис. 5.1). Таким образом, n-разрядный регистр сдвига с последовательным вводом и последовательным выводом можно использовать для задержки сигнала на п тактов.

Если у регистра сдвига с последовательным вводом выведены наружу выходы всех триггеров и они доступны для других схем (см. рис. 5.1), то таким регистром можно воспользоваться для выполнения преобразования последовательного кода в параллельный.

121

Регистр сдвига на k разрядов

Если регистр выполняет микрооперацию сдвига на один разряд, то для сдвига кода на k разрядов необходимо подать k импульсов сдвига. Для уменьшения времени, требуемого для k-разрядного сдвига, в регистре можно организовать цепи сдвига кода одновременно на k разрядов.

Регистр сдвига на два разряда вправо, построенный на D- триггерах, приведен на рис. 5.2. Цепи сдвига соединяют выход i-го триггера регистра с входом D (i-2)-го триггера.

Из(i+3)-горазряда

|

|

|

|

|

|

|

|

|

|

|

В(i-2)-йразряд |

|

Из(i+4)-го |

|

|

|

|

|

|

|

|

|

|

|

В(i-3)-й |

|

|

|

|

|

|

|

|

|

|

|

||

разряда |

D |

T |

|

D |

T |

|

D |

T |

|

D |

T |

разряд |

|

C |

i+2 |

|

C |

i+1 |

|

C |

i |

|

C |

i-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

С

Рис. 5.2. Регистр сдвига на два разряда

Реверсивные регистры сдвига

В цифровых устройствах часто используют регистры, на которых выполняется как микрооперация сдвига кода влево, так и микрооперация сдвига кода вправо. Регистры, выполняющие как левый, так и правый сдвиги, называют реверсивными регистрами сдвига. Схема такого регистра на D-триггерах показана на рис. 5.3.

Данный регистр помимо шины сдвига С имеет управляющий вход У. Его назначение состоит в том, чтобы из двух микроопераций сдвига, выполняемых регистром, выбрать одну, требуемую в данный момент времени. Таким образом, сигнал, поступающий на вход У, настраивает определенную цепь сдвига от одних триггеров к другим и запрещает работу остальных цепей. При У = 0, информация сдвигается от Q0 к Q3, а при У = 1 — от

Q3 к Q0 (см. рис. 5.3).

122

Рис. 5.3. Реверсивный регистр сдвига

Очевидно, на одном и том же регистре можно организовать выполнение нескольких различных сдвигов как влево, так и вправо. При этом увеличивается и число управляющих входов.

Параллельный ввод информации в регистрах сдвига

В рассмотренных выше схемах регистра сдвига предполагается последовательный ввод информации. Однако важна и возможность параллельного ввода информации. Пример схемы регистра сдвига с последовательным и параллельным вводом и выводом информации приведен на рис. 5.4. Данный регистр построен на D-триггерах, имеющих вход разрешения синхросигнала СЕ. Обозначения входов регистра соответствуют тем, которые приняты в условных графических обозначениях регистров сдвига библиотеки элементов сис-

темы Xilinx Foundation:

С (clock) — вход синхронизации,

123

СЕ (clock enable) — вход разрешения синхросигнала; высокий уровень на этом входе разрешает изменение состояния регистра по фронту синхросигнала,

L (load enable) — вход разрешения параллельной загрузки; высокий уровень на этом входе разрешает параллельную загрузку регистра по входам D0÷Dn,

SLI (shift-left serial input) — левый последовательный вход данных (левый разряд регистра имеет индекс 0),

D0÷Dn — параллельные входы данных.

Рис. 5.4. Регистр сдвига с последовательным и параллельным приемом и выводом информации

Микрооперации, выполняемые данным регистром, приведены в табл. 5.1. Регистр выполняет следующие элементарные операции:

124

параллельный прием (загрузку) n-разрядного кода, сдвиг на 1 разряд (от Q0 к Qn) и хранение.

|

|

|

|

|

|

Таблица 5.1 |

|

|

|

Таблица микроопераций регистра |

|||

|

|

|

|

|

|

|

|

|

Входы |

|

Микрооперация |

||

L |

CE |

SLI |

|

Dn–D0 |

C |

|

1 |

X |

X |

|

Dn – D0 |

0/1 |

Загрузка по входам DnD0 |

0 |

1 |

SLI |

|

X |

0/1 |

Сдвиг вправо от Q0 к Qn |

|

(Q0 =SLI, Q1 = Q0, …, |

|||||

|

|

|

|

|

|

|

|

|

X |

|

|

|

Qn = Qn-1) |

0 |

0 |

|

X |

X |

Хранение |

|

Состояние входа L определяет одну из двух микроопераций: параллельную загрузку (L = 1) или сдвиг (L = 0). Регистр устанавливается в любое требуемое состояние при L = 1 подачей кода на параллельные входы D0 — Dn и синхроимпульса на вход С. Обратим внимание, что вход разрешения CE может находиться в произвольном состоянии, поскольку единичное значение сигнала L через элемент ИЛИ поступает на разрешающие входы CE триггеров (см. рис. 5.4).

При L = 0 синхроимпульс, приходящий на вход С, по фронту 0/1 реализует сдвиг хранимой в регистре информации на 1 разряд только при единичном значении сигнала на входе CE регистра. При этом вход SLI служит для последовательного приема информации в регистр (см. рис. 5.4).

Последовательный вывод информации происходит подачей серии тактовых импульсов на шину сдвига и снятием кода с выхода триггера последнего разряда регистра (см. рис. 5.4).

Параллельный вывод информации может быть осуществлен непосредственно с выходов триггеров регистра (см. рис. 5.4).

Все эти возможности расширяют область применения регистров сдвига. Они могут быть использованы полностью или частично в зависимости от применения регистра. Например, с помощью регистра сдвига с параллельным вводом и последовательным выводом можно осуществить преобразование параллельного кода в последовательный.

125