- •СОДЕРЖАНИЕ

- •ВВЕДЕНИЕ

- •НАЧАЛЬНЫЕ СВЕДЕНИЯ О ПЛИС

- •Интегральные схемы типа FPGA

- •Перестраиваемый логический блок

- •Генераторы логических функций

- •Триггер

- •Блоки ввода/вывода сигналов

- •Программируемые соединения

- •Динамические параметры конфигурируемого логического блока

- •ОРГАНЫ УПРАВЛЕНИЯ УНИВЕРСАЛЬНОГО ЛАБОРАТОРНОГО СТЕНДА

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •Список литературы

- •ВВЕДЕНИЕ

- •ПРОЕКТИРОВАНИЕ ОДНОВЫХОДНОЙ КОМБИНАЦИОННОЙ СХЕМЫ

- •СИНТЕЗ КОМБИНАЦИОННЫХ МНОГОВЫХОДНЫХ СХЕМ

- •Реализация булевых функций с помощью постоянного запоминающего устройства

- •ПРОЕКТИРОВАНИЕ КОМБИНАЦИОННЫХ СХЕМ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •СИНХРОННЫЕ ТРИГГЕРЫ СО СТАТИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •СИНХРОННЫЕ ДВУХСТУПЕНЧАТЫЕ ТРИГГЕРЫ

- •СИНХРОННЫЕ ТРИГГЕРЫ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •УСЛОВНОЕ ГРАФИЧЕСКОЕ ОБОЗНАЧЕНИЕ ТРИГГЕРНЫХ СХЕМ

- •ПРОЕКТИРОВАНИЕ ТРИГГЕРНЫХ СХЕМ

- •ПРОЕКТИРОВАНИЕ СИНХРОННЫХ ДВУХСТУПЕНЧАТЫХ ТРИГГЕРОВ

- •ПОСТРОЕНИЕ СИНХРОННЫХ ТРИГГЕРОВ С ДИНАМИЧЕСКИМ УПРАВЛЕНИЕМ ЗАПИСЬЮ

- •ПРОЕКТИРОВАНИЕ ТРИГГЕРНЫХ СХЕМ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •СИНТЕЗ СИНХРОННЫХ СЧЕТЧИКОВ

- •Матрица переходов триггера

- •ПРИМЕР

- •ПРОЕКТИРОВАНИЕ СЧЕТЧИКОВ НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •ПРОЕКТИРОВАНИЕ МНОГОФУНКЦИОНАЛЬНОГО РЕГИСТРА

- •ДИНАМИЧЕСКИЕ ПАРАМЕТРЫ РЕГИСТРОВ

- •ПРОЕКТИРОВАНИЕ РЕГИСТРА НА VHDL

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •ВВЕДЕНИЕ

- •Статические и динамические состязания сигналов

- •Функциональные и логические состязания сигналов

- •Синтез схем, свободных от логических состязаний

- •Анализ комбинационных схем с целью выявления состязаний

- •СОСТЯЗАНИЯ СИГНАЛОВ В ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМАХ

- •Последовательностные схемы

- •Условия надежного функционирования асинхронной схемы

- •Критические состязания

- •Существенные состязания

- •Анализ асинхронных последовательностных схем

- •Устранение критических состязаний

- •ЭКСПЕРИМЕНТАЛЬНОЕ ИССЛЕДОВАНИЕ СОСТЯЗАНИЙ СИГНАЛОВ

- •ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ

- •ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

- •ОТЧЕТ ПО РАБОТЕ

- •Список литературы

- •Логические элементы

- •Мультиплексоры

- •Описание цифрового осциллографа

- •Запуск и настройка осциллографа

- •Настройка изображения сигнала на экране осциллографа

- •Получение устойчивого изображения сигнала

- •Выбор цены деления по оси Х и Y

- •Выбор фронта сигнала по входу Х осциллографа

- •Измерение временных интервалов (измерение задержек)

Регистры сдвига с обратными связями

На базе регистра сдвига можно построить схемы с различными функциональными возможностями. При введении обратных связей регистры сдвига могут работать как счетчики, генераторы кодов; дополнительная логика позволяет использовать их для преобразования кодов, умножения и деления чисел и т.д. Важно, что все эти функции реализуются с помощью сравнительно несложной комбинационной схемы.

Наиболее простая схема с обратными связями получается, если выход последнего разряда регистра сдвига соединить с входом последовательного ввода данных. В этом случае непрерывная серия синхроимпульсов, подаваемых на шину сдвига, будет осуществлять режим циркуляции сдвигаемой информации. В режиме замкнутого в кольцо регистра сдвига по осциллограмме выходных сигналов легко установить, правильно работает регистр или нет, а также определить динамические параметры регистра сдвига.

ПРОЕКТИРОВАНИЕ МНОГОФУНКЦИОНАЛЬНОГО РЕГИСТРА

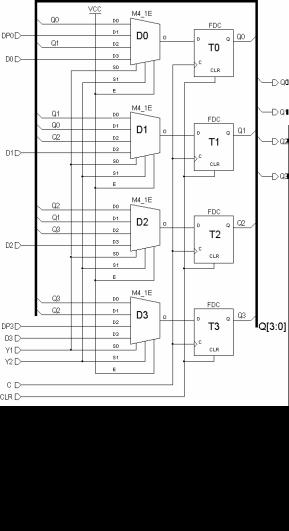

Обобщенная схема логической структуры многофункционального регистра приведена на рис. 5.5.

На логические входы триггеров регистра информация может поступать как с внешних входов, так и по обратной связи с выходов триггеров через комбинационную схему КС1 (см. рис. 5.5). С ее помощью можно реализовать широкий набор микроопераций. Это различные микрооперации преобразования кода, хранимого в триггерах регистра, например, логические и арифметические сдвиги, получение обратного кода и т.п., а также загрузка кода в регистр и синхронная установка регистра в состояние «0» или «1» по входам

R или S.

Выбор требуемой микрооперации осуществляется с помощью управляющих входов У. Исполнение выбранной микрооперации происходит с поступлением импульса на синхронизирующий вход С при наличии разрешающего сигнала СЕ.

126

Рис. 5.5. Обобщенная схема логической структуры многофункционального регистра, где:

С — синхронизирующий вход; CE — вход разрешения синхросигнала; CLR — асинхронный вход установки регистра в «0»; R, S — синхронные входы установки регистра в «0» и «1»; D — входы для параллельного приема информации; DP — входы для последовательного приема информации; У — управляющие входы

Комбинационная схема КС2 реализует приоритет среди управляющих и установочных входов. Например, cинхронный вход R должен иметь наивысший приоритет и обеспечивать установку регистра в «0» вне зависимости от состояния других управляющих входов. Напомним, синхронная установка в «0» реализуется подачей импульса на синхровход С при R = 1. Другой пример, вход раз-

127

решения параллельной загрузки L имеет более высокий приоритет, чем вход разрешения синхросигнала СЕ (см. рис. 5.4 и табл. 5.1).

При проектировании регистра с требуемым набором микроопераций прежде всего необходимо определить число управляющих входов и задать их приоритет. Число управляющих входов находят по следующей формуле: k = [log2M] + 1,где М — число микроопераций. Далее задача логического проектирования схемы регистра заключается в составлении функций возбуждения каждого триггера. Поскольку структура регистра регулярна, то достаточно получить выражения только для одного триггера.

ПРИМЕР

Требуется спроектировать многофункциональный регистр на D- триггерах без входа разрешения синхросигнала СЕ, который должен выполнять следующие микрооперации:

1)сдвиг кода влево на 1 разряд;

2)сдвиг кода вправо на 1 разряд;

3)параллельную загрузку;

4)хранение при наличии синхронизирующих импульсов (СИ) на входе С регистра;

5)асинхронную установку регистра в «0».

Проектирование комбинационной схемы КС1

При реализации микроопераций, выполняемых по логическим входам триггеров регистра, вначале необходимо определить число управляющих входов У. Микрооперация асинхронной установки регистра в «0» реализуется при использовании D-триггеров, имеющих соответствующие входы (CLR) асинхронного сброса.

Остальные четыре микрооперации выполняются при поступлении СИ на синхронизирующий вход С регистра. Следовательно, регистр должен иметь два управляющих входа У1 и У2. Выберем вариант кодирования микроопераций, представленный в табл. 5.2.

128

Таблица 5.2

Кодирование микроопераций регистра

Вход У1 |

Вход У2 |

Микрооперация |

|

|

|

|

|

|

0 |

0 |

Хранение |

|

|

|

0 |

1 |

Сдвиг влево на 1 разряд |

|

|

|

1 |

0 |

Сдвиг вправо на 1 разряд |

|

|

|

1 |

1 |

Параллельная загрузка |

|

|

|

По условию задания необходимо обеспечить режим хранения при наличии синхронизирующих импульсов на входе С регистра. Это можно реализовать перезаписью текущего состояния регистра при поступлении синхронизирующих импульсов.

Режим хранения реализуется подачей на D вход триггера сигнала с выхода Q этого же триггера. Составим таблицу истинности функции возбуждения fi логического входа триггера i-го разряда регистра (табл. 5.3).

|

|

|

|

|

|

|

|

Таблица 5.3 |

|

Функция возбуждения входа Dтрi триггера i-го разряда |

|||||||

|

|

|

|

|

|

|

|

|

У1 |

|

|

У2 |

Qi+1 |

Qi-1 |

Di |

Qi |

fi |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

X |

X |

X |

0 |

0 |

|

0 |

|

0 |

X |

X |

X |

1 |

1 |

|

0 |

|

1 |

0 |

X |

X |

X |

0 |

|

0 |

|

1 |

1 |

X |

X |

X |

1 |

|

1 |

|

0 |

X |

0 |

X |

X |

0 |

|

1 |

|

0 |

X |

1 |

X |

X |

1 |

|

1 |

|

1 |

X |

X |

0 |

X |

0 |

|

1 |

|

1 |

X |

X |

1 |

X |

1 |

|

Примечание. Di — внешний вход регистра для параллельного приема информации в i-ый разряд.

129

Непосредственно из таблицы, используя правило записи функции по единицам и опуская те переменные, которые могут иметь произвольное значение (×), можно записать выражение для функции fi:

fi =Y1 Y2 Qi Y1 Y2 Qi+1 Y1 Y2 Qi−1 Y1 Y2 Di .

Схема, реализующая данное выражение, — это мультиплексор с двумя адресными входами.

Логическая схема многофункционального регистра, построенная на библиотечных элементах ПЛИС XC10PC84, приведена на рис. 5.6.

Рис. 5.6. Схема многофункционального регистра

130

Условное графическое обозначение (УГО) регистра приведено на рис. 5.7, а временная диаграмма его дана на рис. 5.8.

Рис. 5.7. Условное графическое обозначение многофункционального регистра

Рис. 5.8. Временная диаграмма работы многофункционального регистра

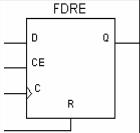

При проектировании схемы регистра с синхронной установкой в «0» следует использовать триггер с синхронной установкой в «0», например, D-триггер FDRE.

131

Условное графическое обозначения D-триггера FDRE приведено на рис. 5.9, а его таблица переходов представлена табл. 5.4.

Рис.5.9.УсловноеграфическоеобозначениеD-триггераFDRE

Рис.5.9.УсловноеграфическоеобозначениеD-триггераFDRE

|

Таблица переходов D-триггера FDRE |

Таблица 5.4 |

||||

|

|

|

||||

|

|

|

|

|

|

|

|

|

Входы |

|

Выход |

|

|

R |

CE |

|

D |

C |

Q |

|

1 |

X |

|

X |

0/1 |

0 |

|

0 |

0 |

|

X |

X |

Q |

|

0 |

1 |

|

1 |

0/1 |

1 |

|

0 |

1 |

|

0 |

0/1 |

0 |

|

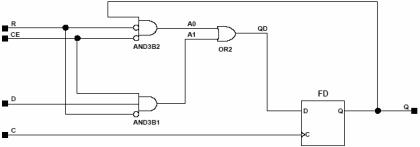

Данный триггер является макроэлементом, его структура приведена на рис. 5.10.

Рис. 5.10. Внутренняя структура D-триггера FDRE

132