- •1. Основы микросхемотехники ИС

- •1.1. Основные термины и определения

- •1.2. Этапы и направления развития ИС

- •1.3. Классификация ИС

- •1.3.4. Классификация по степени интеграции

- •1.4. Последовательность разработки ИС

- •2. Основы цифровой техники

- •2.3. Основные логические операции

- •2.4. Формы представления логической функции

- •2.5. Структурное проектирование цифровых схем комбинационного типа

- •3. Основные параметры и характеристики ЦИС

- •3.1. Основные параметры ЦИС

- •3.2. Характеристики ЦИС

- •3.3. Определение измеряемых параметров по характеристикам

- •4.1. Формирование биполярных транзисторов

- •4.3. Эквивалентная модель интегрального n–p–n биполярного транзистора

- •4.4. Режимы работы биполярного транзистора

- •4.6. Статические ВАХ транзистора

- •5. Диоды в интегральных схемах

- •5.1. Модель идеального диода

- •5.2. Эквивалентная схема интегрального диода

- •5.3. Аппроксимации ВАХ диода

- •5.4. Варианты реализации интегральных диодов

- •6. Пассивные элементы ИС

- •6.1. Основные параметры резисторов

- •6.2. Реализация интегральных резисторов

- •6.4. Реализация интегральных конденсаторов

- •7. Элементная база статических ЦИС на биполярных транзисторах

- •7.1. Резисторно-транзисторная логика (РТЛ)

- •7.1.1. Характеристики РТЛ

- •7.2. Эмиттерно-связанная логика (ЭСЛ)

- •7.2.1. Принцип работы

- •7.2.2. Входная характеристика

- •7.2.3. Передаточная характеристика

- •7.2.4. Выходная характеристика

- •7.2.6. Многоярусные ЭСЛ (МяЭСЛ)

- •7.3. Диодно-транзисторная логика

- •7.3.1. Расчет передаточной и входной характеристик

- •7.3.2. Выходная характеристика

- •7.3.3. Влияние нагрузки на логические уровни

- •7.4. Транзисторно-транзисторная логика

- •7.4.1. ТТЛ-элемент с простым инвертором

- •7.4.2. Передаточная характеристика

- •7.4.3. Входная характеристика

- •7.4.4. Выходная характеристика

- •7.4.6. Основные параметры

- •7.4.7. Многоэмиттерный транзистор

- •7.4.8. ТТЛ-элемент со сложным выходным каскадом

- •7.4.9. Модификация логического элемента

- •7.5. Интегральная инжекционная логика

- •7.5.2. Реализация логических функций

- •8. Полевые транзисторы

- •8.1. Типы полевых транзисторов

- •8.2. Определение физических параметров

- •8.3. модель полевого транзистора

- •8.4. Режимы работы и уравнения ВАХ полевого транзистора

- •9. Элементная база на полевых транзисторах

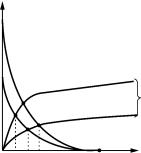

- •9.2. Передаточная характеристика и параметры инвертора с линейной нагрузкой

- •9.3. Передаточная характеристика и параметры инвертора с нелинейной нагрузкой

- •9.4. Передаточная характеристика и параметры инвертора с квазилинейной нагрузкой

- •9.5. Передаточная характеристика и параметры инвертора с токостабилизирующей нагрузкой

- •9.6. Передаточная характеристика и параметры комплементарного инвертора

- •9.8. Логические элементы на МОП-транзисторах

- •9.9. Определение эквивалентной крутизны группы переключающих транзисторов

- •9.11. Влияние параметров транзисторов на характеристики логического элемента

- •9.12. Сопряжение ТТЛ- и КМОП-схем

Наименьшее значение уровня логического нуля соответствует наибольшей крутизне, определяемой с учетом всех параллельных цепей включения транзисторов kmax = 3k/5.

9.11. Влияние параметров транзисторов на характеристики логического элемента

Пороговое напряжение UПОР0 , коэффициент влияния подложки η, удельная крутизна kУД - физические параметры, которые определяются технологической структурой транзистора.

Напряжение уровня логической единицы U1 для элементов с линейной, квазилинейной, токостабилизирующей нагрузкой и КМОП пропорционально UИП; для элемента с нелинейной нагрузкой

-U ПОР0 .

1+ h

Таким образом, U1 зависит от условий эксплуатации UИП и

физических параметров UПОР0 , η.

Схемы логических элементов на МОП-транзисторах называются схемами с отношением, поскольку напряжение уровня логического нуля зависит от соотношения kН/k0.

Так как

k = kУД WL ,

то

U 0 » WН × L0 . LН ×W0

Если крутизну нагрузочного транзистора увеличить в 2 раза,

то

kН↑(WН↑ или LН↓), I2kН > IkН в 2 раза,

U20kН > U 0 (рис.9.34).

204

IC0,IН

2kН |

|

|

2k0 |

kН |

IC0 |

|

k0 |

U20k0 U0 U20kН |

UВЫХ |

Рис.9.34. Влияние крутизны транзисторов на уровень логического нуля U0

Если крутизну переключающего транзистора увеличить в 2 раза, то

k0↑ (W0↑ или L0↓), I2k0 > Ik0 в 2 раза,

0 < U 0 (см. рис.9.34).

Для обеспечения высоких помехоустойчивости и помехозащищенности логического элемента необходимо понижать напряжение уровня логического нуля, т.е. уменьшать крутизну нагрузочного транзистора и увеличивать крутизну переключающего транзистора.

9.12. Сопряжение ТТЛ- и КМОП-схем

Наиболее широкое применение имеют логические элементы на МОП-транзисторах, поскольку по своим логическим уровням совместимы с ТТЛ-элементами. НСТ-схемы - быстродействую-

щие КМОП, совместимые с ТТЛ (High-speed CMOS, TTL compatible), работают с напряжением питания 5 В и их можно использовать совместно с ТТЛ-схемами, работающими с таким же напряжением питания. Логические уровни НСТ-схем составляют U1 = (2÷3,4) В, U0 = (0,33÷0,8) В. Эти уровни устанавливаются в

205

процессе изготовления путем создания транзисторов с разными порогами переключения, что приводит к различным передаточным характеристикам.

При сопряжении ТТЛ- и КМОП-схем следует учитывать:

1)запас помехоустойчивости по постоянномй току, который зависит от напряжения на выходе схемы, являющегося источником сигнала, а также напряжения на входе, подключенного

кданному выходу;

2)коэффициент разветвления по выходу. Если ТТЛ-схема управляет КМОП, то проблем не возникает, так как при любом уровне сигнала входы КМОП представляют собой емкостную нагрузку. Если КМОП управляет ТТЛ-схемой, особенно при низком уровне входного сигнала, то требуется значительный ток по сравнению с возможностями выходных каскадов НСТ-схем;

3)величину емкостной нагрузки, которая приводит к увеличению как задержки, так и мощности рассеивания. Особенно чувствительным к емкостной нагрузке является НСТ-элемент.

Втабл. 9.3 приведены параметры, характеризующие логические элементы. Из нее следует, что КМОП с напряжением питания 3,3 В могут работать совместно с ТТЛ-схемами с напряжением питания 5 В.

Таблица 9.3

Сравнение логических уровней различных элементов

Параметр, В |

КМОП |

|

ТТЛ |

UИП |

5 |

3,3 |

5 |

1 |

4,44 |

2,4 |

2,4 |

UВЫХ |

|||

UВХ1 |

3,5 |

2,0 |

2,0 |

UП |

2,5 |

1,5 |

1,5 |

UВХ0 |

1,5 |

0,8 |

0,8 |

0 |

0,5 |

0,4 |

0,4 |

UВЫХ |

На входы элемента не всегда можно подавать напряжение, превышающее напряжение питания UИП. Эта проблема возникает

206

в том случае, если в системе применяются логические схемы с напряжением питания как 5 В так и 3,3 В.

|

UИП |

|

M2 |

UИП |

UЗ2 = UВЫХ |

|

|

UЗ2 = UИП |

M3 |

UЗ3 = UИП |

|

M2 |

|

UВЫХ |

UВЫХ |

M1 |

M1 |

UЗ1 = 0 |

UЗ1 = 0 |

а |

б |

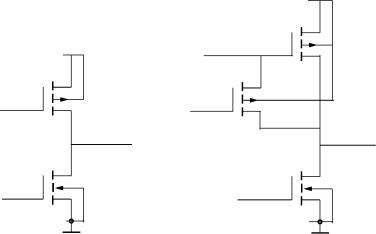

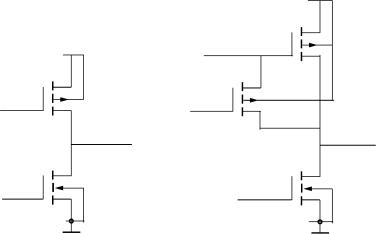

Рис.9.36. Схемы выходных каскадов с тремя состояниями: а - не допускающие напряжение 5 В; б - допускающие напряжение 5

В

На рис. 9.35,а приведена схема входного каскада НСТ, которая содержит два смещенных в обратном направлении фиксирующих диода. Диод Д2, включенный между входом и шиной питания, замыкает вход на шину питания, когда входной сигнал превышает напряжение питания UИП. С помощью диода Д1 шунтируют вход на землю, когда входной сигнал становится отрицательным во время переходного процесса. Однако вход с шунтирующими диодами имеет небольшое входное сопротивление в отличие от КМОП, которое определяется сопротивлением смещенного в прямом направлении диода, по которому потечет большой ток. На рис. 9.35,б приведена КМОП-схема, на вход которой можно подавать напряжение 5 В. Во входном каскаде отсутствует диод Д2, но благодаря диоду Д1 сохраняется шунтирование при отрицательных выбросах напряжения. В этом случае

207

транзисторы, используемые в схемах, должны выдерживать напряжения большие, чем UИП.

Когда выходы схемы с тремя состояниями с напряжением питания 3,3 и 5 В объединяются, то необходимо проверить возможность выходных цепей выдерживать напряжение 5 В. Схема с источником 5 В является источником сигнала для выхода 3,3- вольтовой схемы. На рис.9.36,а в обычной КМОП-схеме, находящейся в состоянии высокого импеданса на выходе, если напряжение на затворе М1 поддерживается равным 0 В, а напряжение на затворе М2 - равным напряжению питания, то оба транзистора закрыты. Далее, если на выход элемента с питанием 3,3 В поступает напряжение 5 В, то на стоке М2 будет 5 В, тогда как на затворе - 3,3 В. Так как потенциал затвора ниже, чем потенциал стока, то М2 откроется и потечет большой ток с выхода до шины питания. Таким образом, напряжение 5 В для этих схем недопустимо.

|

UИП |

|

M2 |

UИП |

UЗ2 = UВЫХ |

|

|

UЗ2 = UИП |

M3 |

UЗ3 = UИП |

|

M2 |

|

UВЫХ |

UВЫХ |

M1 |

M1 |

UЗ1 = 0 |

UЗ1 = 0 |

а |

б |

Рис.9.36. Схемы выходных каскадов с тремя состояниями: а - не допускающие напряжение 5 В; б - допускающие напряжение 5

В

208

На рис.9.36,б приведен выходной каскад, допускающий напряжение 5 В. Дополнительный p-канальный транзистор М3 предотвращает отпирание М2. Если напряжение на выходе выше напряжения питания, то открывается М3, обеспечивая малое сопротивление между выходом и затвором М2. При этом транзистор М2 остается закрытым, поскольку напряжение на его затворе выше напряжения на стоке.

Итак, при применении в одной системе ТТЛ и КМОП с пониженным питанием следуют три правила сопряжения:

1)выходы КМОП можно непосредственно подавать на входы ТТЛ при соблюдении обычных ограничений на выходной ток;

2)выходы ТТЛ можно непосредственно соединять со входами КМОП, если они допускают входные напряжения

5 В;

3)выходы ТТЛ и КМОП в третьем состоянии можно соединять, если выходы КМОП допускают напряжение 5 В.

209