- •1. Основы микросхемотехники ИС

- •1.1. Основные термины и определения

- •1.2. Этапы и направления развития ИС

- •1.3. Классификация ИС

- •1.3.4. Классификация по степени интеграции

- •1.4. Последовательность разработки ИС

- •2. Основы цифровой техники

- •2.3. Основные логические операции

- •2.4. Формы представления логической функции

- •2.5. Структурное проектирование цифровых схем комбинационного типа

- •3. Основные параметры и характеристики ЦИС

- •3.1. Основные параметры ЦИС

- •3.2. Характеристики ЦИС

- •3.3. Определение измеряемых параметров по характеристикам

- •4.1. Формирование биполярных транзисторов

- •4.3. Эквивалентная модель интегрального n–p–n биполярного транзистора

- •4.4. Режимы работы биполярного транзистора

- •4.6. Статические ВАХ транзистора

- •5. Диоды в интегральных схемах

- •5.1. Модель идеального диода

- •5.2. Эквивалентная схема интегрального диода

- •5.3. Аппроксимации ВАХ диода

- •5.4. Варианты реализации интегральных диодов

- •6. Пассивные элементы ИС

- •6.1. Основные параметры резисторов

- •6.2. Реализация интегральных резисторов

- •6.4. Реализация интегральных конденсаторов

- •7. Элементная база статических ЦИС на биполярных транзисторах

- •7.1. Резисторно-транзисторная логика (РТЛ)

- •7.1.1. Характеристики РТЛ

- •7.2. Эмиттерно-связанная логика (ЭСЛ)

- •7.2.1. Принцип работы

- •7.2.2. Входная характеристика

- •7.2.3. Передаточная характеристика

- •7.2.4. Выходная характеристика

- •7.2.6. Многоярусные ЭСЛ (МяЭСЛ)

- •7.3. Диодно-транзисторная логика

- •7.3.1. Расчет передаточной и входной характеристик

- •7.3.2. Выходная характеристика

- •7.3.3. Влияние нагрузки на логические уровни

- •7.4. Транзисторно-транзисторная логика

- •7.4.1. ТТЛ-элемент с простым инвертором

- •7.4.2. Передаточная характеристика

- •7.4.3. Входная характеристика

- •7.4.4. Выходная характеристика

- •7.4.6. Основные параметры

- •7.4.7. Многоэмиттерный транзистор

- •7.4.8. ТТЛ-элемент со сложным выходным каскадом

- •7.4.9. Модификация логического элемента

- •7.5. Интегральная инжекционная логика

- •7.5.2. Реализация логических функций

- •8. Полевые транзисторы

- •8.1. Типы полевых транзисторов

- •8.2. Определение физических параметров

- •8.3. модель полевого транзистора

- •8.4. Режимы работы и уравнения ВАХ полевого транзистора

- •9. Элементная база на полевых транзисторах

- •9.2. Передаточная характеристика и параметры инвертора с линейной нагрузкой

- •9.3. Передаточная характеристика и параметры инвертора с нелинейной нагрузкой

- •9.4. Передаточная характеристика и параметры инвертора с квазилинейной нагрузкой

- •9.5. Передаточная характеристика и параметры инвертора с токостабилизирующей нагрузкой

- •9.6. Передаточная характеристика и параметры комплементарного инвертора

- •9.8. Логические элементы на МОП-транзисторах

- •9.9. Определение эквивалентной крутизны группы переключающих транзисторов

- •9.11. Влияние параметров транзисторов на характеристики логического элемента

- •9.12. Сопряжение ТТЛ- и КМОП-схем

8. Полевые транзисторы

Полевые транзисторы первоначально назывались МДП - ме- талл-диэлектрик-полупроводник, но поскольку в интегральном исполнении в качестве диэлектрика использовали окисел, то они стали называться МОП - металл-окисел-полупроводник.

Полевой транзистор - униполярный прибор, в котором работает один тип носителей. Если работают электроны, то прибор называется n-МОП, если работают дырки - p-МОП. В основе полевого транзистора лежит принцип модуляции проводимости сток-исток.

8.1. Типы полевых транзисторов

Существует четыре типа транзисторов.

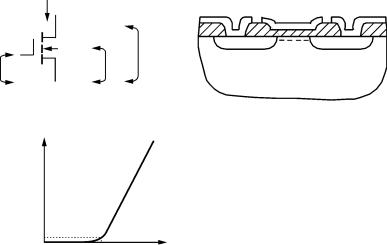

1. МОП-транзистор с индуцированным каналом (рис.8.1 и 8.2). Напряжение UЗИ при токе стока IС = 1 мкА называется пороговым напряжением, т.е. напряжением, при котором открывается транзистор.

|

IС |

|

Исток |

Затвор(+) |

Сток |

|

Сток |

|

|

|

|

Затвор |

Подложка |

n+ |

|

n+ |

|

UЗИ |

Исток |

UПИ |

UСИ |

p-подложка |

|

|

|

||||

|

|

|

|||

|

а |

|

|

б |

|

|

IС |

|

|

|

|

|

Рис.8.1. n-МОП с индуцированным |

IС= 1 мкА |

каналом: а - условное обозначение; б- |

структура; в - проходная характеристика |

|

UПОР > 0 |

UЗИ |

в

144

|

Исток |

Затвор(− ) |

Сток |

|

p+ |

|

p+ |

|

|

n-подложка |

|

а |

|

б |

|

UПОР<0 |

IС |

|

|

|

UЗИ |

|

|

|

Рис.8.2. р-МОП с индуцированным |

||

|

каналом: а - условное обозначение; |

||

|

б - структура; в - |

проходная |

|

в |

|

характеристика |

|

|

|

|

|

Так как при UЗИ = 0 IС = 0, то транзистор называется нормально-закрытым (НЗ).

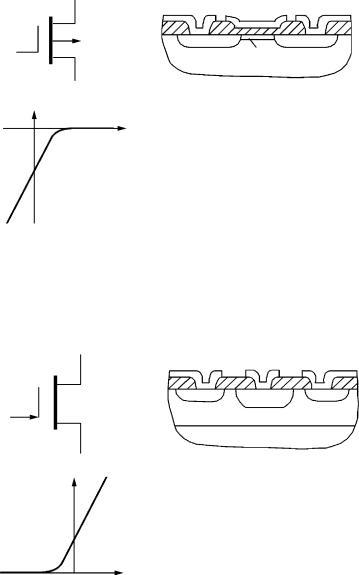

2. МОП-транзистор со встроенным каналом (рис.8.3 и 8.4).

|

|

Исток |

Затвор( ) |

Сток |

|

|

n+ |

n |

n+ |

|

|

|

|

|

|

|

|

p-подложка |

|

|

а |

|

б |

|

|

IС |

|

|

|

|

IС0 |

|

|

|

|

|

Рис.8.3. n-МОП со встроенным |

||

|

|

каналом: а - условное обозначение; |

||

UОТС < 0 |

UЗИ |

б - структура; в - |

проходная |

|

|

в |

характеристика |

|

|

|

|

|

|

|

145

|

Исток |

Затвор(+) |

Сток |

|

p+ |

p |

p+ |

|

|

|

|

|

|

n-подложка |

|

а |

|

б |

|

IС |

UОТС > 0 |

|

|

|

UЗИ |

|

|

IС0 |

Рис.8.4. р-МОП со встроенным |

||

|

|||

|

каналом: а - условное обозначение; |

||

|

б - структура; в - |

проходная |

|

в |

|

характеристика |

|

|

|

|

|

Напряжение UЗИ при токе стока IС = 1 мкА называется напряжением отсечки, т.е. напряжением, при котором закрывается транзистор.

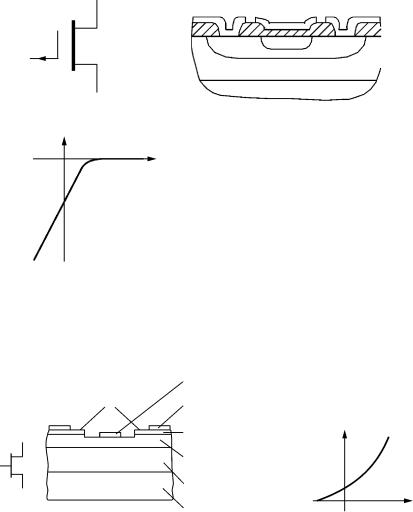

Так как при UЗИ = 0 IС = IС0, то транзистор называется нормально-открытым (НО), а IС0 называется током отсечки. 3. Полевой транзистор с p–n-переходом (рис.8.5 и 8.6). Это НО транзистор, у которого проводимость сток-исток модулируется

Исток |

Затвор(+) |

Сток |

n+ |

p |

n+ |

n-эпитаксиальный слой |

||

|

p-подложка |

|

а |

б |

|

IС

IС0

Рис.8.5. n-ПТ с p−n-переходом: а - условное обозначение; б - структура; в - проходная характеристика

UОТС < 0 |

UЗИ |

в

146

|

Исток |

Затвор |

Сток |

|

|

n+ |

p+ |

|

n-эпитаксиальный слой |

||

|

|

p-подложка |

|

а |

|

б |

|

IС |

UОТС > 0 |

|

|

|

UЗИ |

|

|

IС0 |

|

|

|

Рис.8.6. p-ПТ с p−n-переходом: а -

условное обозначение; б - структура; в - проходная характеристика

в

областью пространственного заряда с p–n-перехода.

4. ПТШ - полевой транзистор с затвором Шотки (рис.8.7).

Затворный контакт

Шотки (Ti,W)

|

|

n+ |

|

Омические контакты |

|

|

|

И |

З |

С |

(слои AuGe,Ni,Au,Pt) |

|

|

|

Контактный |

IC |

|

|||

|

|

|

|

|||

|

|

n |

|

|

||

|

|

|

n+-слой |

|

|

|

|

|

n− |

|

Активный |

|

|

|

|

|

|

слой |

IC0 |

|

|

|

i*-GaAs |

|

Буферный |

|

|

|

|

|

|

слой |

UОТС < 0 |

UЗИ |

а |

|

|

|

Полуизолирующая |

||

|

б |

|

подложка |

|

в |

|

|

|

|

|

|

||

Рис.8.7. ПТШ: а - условное обозначение; б - структура; в - проходная характеристика

147