- •1. Основы микросхемотехники ИС

- •1.1. Основные термины и определения

- •1.2. Этапы и направления развития ИС

- •1.3. Классификация ИС

- •1.3.4. Классификация по степени интеграции

- •1.4. Последовательность разработки ИС

- •2. Основы цифровой техники

- •2.3. Основные логические операции

- •2.4. Формы представления логической функции

- •2.5. Структурное проектирование цифровых схем комбинационного типа

- •3. Основные параметры и характеристики ЦИС

- •3.1. Основные параметры ЦИС

- •3.2. Характеристики ЦИС

- •3.3. Определение измеряемых параметров по характеристикам

- •4.1. Формирование биполярных транзисторов

- •4.3. Эквивалентная модель интегрального n–p–n биполярного транзистора

- •4.4. Режимы работы биполярного транзистора

- •4.6. Статические ВАХ транзистора

- •5. Диоды в интегральных схемах

- •5.1. Модель идеального диода

- •5.2. Эквивалентная схема интегрального диода

- •5.3. Аппроксимации ВАХ диода

- •5.4. Варианты реализации интегральных диодов

- •6. Пассивные элементы ИС

- •6.1. Основные параметры резисторов

- •6.2. Реализация интегральных резисторов

- •6.4. Реализация интегральных конденсаторов

- •7. Элементная база статических ЦИС на биполярных транзисторах

- •7.1. Резисторно-транзисторная логика (РТЛ)

- •7.1.1. Характеристики РТЛ

- •7.2. Эмиттерно-связанная логика (ЭСЛ)

- •7.2.1. Принцип работы

- •7.2.2. Входная характеристика

- •7.2.3. Передаточная характеристика

- •7.2.4. Выходная характеристика

- •7.2.6. Многоярусные ЭСЛ (МяЭСЛ)

- •7.3. Диодно-транзисторная логика

- •7.3.1. Расчет передаточной и входной характеристик

- •7.3.2. Выходная характеристика

- •7.3.3. Влияние нагрузки на логические уровни

- •7.4. Транзисторно-транзисторная логика

- •7.4.1. ТТЛ-элемент с простым инвертором

- •7.4.2. Передаточная характеристика

- •7.4.3. Входная характеристика

- •7.4.4. Выходная характеристика

- •7.4.6. Основные параметры

- •7.4.7. Многоэмиттерный транзистор

- •7.4.8. ТТЛ-элемент со сложным выходным каскадом

- •7.4.9. Модификация логического элемента

- •7.5. Интегральная инжекционная логика

- •7.5.2. Реализация логических функций

- •8. Полевые транзисторы

- •8.1. Типы полевых транзисторов

- •8.2. Определение физических параметров

- •8.3. модель полевого транзистора

- •8.4. Режимы работы и уравнения ВАХ полевого транзистора

- •9. Элементная база на полевых транзисторах

- •9.2. Передаточная характеристика и параметры инвертора с линейной нагрузкой

- •9.3. Передаточная характеристика и параметры инвертора с нелинейной нагрузкой

- •9.4. Передаточная характеристика и параметры инвертора с квазилинейной нагрузкой

- •9.5. Передаточная характеристика и параметры инвертора с токостабилизирующей нагрузкой

- •9.6. Передаточная характеристика и параметры комплементарного инвертора

- •9.8. Логические элементы на МОП-транзисторах

- •9.9. Определение эквивалентной крутизны группы переключающих транзисторов

- •9.11. Влияние параметров транзисторов на характеристики логического элемента

- •9.12. Сопряжение ТТЛ- и КМОП-схем

|

U |

|

æU |

ИП |

-U |

БЭН |

-U 0 |

|

P = |

|

ИП ç |

|

|

||||

|

2 |

ç |

|

|

R1 |

|

||

|

|

|

è |

|

|

|

|

|

|

|

|

ö |

+ |

UИП - 2UБЭН - UБКН ÷ |

||

|

|

. |

|

|

R1 |

||

|

|

÷ |

|

|

|

|

ø |

В качестве особенностей ТТЛ со сложным выходным каскадом следует отметить недопустимость соединения выходов нескольких схем. Поскольку, если соединить несколько схем, когда один выход имеет состояние U0, а другой состояние U1, то через последовательные элементы Т3, Д1 одной схемы и Т4 другой схемы потечет сквозной ток. При этом резко возрастет потребляемая мощность.

7.4.9. Модификация логического элемента

На рис.7.43 приведена схема ТТЛ-элемента, имеющего улучшенные характеристики и параметры. Введение дополнительных элементов позволило:

1)повысить помехоустойчивость, так как диоды D1 и D2, подключенные ко входам логического элемента, защищают схему от воздействия отрицательной импульсной помехи;

2)повысить нагрузочную способность и уменьшить время переключения из 0 в 1, поскольку составной транзистор в сложном выходном каскаде, реализованный на Т3 и Т5, включенных по схеме Дарлинг-

тона, имеет высокий коэффициент усиления по току; повысить быстродействие за счет использования цепи нелиней-

ной коррекции, состоящей из резисторов R3, R5 и транзистора Т4

и

ограничивающей степень насыщения транзистора Т6. Когда на входах логического элемента 1, то при включении транзистора Т2 его эмиттерный ток втекает в базу транзистора Т6, который быстро открывается. Затем открывается транзистор Т4 и шунтирует

136

низкоомным сопротивлением R5 эмиттерный переход Т6. При выключении Т6 избыточный заряд

|

|

|

|

UИП |

|

|

R2 |

|

R6 |

|

|

R1 |

T3 |

|

|

|

|

|

|

UВХ1 |

|

T1 |

|

T5 |

|

R4 |

|

||

|

T2 |

UВЫХ |

||

UВХ2 |

|

|

||

|

|

|

T6 |

|

Д1 |

Д2 |

|

|

|

R3 |

R5 |

|

||

|

|

|

||

|

|

|

T4 |

|

Рис.7.43. Схема ТТЛ-элемента с улучшенными параметрами

3)неосновных носителей удаляется из базовой области возросшим током Т4.

Быстродействие ТТЛ-элемента определяется инерционными свойствами биполярного транзистора, работающего в режиме насыщения. При выключении такого транзистора требуется дополнительное время, называемое временем удержания, для рассасывания заряда неосновных носителей, накопленного в базе.

Д |

|

T |

T |

а |

б |

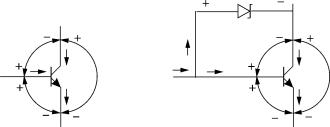

Рис.7.44. Транзистор Шотки: а - схема; б - условное обозначение

137

Время удержания можно исключить, обеспечив условие, при котором транзистор, работающий в нормальном активном режиме, не попадает в режим насыщения. В современных ТТЛ это достигается включением диода Шотки. Транзисторы с диодами Шотки, расположенными между базой и коллектором (рис.7.44,а), не попадают в область насыщения и называются транзисторами с фиксирующими диодами Шотки, или транзисторами Шотки (рис.7.44,б). Падение напряжения на диоде Шотки в прямом направлении меньше, чем на обычном, и составляет 0,25 В против

0,6 В.

|

|

UД = 0,25 В |

|

|

|

|

Д |

|

|

UБК = 0,4 В |

IК |

UБК = 0,25 В |

IК |

|

IБ |

||||

IБ |

||||

|

T UКЭ = 0,2 В |

|

T UКЭ = 0,35 В |

|

UБЭ = 0,6 В |

IЭ |

UБЭ = 0,6 В |

IЭ |

|

|

|

|||

|

а |

б |

|

Рис.7.45. Работа транзистора при больших базовых токах: а – обычный транзистор в РН; б – транзистор с диодом Шотки, предотвращающим насыщение

У обычного транзистора напряжение между базой и коллектором в режиме насыщения равно 0,4 В (рис.7.45,а). В транзисторе Шотки благодаря применению диода Шотки ток базы разветвляется, и часть его отводится в коллектор прежде чем транзистор попадает в режим насыщения (рис.7.45,б). На рис.7.46 приведена схема ТТЛ-элемента с использованием диода Шотки.

138