- •1. Основы микросхемотехники ИС

- •1.1. Основные термины и определения

- •1.2. Этапы и направления развития ИС

- •1.3. Классификация ИС

- •1.3.4. Классификация по степени интеграции

- •1.4. Последовательность разработки ИС

- •2. Основы цифровой техники

- •2.3. Основные логические операции

- •2.4. Формы представления логической функции

- •2.5. Структурное проектирование цифровых схем комбинационного типа

- •3. Основные параметры и характеристики ЦИС

- •3.1. Основные параметры ЦИС

- •3.2. Характеристики ЦИС

- •3.3. Определение измеряемых параметров по характеристикам

- •4.1. Формирование биполярных транзисторов

- •4.3. Эквивалентная модель интегрального n–p–n биполярного транзистора

- •4.4. Режимы работы биполярного транзистора

- •4.6. Статические ВАХ транзистора

- •5. Диоды в интегральных схемах

- •5.1. Модель идеального диода

- •5.2. Эквивалентная схема интегрального диода

- •5.3. Аппроксимации ВАХ диода

- •5.4. Варианты реализации интегральных диодов

- •6. Пассивные элементы ИС

- •6.1. Основные параметры резисторов

- •6.2. Реализация интегральных резисторов

- •6.4. Реализация интегральных конденсаторов

- •7. Элементная база статических ЦИС на биполярных транзисторах

- •7.1. Резисторно-транзисторная логика (РТЛ)

- •7.1.1. Характеристики РТЛ

- •7.2. Эмиттерно-связанная логика (ЭСЛ)

- •7.2.1. Принцип работы

- •7.2.2. Входная характеристика

- •7.2.3. Передаточная характеристика

- •7.2.4. Выходная характеристика

- •7.2.6. Многоярусные ЭСЛ (МяЭСЛ)

- •7.3. Диодно-транзисторная логика

- •7.3.1. Расчет передаточной и входной характеристик

- •7.3.2. Выходная характеристика

- •7.3.3. Влияние нагрузки на логические уровни

- •7.4. Транзисторно-транзисторная логика

- •7.4.1. ТТЛ-элемент с простым инвертором

- •7.4.2. Передаточная характеристика

- •7.4.3. Входная характеристика

- •7.4.4. Выходная характеристика

- •7.4.6. Основные параметры

- •7.4.7. Многоэмиттерный транзистор

- •7.4.8. ТТЛ-элемент со сложным выходным каскадом

- •7.4.9. Модификация логического элемента

- •7.5. Интегральная инжекционная логика

- •7.5.2. Реализация логических функций

- •8. Полевые транзисторы

- •8.1. Типы полевых транзисторов

- •8.2. Определение физических параметров

- •8.3. модель полевого транзистора

- •8.4. Режимы работы и уравнения ВАХ полевого транзистора

- •9. Элементная база на полевых транзисторах

- •9.2. Передаточная характеристика и параметры инвертора с линейной нагрузкой

- •9.3. Передаточная характеристика и параметры инвертора с нелинейной нагрузкой

- •9.4. Передаточная характеристика и параметры инвертора с квазилинейной нагрузкой

- •9.5. Передаточная характеристика и параметры инвертора с токостабилизирующей нагрузкой

- •9.6. Передаточная характеристика и параметры комплементарного инвертора

- •9.8. Логические элементы на МОП-транзисторах

- •9.9. Определение эквивалентной крутизны группы переключающих транзисторов

- •9.11. Влияние параметров транзисторов на характеристики логического элемента

- •9.12. Сопряжение ТТЛ- и КМОП-схем

A |

ЭСЛ |

F1 |

F1 |

B |

|

|

|

|

|

F |

|

|

|

|

|

C |

ЭСЛ |

F2 |

F2 |

D |

|

F |

|

|

|

||

|

|

|

−UИП

Рис.7.23. Расширение функциональных возможностей ЭСЛэлемента при объединении выходов

Отметим, что:

1)максимальное количество ярусов при стандартном питании ограничивается тремя;

2)для обеспечения НАР работы транзисторов требуются формирователи опорных напряжений UОП2, UОП1 и

входных логических сигналов U A0 , U 1A , U B0 , U1B ;

3)для повышения стабильности логического уровня единицы используется отрицательное питание.

7.3. Диодно-транзисторная логика

Достоинства:

1)простая схемотехника;

2)простая технология (n–p–n-транзисторы, диоды и резисторы);

3)простая топология.

Недостатки:

1)узкая зона помехоустойчивости;

2)высокая потребляемая мощность;

3)низкая нагрузочная способность;

4)среднее быстродействие.

114

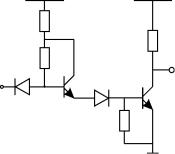

На рис.7.24 и 7.25 приведены условное обозначение и электрическая схема ДТЛ-элемента.

A &

F=AB И-НЕ

B

Рис.7.24. Условное обозначение ДТЛ-элемента

UИП1 UИП2

R1

|

R2 |

R4 |

|

|

UВЫХ |

||

|

Д1 |

||

UВХ1 |

T1 Д3 |

||

|

|||

|

T2 |

||

UВХ2 |

|

||

Д2 |

R3 |

||

|

|||

|

|

Рис.7.25. Электрическая схема ДТЛ-элемента 2И-НЕ

Табл.7.5 является таблицей истинности ДТЛ-элемента, выполняющего логическую функцию И-НЕ.

|

|

|

|

|

|

|

|

|

Таблица 7.5 |

|

|

|

Таблица истинности ДТЛ-элемента |

||||||

UВХ1 |

|

UВХ2 |

|

|

|

UВЫХ |

|

Примечания |

|

0 |

|

|

0 |

|

|

|

1 |

|

Д1, Д2 открыты |

0 |

|

|

1 |

|

|

|

1 |

|

Д1 открыт, Д2 закрыт |

1 |

|

|

0 |

|

|

|

1 |

|

Д1 закрыт, Д2 открыт |

1 |

|

|

1 |

|

|

|

0 |

|

Д1, Д2 закрыты |

1. При |

U |

ВХ1 |

= U 0 |

U |

ВХ2 |

= U1 |

(Д1 открыт, Д2 закрыт) |

||

|

|

|

|

|

|||||

115

Т1 в НАР ( IЭТ1 = 0 ); Т2 - в РО;

UВЫХ = UИП2 = U1 (без нагрузки).

2. ПриU ВХ1 = U ВХ2 = U 1 (Д1, Д2 закрыты) Т1 в НАР; Т2 в РН;

UВЫХ = UКЭН = U0 (без нагрузки).

Если хотя бы на одном входе задан U0, соответствующий входной

диод открыт (Д1, Д2); T1 работает в НАР с IЭТ1 = 0, Т2 в РО и на выходе U1.

Только, когда на всех входах задан U1, входные диоды Д1, Д2 закрыты, T1 работает в НАР, а Т2 в РН и на выходе U0.

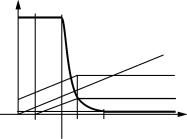

7.3.1. Расчет передаточной и входной характеристик

Рассмотрим одновходовую схему ДТЛ-элемента (рис.7.26).

UИП1 |

UИП2 |

|

R1 |

|

|

R2 |

R4 |

|

UВЫХ |

||

Д1 |

T1 Д3 |

|

UВХ1 |

||

T2 |

||

|

R3 |

Рис.7.26. Одновходовая электрическая схема ДТЛ-элемента

1. На участке AВ 0 < UВХ < UВХГР1 .

Ток протекает только через R1, R2 и Д1,

116

Д1 открыт → UБТ1 |

=UВХ + UД1Н , |

|

|

||||||

так как |

UБ |

Т1 |

< UД3 |

ГР |

+ UБЭ1 |

|

|

||

|

|

|

ГР , то T1 работает в НАР с IЭ |

||||||

= 0, Д3 открыт с IД = 0, Т2 работает в РО (UБ ЭТ 2 = U R3 = 0) . То- |

|||||||||

гда |

|

|

|

|

|

|

|

|

|

UВЫХ = UИП2 − IКТ 2 R4 = UИП2 (так |

как |

IКT 2 = 0 ) |

|||||||

(рис.7.27), |

|

|

|

UИП1 − UД1Н − UВХ |

|

|

|

||

|

I |

ВХ = |

|

|

|||||

|

|

|

R1 + R2 |

(рис.7.28). |

|

||||

|

|

|

|

|

|

|

|||

Граничное условие перехода на следующий участок определяется моментом, когда ток потечет через транзистор Т1, диод Д3 и резистор R3:

UВХГР1 = UД3ГР + UБЭ1ГР − UД1Н .

2. На участке ВС при UВХГР1 |

< UВХ < UВХГР2 ток протекает от |

||

UИП1 через R1, R2: одна часть тока через Д1, другая - через T1, Д3, |

|||

R3. |

|

|

|

Тогда Д1 открыт, Т1 в НАР, Д3 открыт, Т2 в НАР с IЭ = 0. |

|||

С увеличением UВХ растет UR3 |

(0 <U R3 <UБЭT2 ) . При этом |

||

UВЫХ = UИП2 (см. рис.7.27), |

|

||

UВЫХ |

|

|

|

U 1 =UИП A |

В С |

|

|

|

|

UВЫХ = UВХ |

|

|

UБ1 |

|

3UБЭН |

UБЭН |

|

UБЭН |

|

UБ2 |

D |

||

U 0=UКЭН |

|

E |

F |

UВХГР1 |

UВХГР3 UВХГР4 |

UВХ |

|

UВХГР2

Рис.7.27. Передаточная характеристика ДТЛ-элемента

117

|

|

|

|

|

|

|

IВХ = IR1 − IR3 ≈ |

|

|

|||||

≈ |

U |

ИП1 |

− U |

Д Н |

− U |

ВХ |

− |

UВХ + UД1 |

− UБЭ1 |

− UД3 |

|

|||

|

|

|

|

|

Н |

|

|

(см. рис.7.28) |

||||||

|

|

R1 + R2 |

|

|

|

|

|

R3 |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

IВХ |

|

|

|

|

|

UВХГР3 |

|

|

|

|

||

|

|

1 |

|

|

|

|

|

|

E |

F UВХ |

|

|||

|

I |

U0 UВХ |

|

UВХ |

|

|

UВХ |

U1 |

|

|

||||

|

|

|

|

ГР1 |

|

|

ГР2 |

ГР4 |

|

|

|

|||

D

I0 С

АВ

Рис.7.28. Входная характеристика ДТЛ-элемента Граничное условие перехода на следующий участок определяется

моментом открывания транзистора Т2, т.е. UБЭТ 2 = UБЭГР . Тогда

UВХГР 2 = UБЭ 2ГР + UД3Н + UБЭ1Н − UД1Н ~ UБЭГР + UБЭН .

3. На участке СD при UВХГР 2 < UВХ < UВХГР3 ток протекает от UИП1 через R1, R2: одна часть тока течет через Д1, другая - через T1, Д3, далее часть тока течет через R3 и часть - через Т2.

Тогда Д1 открыт, Т1 в НАР, Д3 открыт, Т2 в НАР.

UВЫХ = UИП2 – IК2R4 (см. рис.7.27),

IВХ = I R1 − IR3 − (1− αN )IЭТ 2 (см. рис.7.28).

118